Makefile中支持程序设计语言中变量的概率,但没有变量类型,只代表文本数据;

变量命名规则:变量可以包含字符、数字、下划线,单不能包含”:”,”#”, “=”,” ”,变量名大小写敏感。

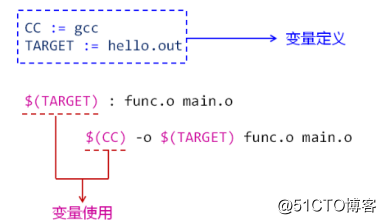

变量的定义和使用:

Makefile中有4中变量赋值方式:

程序设计语言中的通用赋值方式,只针对当前语句有效,等价于C语言中的赋值。建议无特殊要求时使用简单赋值。

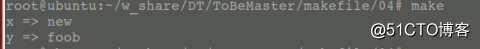

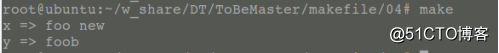

x := foo

y := $(x)b

x := new

test :

@echo "x => $(x)"

@echo "y => $(y)"输出结果:

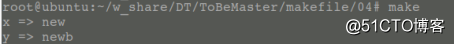

赋值操作可能影响多个其它变量,所有与目标变量相关的其他变量都会受到影响。

x = foo

y = $(x)b

x = new

test :

@echo "x => $(x)"

@echo "y => $(y)"输出结果:

注意:如果不是必要请尽可能不要使用递归赋值,这里的赋值号完全不等价与C语言中的赋值号。

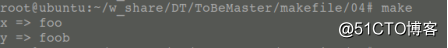

如果变量未定义,使用赋值符号中的值定义变量,如果已经定义,赋值无效。

x := foo

y := $(x)b

x ?= new

test :

@echo "x => $(x)"

@echo "y => $(y)"输出结果:

原变量值后加一个新值,原变量与新值之间由空格隔开

x := foo

y := $(x)b

x += new

test :

@echo "x => $(x)"

@echo "y => $(y)"输出结果:

在Makefile中存在一些预定义的变量,主要分为两类:自动变量和特殊变量。

$@ 当前规则中触发命令被执行的目标

$^ 当前规则中的所有依赖

$< 当前规则中的第一个依赖

自动变量的使用:

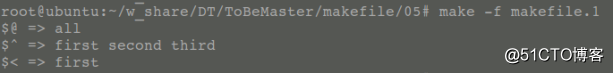

.PHONY : all first second third

all : first second third

@echo "\$$@ => $@"

@echo "$$^ => $^"

@echo "$$< => $<"

firtst:

second:

third:输出结果:

注意:

1.“$”符号在Makefile中有特殊含义,当打印其字面量时需要加上$进行转义

2.“$@”则需要加上\$进行转义

$(MAKE) 当前make解释器的文件名

$(MAKECMDGOALS) 命令行中指定的目标名,(make的命令行参数)

$(MAKEFILE_LIST) make需要要处理的makefile文件列表,注意当前Makefile的文件名总是位于列表最后,文件名之间使用空格分隔。

$(MAKE_VERSION) 当前make解释器的版本

$(CURDIR) 当前make解释器的工作目标

$(.VARIABLES) 所有已经定义的变量名和列表(预定义变量和自定义变量)

$(RM) rm -f

通常我们会打印$(.VARIABLES) 查看当前操作系统所支持的自定变量,然后对照make 手册(可从官网下载:http://www.gnu.org/software/make/manual/make.html),查看每个变量的意义。

.PHONY : all out first second third test

all out :

@echo "$(MAKE)"

@echo "$(MAKECMDGOALS)"

@echo "$(MAKEFILE_LIST)"

first :

@echo "first"

second :

@echo "second"

third :

@echo "third"

test :

@$(MAKE) first

@$(MAKE) second

@$(MAKE) third输出结果:

使用指定字符串替换变量中的后缀:

语法规则: $(var:cc=o)或 ${src1:cc=o}

替换表达式中不能有任何的空格,make中支持使用${}对变量进行取值

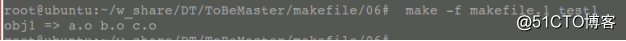

src1 := a.cc b.cc c.cc

obj1 := $(src1:cc=o)

test1 :

@echo "obj1 => $(obj1)"输出结果:

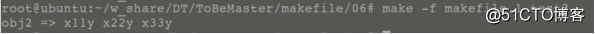

变量的模式替换,使用%保留变量值中的指定字符,替换其他字符

语法格式:$(var:a%b=x%y)或 ${src1:a%b=x%y}

src2 := a11b.c a22b.c a33b.c

obj2 := $(src2:a%b.c=x%y)

test2 :

@echo "obj2 => $(obj2)"输出结果:

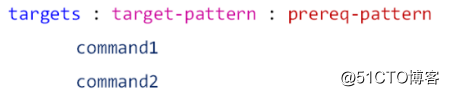

意义:

通过target-patten从targets中匹配子目标;再通过prereq-patten从子目标生成依赖;进而构成完成的规则。

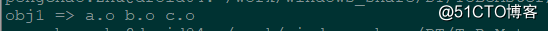

src1 := a.cc b.cc c.cc

obj1 := $(src1:cc=o)

test1 :

@echo "obj1 => $(obj1)"

src2 := a11b.c a22b.c a33b.c

obj2 := $(src2:a%b.c=x%y)

test2 :

@echo "obj2 => $(obj2)"输出结果:

一个变量名之中可以包含对其他变量的引用,本质上是使用一个变量表示另一个变量。

运行make时,可以在命令行中定义变量,命令行变量默认覆盖Makefile中定义的变量。

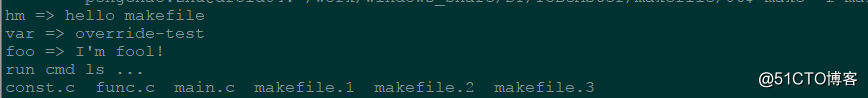

用于指示Makefile中定义的变量不能被覆盖,变量的定义和赋值都需要使用override关键字

用于定义Makefile中的多行变量,多行变量的定义从变量名开始到endef结束,可以使用override关键字防止变量被覆盖,define定义的变量等价于使用=定义的变量。

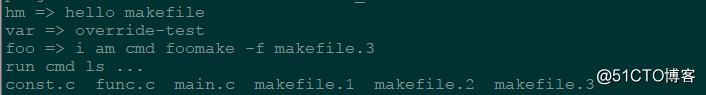

hm := hello makefile

override var := override-test

define foo

I‘m fool!

endef

override define cmd

@echo "run cmd ls ..."

@ls

endef

test :

@echo "hm => $(hm)"

@echo "var => $(var)"

@echo "foo => $(foo)"

${cmd}直接运行makefile的结果:

命令行传参的结果:

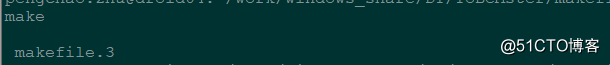

make makefile foo="i am cmd foomake -f makefile.3" var="cmd line var"

显然我们改变了foo变量的值,因为foo变量没有被override修饰,但不能改变var变量的值。

Makefile中能够使用环境变量的值,如果定义的普通变量和环境变量同名,环境变量将被覆盖,运行make时指定-e选项,优先使用环境变量

优势:环境变量可以在所有文件中使用;

劣势:过多的环境变量会导致移植性降低

变量在不同Makefile之间传递的方式:

1.直接在外部定义环境变量进行传递

2.使用export定义变量进行传递(定义临时环境变量)

3.使用make命令行变量进行传递(推荐)

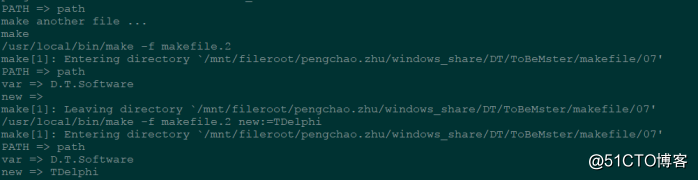

PATH := path

export var := D.T.Software

new := TDelphi

test :

@echo "PATH => $(PATH)"

@echo "make another file ..."

@$(MAKE) -f makefile.2

@$(MAKE) -f makefile.2 new:=$(new)makefile.2的内容:

test:

@echo "PATH => $(PATH)" #1.直接在外部定义环境变量进行传递

@echo "var => $(var)" #2.使用export定义变量进行传递(定义临时环境变量)

@echo "new => $(new)" #3.使用make命令行变量进行传递(推荐)输出结果:

作用域只在指定目标及连带规则中。

target : name <assignment> value

target : voerride name <assignment > value

模式变量是目标变量的扩展,作用域只在符合的目标及连带规则中。

pattrn : name <assignment > value

pattrn : voerride name <assignment > value

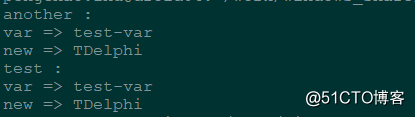

var := D.T.Software

new := TDelphi

test : var := test-var # 目标变量

%e : override new := test-new # 模式变量

test : another

@echo "test :"

@echo "var => $(var)"

@echo "new => $(new)"

another :

@echo "another :"

@echo "var => $(var)"

@echo "new => $(new)"

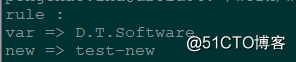

rule :

@echo "rule :"

@echo "var => $(var)"

@echo "new => $(new)"直接运行结果:

make rule运行结果:

原文地址:http://blog.51cto.com/11134889/2108156