标签:inf log alt 设计 style 编译 探讨 ril 没有

在使用Verilog进行设计过程中,经常会遇到某些条件判断语句中的分支没有执行,有些for循环仅执行一次的情况,特别是在过程性赋值语句中。其中很大一部分是因为错误使用了“;”导致的。因为Verilog源自C语言,根据其语言特性,“;”在Verilog中本身是一条单独的空语句,只是岂不进行任何具体操作而已,但是这样的特点造成了“;”可以出现在设计的很多地方,顺利的通过编译甚至仿真,引起不容易察觉的错误。本文将针对这种情况探讨其中原因,并以示例说明。

1 条件判断

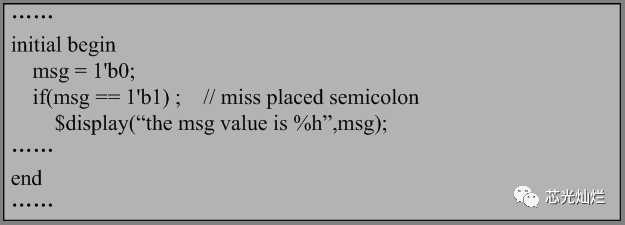

在条件判断语句中,如果将“;”放置在条件判断语句之后,那么有可能导致不期望的结果,如下例期望条件为真时输出对应的消息:

上例仿真后,虽然msg条件不成立,但是其后的显示语句还是被执行了,与预期要求不符。主要原因是条件判断后紧跟的“;”,那么当该条件成立时,执行的是条件判断后的“;”对应的空语句。而$display此时已经不是条件判断语句为真时对应的语句,所以导致显示结果在条件为假时显示,与期望结果不一致。

2 循环控制

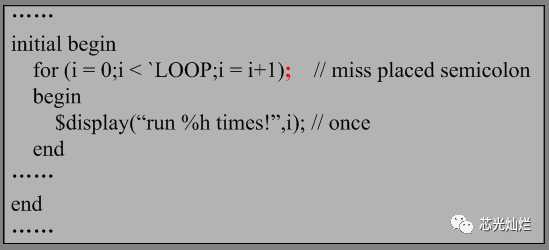

在循环控制语句中,如果将“;”放置在循环控制条件判断语句后,那么可能会导致不期望的结果,如下例期望条件成立时多次输出对应的消息:

上例仿真后,发现显示的消息仅出现了一次,与期望出现多次不相符。主要原因是for循环后紧跟";",提前结束了for循环,即每当for循环执行一次其后的“;”都会执行一次,不会按照期望的执行后续的“begin-end”中的语句。从而导致了仿真时期望的消息仅仅输出一次的现象。

3 解决方法

Verilog中的";"特点主要源自C语言,因为C语言中认为这样的“;”语法是正确的,是一条空语句。为了避免类似情况在其他语句中出现,可以通过以下方法防范:

如果确需执行类型空语句,使用“begin-end”结构,即将空语句置于“begin-end”中;

必须理解Verilog中相关语句的语法,不要错误使用相关的操作符;

标签:inf log alt 设计 style 编译 探讨 ril 没有

原文地址:https://www.cnblogs.com/xgcl-wei/p/8969990.html