标签:注意 test 原理 center text 对话框 增加 eve 资讯

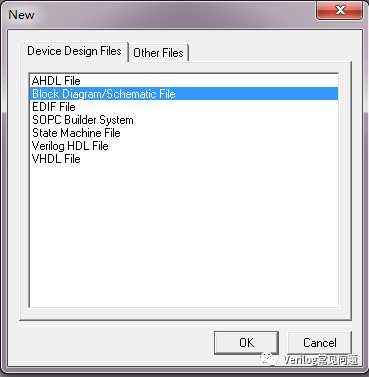

1.新建一个工程,创建一个原理图文件,并在其中进行原理图电路绘制,本例以一个2输入与门为例,如下图所示:

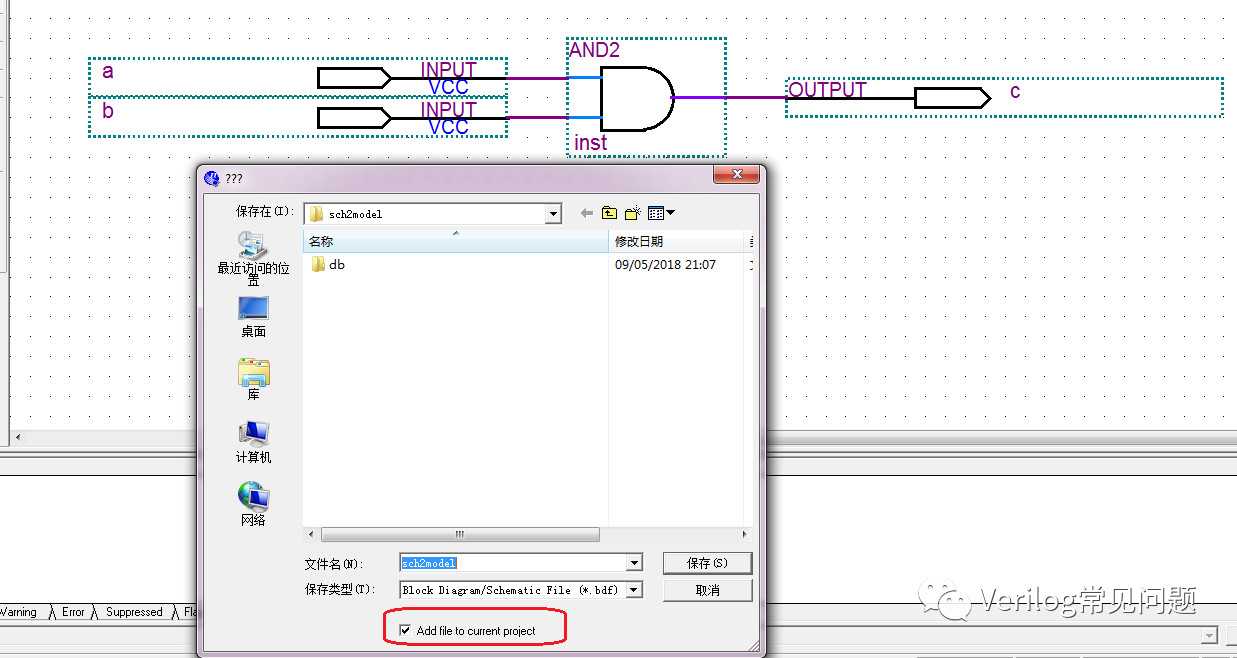

绘制好电路图后,保存绘制好的电路至新建的工程,如下图所示:

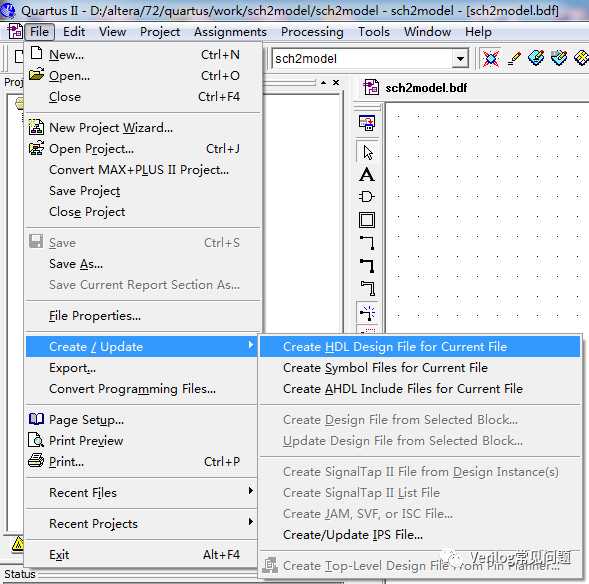

因为原理图文件ModelSim等第三方仿真器并不识别,所以需要将其输出为Veilog或者VHDL文件,操作如下:

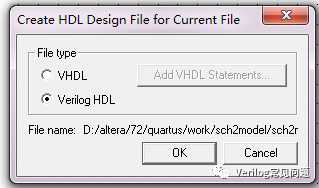

点击当前选项后弹出如下对话框,选择要生成的对应的硬件描述语言文件,点击OK按钮完成对应文件的生成(生成文件的路径为当前项目文件夹下),本文中以Verilog为例:

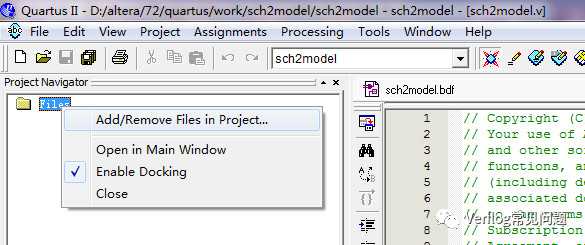

确认文件生成后,在工程中单击原理图文件,将其从当前工程中移除后,右击"Files"如下图所示:

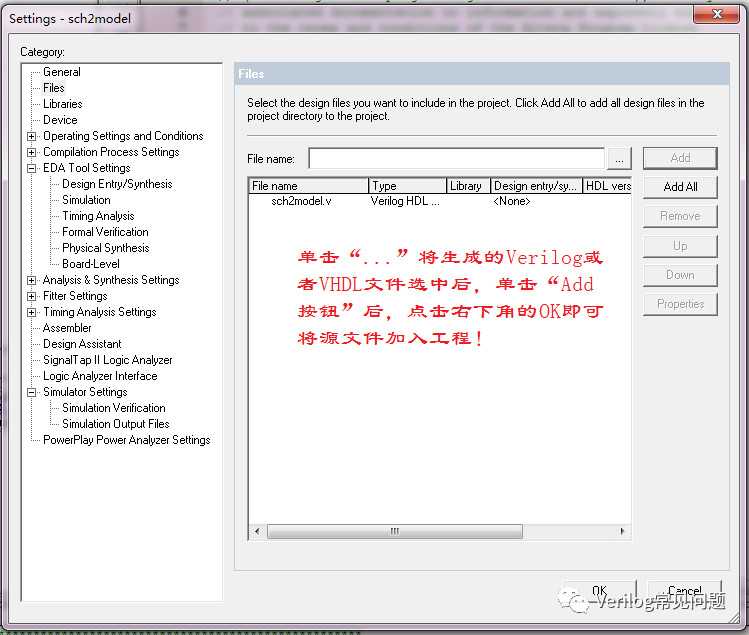

点击选项后,在弹出的对话框中增加生成的源文件,如下图所示:

通过上述步骤,即可将源文件加入到工程中.

2 选择"Processing"中的"Start Compilation"完成对项目的编译。

3 参考“Quartus II 调用ModelSim仿真调试”中的步骤,即可完成对应的ModelSim调用仿真。

4 如果想使用Quartus中的波形文件作为调用ModelSim的仿真激励,那么只需要注意以下事项:

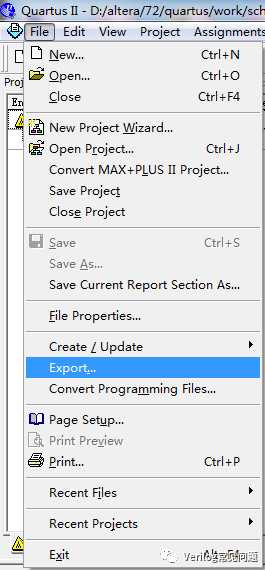

使用波形文件完成仿真后,生成的波形文件本身是不能为第三方仿真工具识别,同样需要将其输出为Verilog或者VHDL等格式,如下图所示:

单击“Export...”在弹出的对话框中保存生成的testbench,此时的testbench中即包含了波形仿真时的激励,但是这个testbench的文件后缀为“*.vt”。

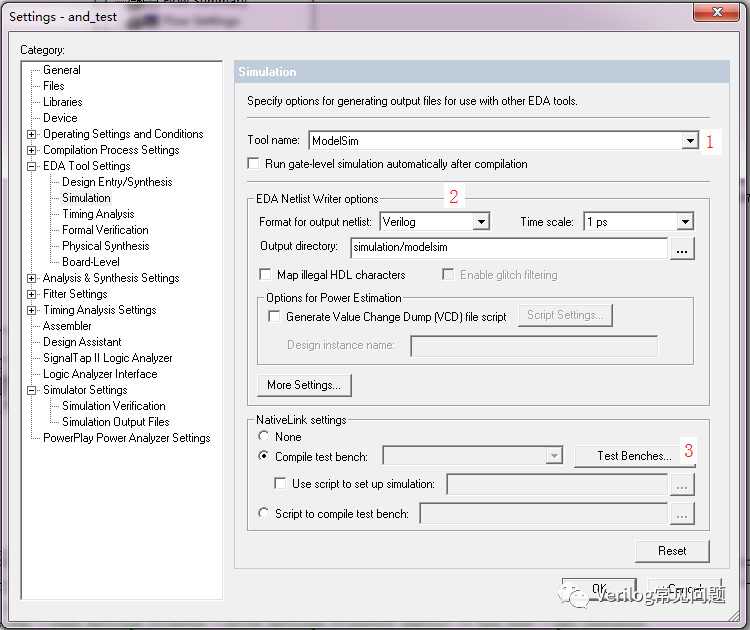

选择菜单栏下的Assignments->Settings,在弹出的界面中选择EDA Tool Settings->Simulation,设置如下图所示:

其中“3”指定到生成的testbench即可。

最后,如果确实不想将原理图转换为Verilog或者VHDL进行仿真,即不想将原理图文件从项目中移除,那么可以只生成功能仿真网表进行仿真,在指定好testbench后,选择"Tools"->"EDASimulation Tool"->"Run EDA Gate Level Simulation"进行仿真。

更多资讯,请关注下方二维码!

Quartus系列:Quartus II 原理图调用ModelSim进行仿真

标签:注意 test 原理 center text 对话框 增加 eve 资讯

原文地址:https://www.cnblogs.com/xgcl-wei/p/9021659.html