标签:uart doc round ilo mic nbsp 直接 intel col

###### 【该随笔部分内容转载自小梅哥】 #########

工具使用 -> 语法学习 -> 逻辑设计 -> IP使用 ->接口设计 -> 时序分析 -> 片上系统

1、工具使用

Altera:Quartus II

Xlinx: Vivado

2、语法学习

Verilog HDL(FPGA设计的是电路)

3、 逻辑设计

组合逻辑:多路选择器、加法器、译码器、乘法器 ·······

时序逻辑:计数器、分频器、移位寄存器、定时器 ·······

接口逻辑:UART,CAN,SPI,LVDS ······

状态机,线性序列机

4、IP使用

计数器、IO、FFT、各种软核CPU(MC8051)·······

5、接口设计

Avalon ST、Avalon MM、FSMC和FPGA

6、时序分析

时序分析和时序约束

7、片上系统

SOPC: 使用FPGA通用逻辑搭建CPU和外围设备电路

Intel: NIOS II 软核CPU,ARM CortexA9硬核

Xilinx: MicroBlaze软核CPU,PowerPC硬核,硬核ARM CortexA9

MCS8051、开源软核CPU、CortexM0

1、设计定义

2、设计输入(verilog、原理图)

3、分析和综合

4、功能仿真(modelsim)

5、布局布线

6、时序仿真

7、IO分配及配置文件的生成

8、配置(烧写FPGA)

9、在线调试

1、Quartus II

2、Vivado

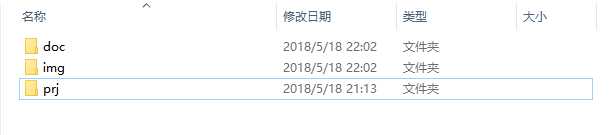

使用Vivado软件比较方便,直接指定存放工程目录就可以,源文件和测试文件会自动分类存放在子文件夹下:

标签:uart doc round ilo mic nbsp 直接 intel col

原文地址:https://www.cnblogs.com/Mculover666/p/9060566.html