本文说明的是单纯的一般的计算指令从储存设备中取出来之后,运行时(取址,译码,执行,回写 -- 这些操作)在CPU和我们的主存之间的执行过程

以下,我们使用一条简单的指令进行引入,后续再添加其他的情况:

ADD R0,[6] //将主存地址为6的内容取出和寄存器R0的内容相加,并回写入R0中

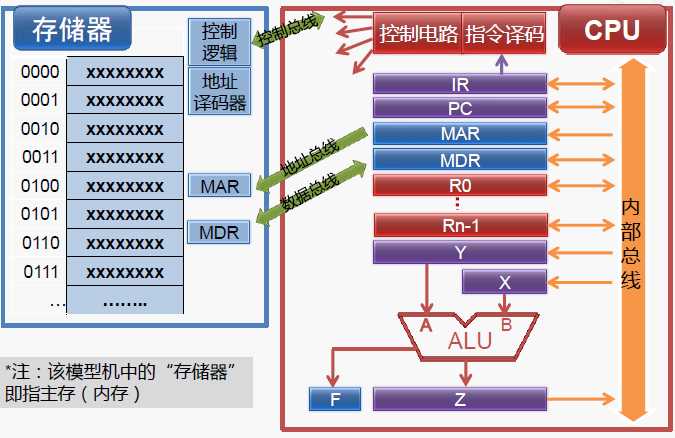

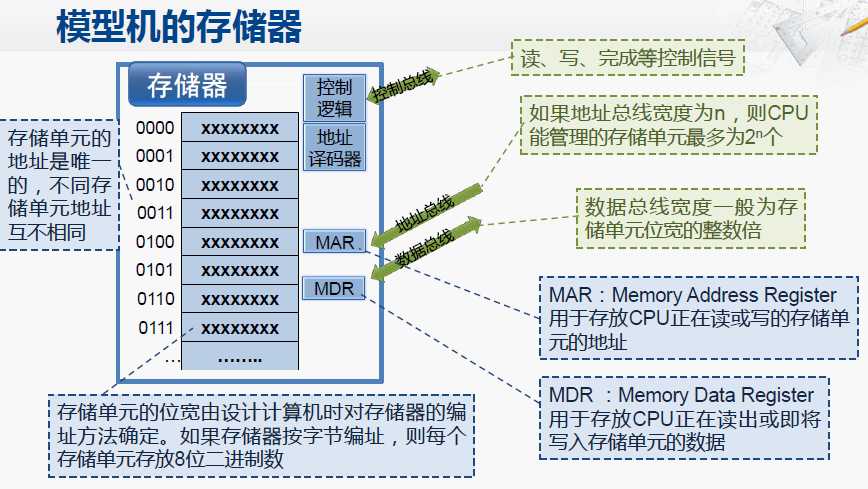

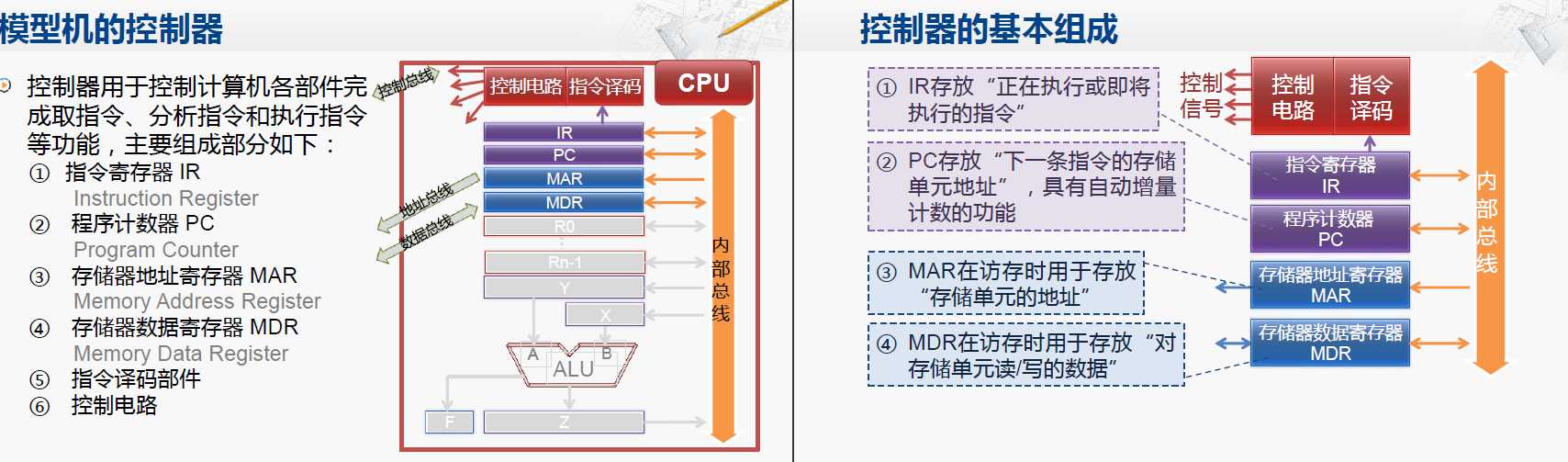

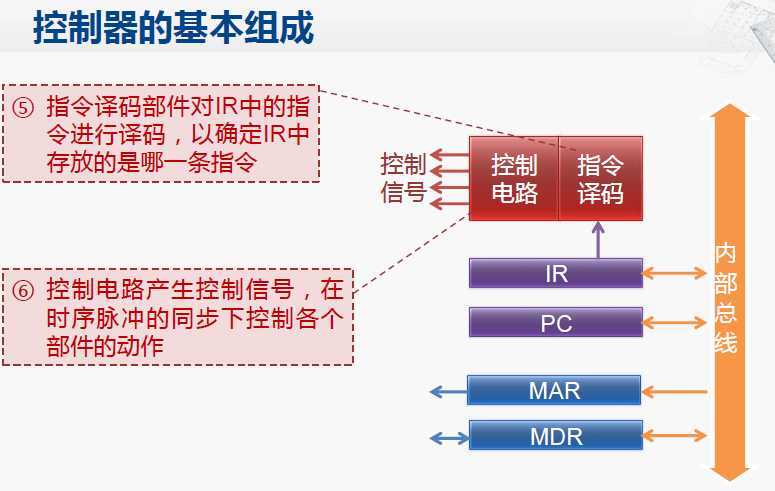

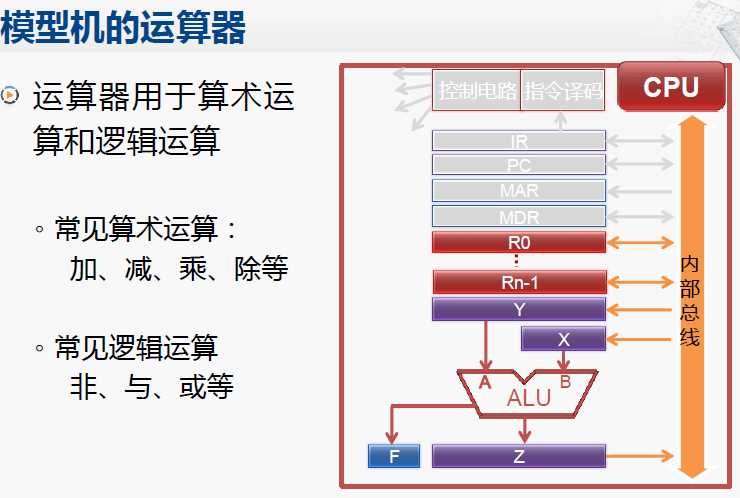

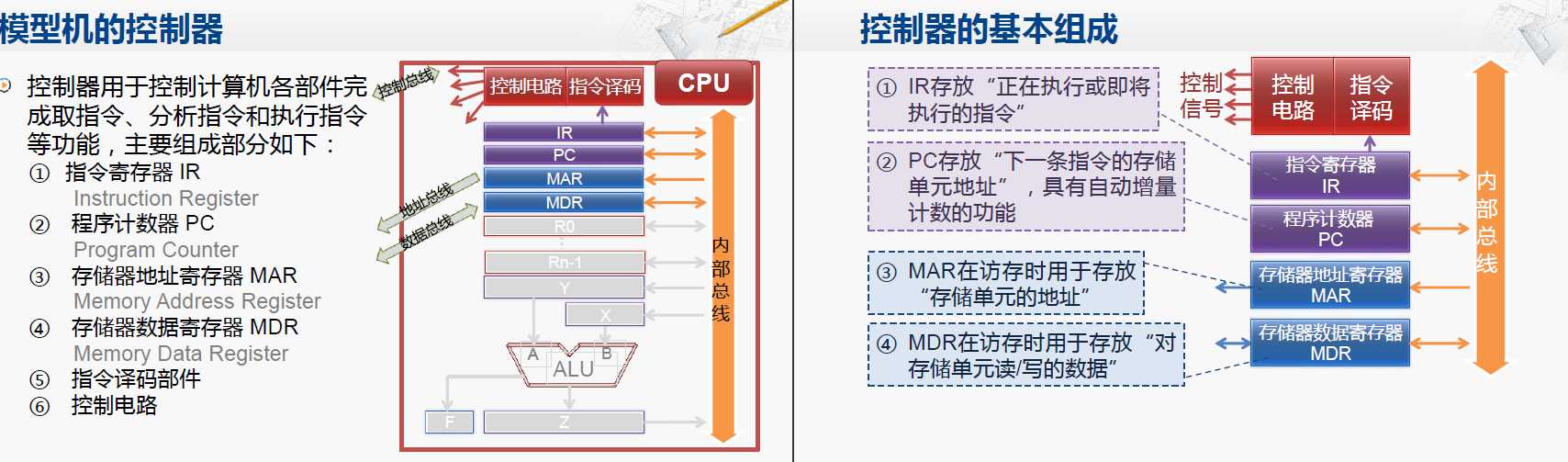

为了更加明确的了解后续的执行过程先普及一下基本的计算机结构(一个简单的模型机):

模型机的结构

主存的结构(模型机)

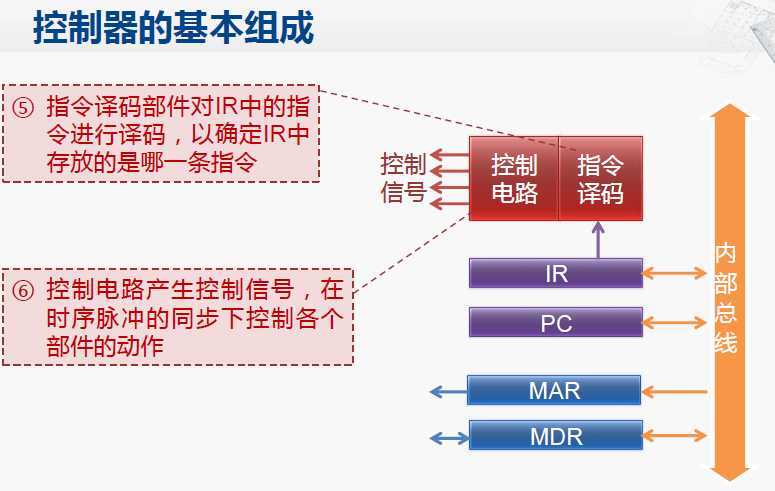

CPU的控制器(CC)结构

CPU的运算器(CA)结构

好的,现在可以进入正题了,tips: 上面的都是说的模型机的结构,不代表现在的硬件的真实的结构

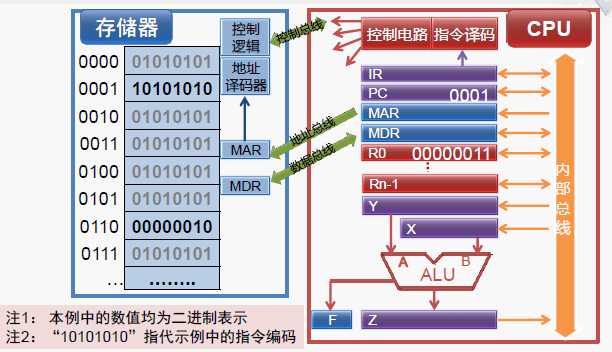

下面这个图是就是执行的环境

通过上面的图,我们可以看出:R0中储存的是数值3,PC中储存的内容是0001

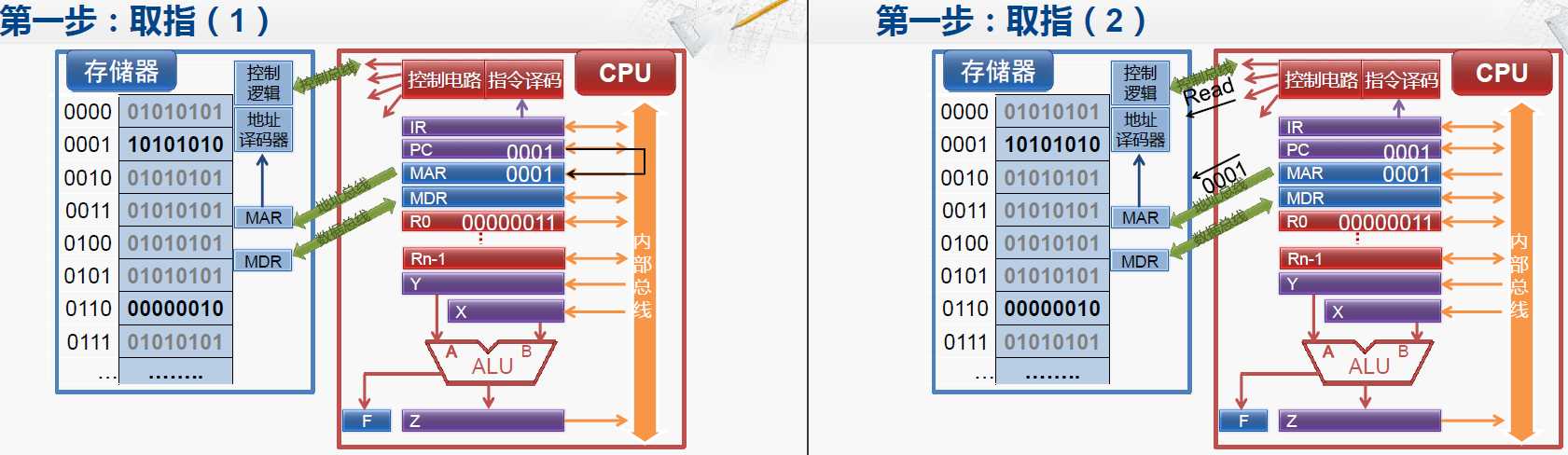

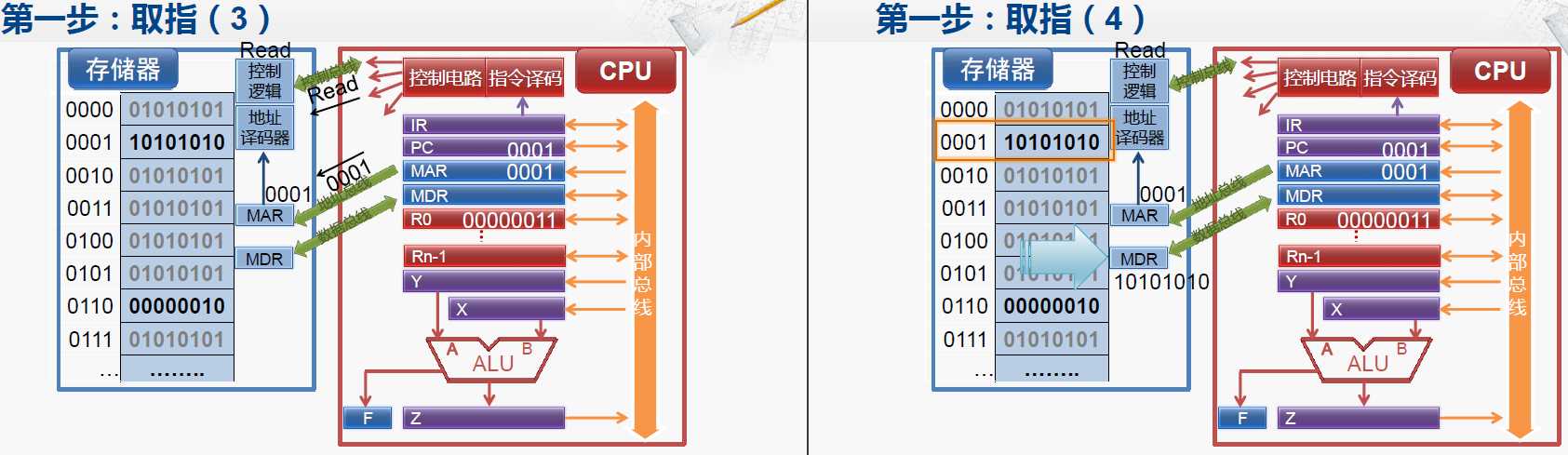

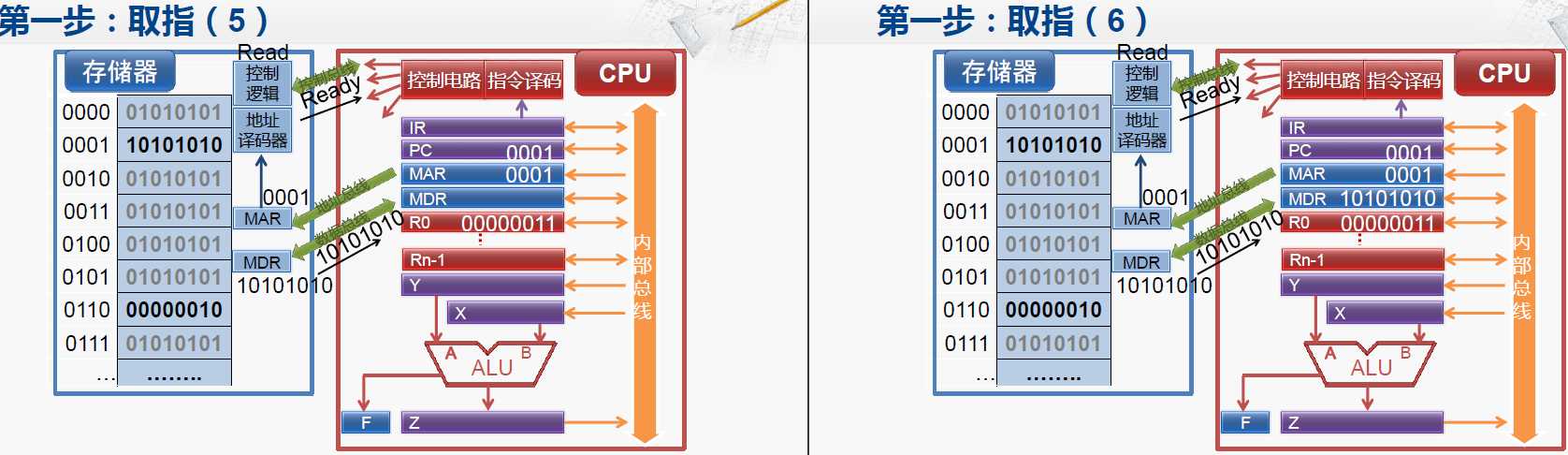

第一步:取址

- 控制器将指令的地址送往寄存器

- 存储器按给定的地址读取处指令的内容,送回控制器

PC中是记录的当前下一条需要执行的指令的地址,开始执行

情景参与角色:CPU_控制电路,存储器_控制逻辑,存储器_MDR,CPU_MDR,CPU_IR

CPU_控制电路: CPU_PC,把你的东西给CPU_MAR,好告诉存储器该做什么

PC,CPU_MAR: 收到 (于是CPU_MAR获得了PC中的东西)

----------此时,CPU_MAR在cpu控制电路的指导下,将数据通过 地址总线发送给了存储器的MAR ,CPU_控制电路并告诉了存储器的控制逻辑只是一个只读的

存储器_MAR: 地址译码器大哥,有你的任务

地址译码器 : 晓得了 (此时控制逻辑通过控制总线告诉CPU : "I am ready" 过了一会对MDR说) 莫睡了,快起来给你个数据。

存储器_MDR: MMP,要的 (获得0001处的内容,10101010)

存储器_MDR: CPU_MDR,我弄好了,给你

CPU_MDR: 好,给我嘛,已收到!

CPU_IR: 给我,我现在要给指令译码的部分了! (CPU_MDR的内容复制给)

CPU_PC: 悄悄的自增。(变成下一条指令的地址)

取址的工作完成

以下是图解:

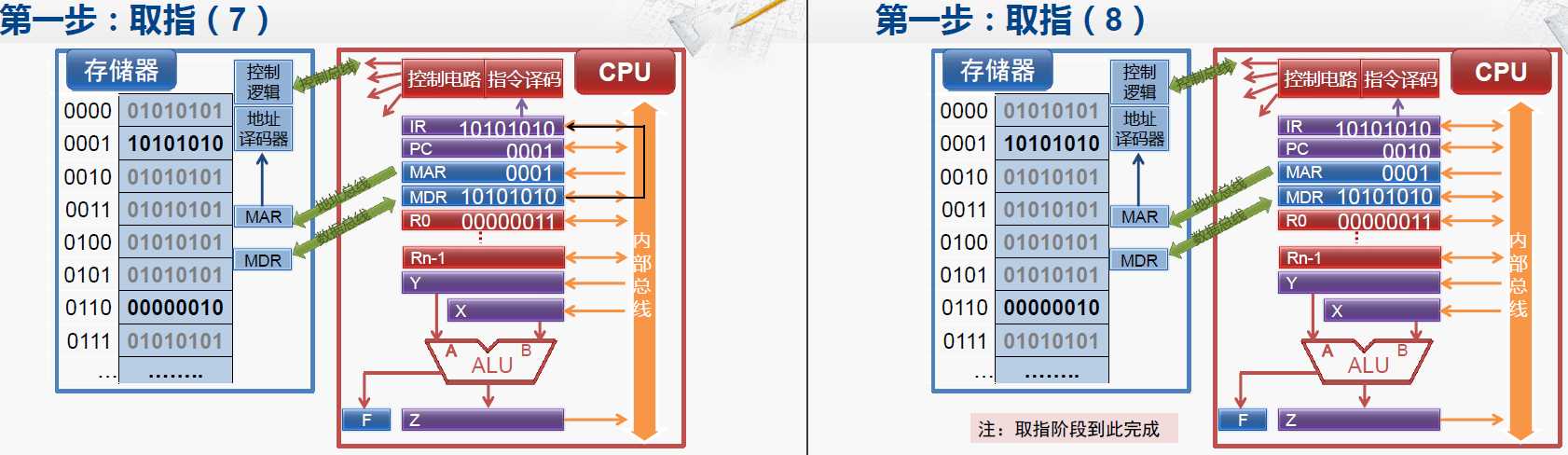

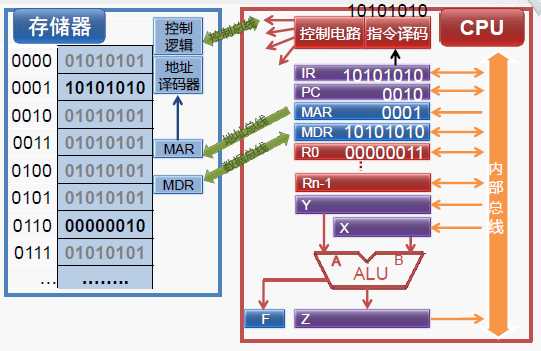

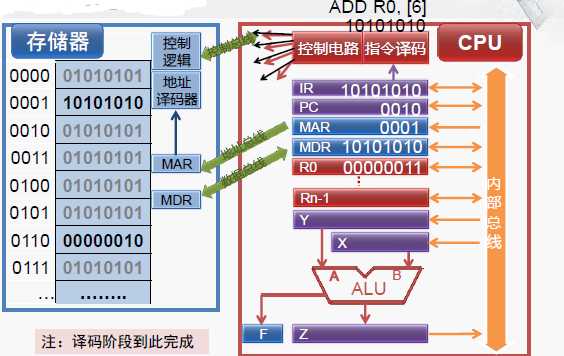

第二步:译码

- 控制器分析指令的操作性质

- 控制器向有关部件发出指令所需的控制信号

CPU_IR现在将数据传送给指令译码器,指令译码器知道了这个指令代表的含义是:ADD R0,[6]

- 控制器从通用寄存器或存储器取出操作数

- 控制器命令运算器对操作数进行指令规定的运算

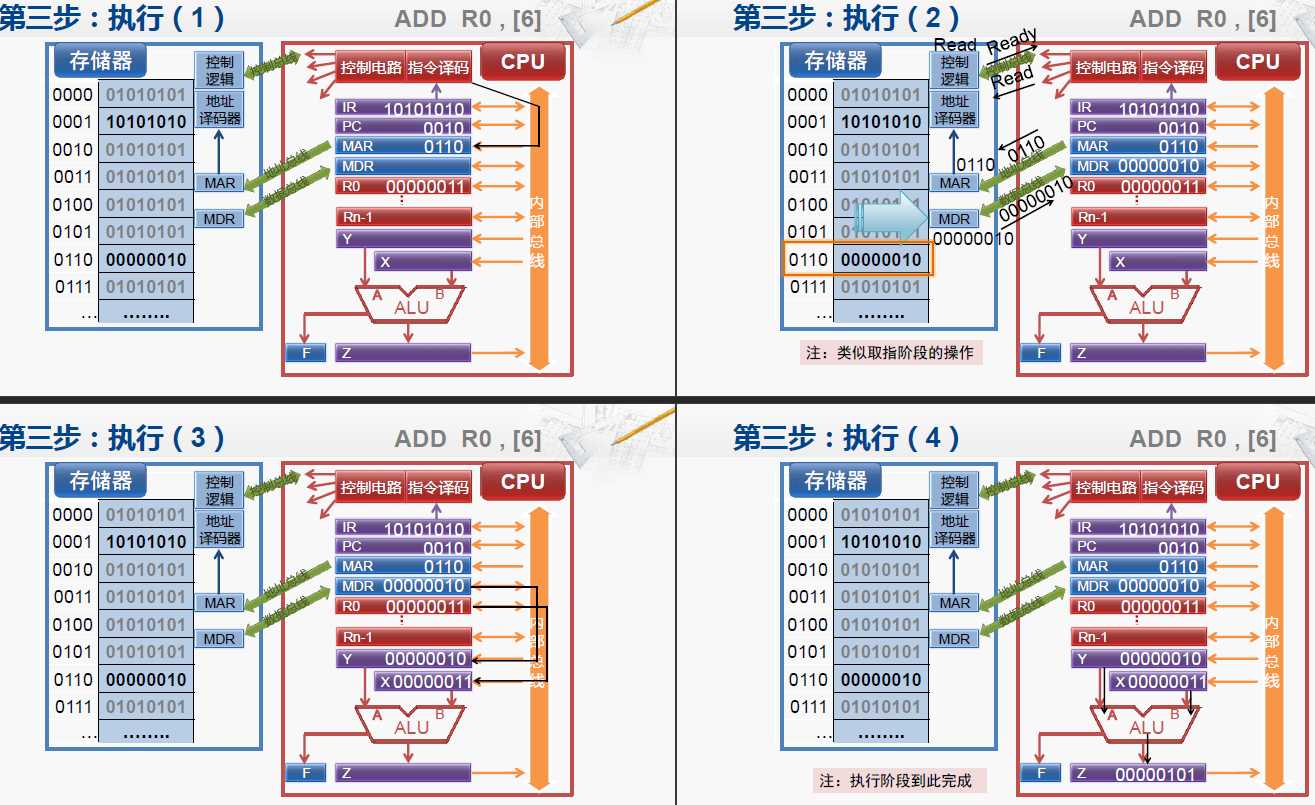

通过译码找到了加数的位置是内存中的第6个的位置,此时CPU_MAR中保存着这个数值0110,CPu控制电路发送只读命令,CPU_MAR将数据送入存储器_mar中,通过地址译码器找到第0110位置的内容,将内容给存储器_MDR,此时控制逻辑发送Ready信号,CPU_MDR开始接收数据,变为00000010,然后MDR和R0通过内部总线将数据送入X,Y寄存器中,XY的内容作为A,B输入进ALU中,然后将结果保存在Z寄存器中,F寄存器中保存的是当前运算结果的状态。

图解:

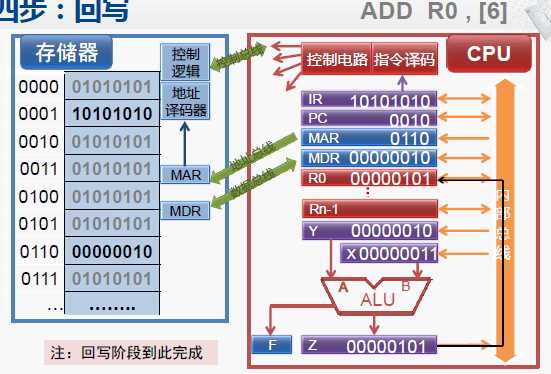

第四步:回写

- 将运算结果写入通用寄存器或存储器(这个要看是代码是怎么写的,默认前面的存储空间就是回写的位置)

声明:以上图片来自北京大学陆俊林老师的计算机组成原理课程PPT

这个过程就完成了,寄存器和内存中的内容进行ADD操作并回写如寄存器中的步骤就是这样的

思考:如果是寄存器和寄存器中的内容进行相加呢?内存某位置内容和寄存器内容相加回写入内存某一个位置呢?