标签:file 掌握 jpg 完成 基于 成功 时钟 ref 串口发送

本文是在前面设计好的简易SDRAM控制器的基础上完善,逐步实现使用SDRAM存储视频流数据,实现视频图像采集系统,CMOS使用的是OV7725。

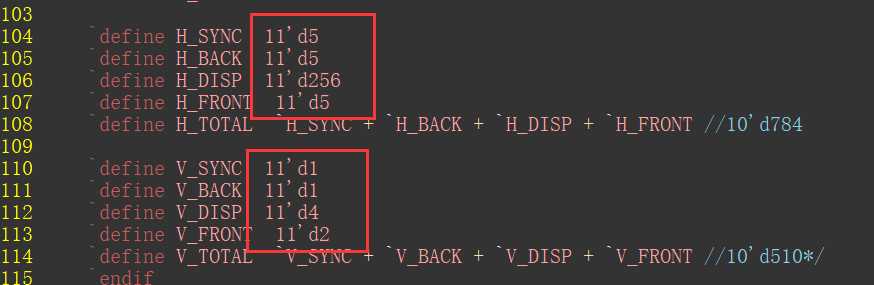

1. 修改SDRAM的时钟到100Mhz

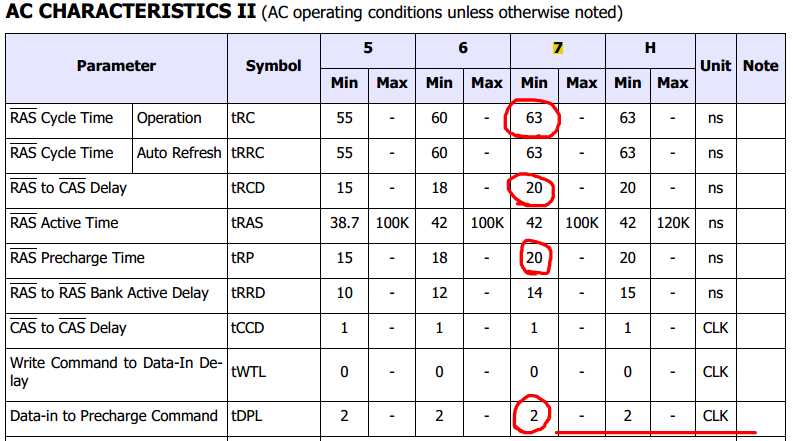

系统时钟提了上来下面对应的时间参数就需要注意,再50Mhz下的这些时间参数的计数器的都需要做相应的修改。

2. 写入一幅图像(640 * 480)到SDRAM

640 * 480 = 307200个数据

307200 / 256 = 1200行,所以我们只需要写入1200行数据写满即可。

OV7725支持640*480分辨率的30万像素摄像头,首先验证SDRAM和VGA级联能够显示出来,所以先用串口发送一幅640*480的图片存到SDRAM中,通过VGA显示出来。

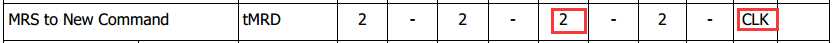

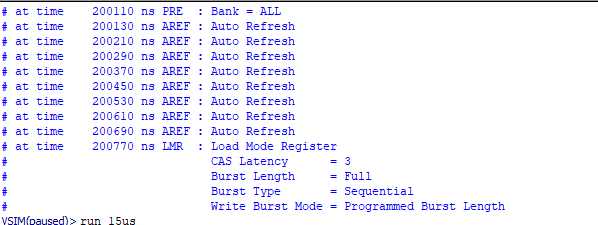

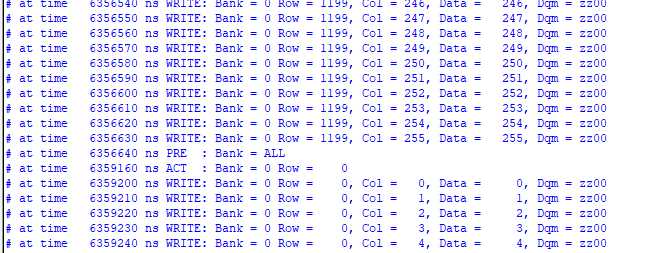

3. 将突发长度设置为full page

视频图像采集显示对实时性要求比较高,所以本设计将SDRAM的突发长度设置为full page。

将burst length设置为full page,full page就是一次写入一行数据,我这里就是2 ^ 8 = 256个位宽16的数据。

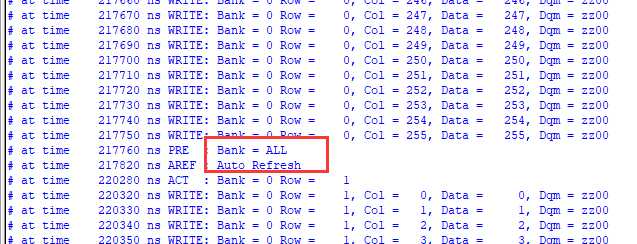

当刷新请求来临,但是些突发还没有写完full page,所以这个时候需要等待,等一个突发长度操作完成,才能去进行刷新。相应的读操作也是一样的。

SDRAM写入1200行后又会继续写入数据。

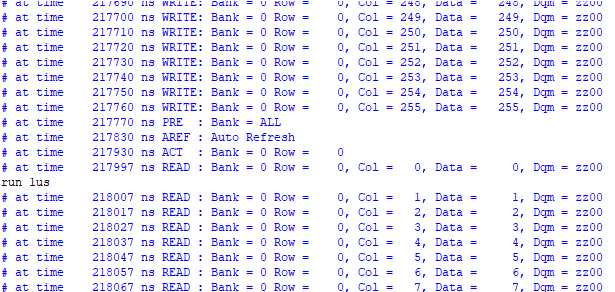

为了要求设计的实时性,做到编写边读,当系统检测到第一次写入数据时,然后触发使能,然后就开始读数据,实现边读边写。

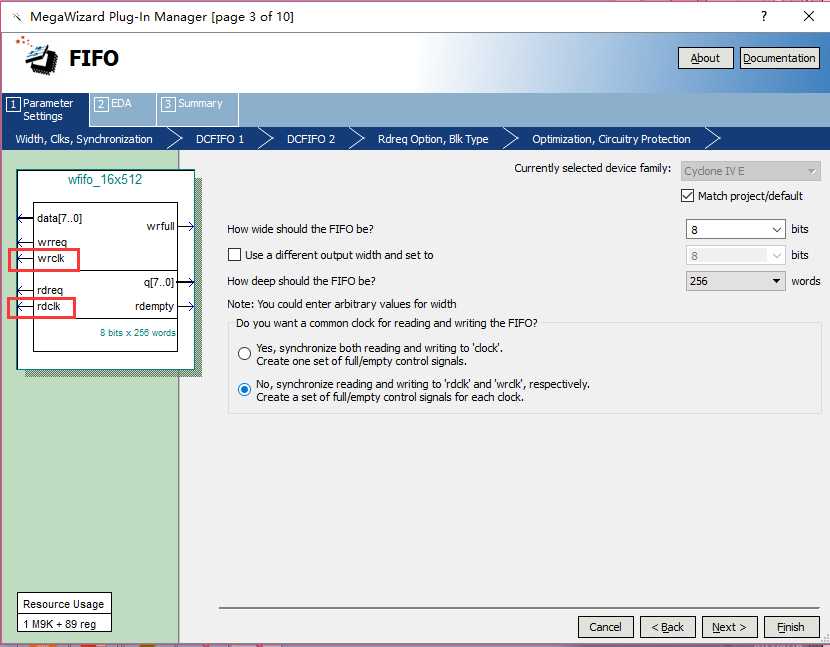

sdram写模块一次写入256个数据,rdusedw为fifo深度判断,设置fifo深度为512,当rdusedw大于256时,即拉高wr_trig,读fifo模块也是一样的,从sdram中把数据写入fifo里,当读fifo的wrusedw小于256就往里面写数据。fifo起到一个缓冲作用,既不能写满也不能读空。这里是博主感觉到妙的地方,使用异步FIFO缓冲,实现数据再两个模块在时钟域不同的情况下传输。基本上FIFO一直处在半满的状态下。

串口的时钟是50Mhz,SDRAM写入的时钟是100Mhz,所以这里fifo应该要两个独立的读写时钟。使用两个fifo,一个fifo作为串口发送过来的数据和sdram写数据端口的连接,一个作为VGA和sdram读数据端口连接。VGA模块的读使能信号决定什么时候从sdram读出数据进行显示。

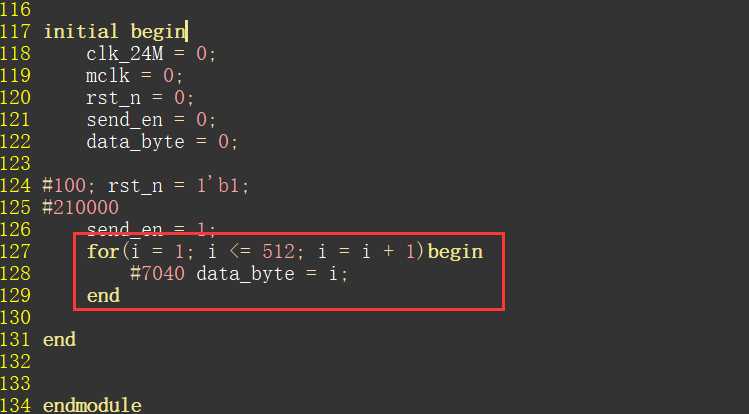

这部分由于数据比较大,而且出了错不容易查找,所以更要做好充分的仿真。具体的仿真方法,我是这样仿真的,在testbench里加上串口发送模块,把接收模块的波特率提高到50Mhz,发送模块也相应的对应上1/16的关系,发送模块里面给一串数据,用for循环的方法。

VGA显示的行场扫描的的参数也缩小,这里主要是看前几行数据有没有对应上,我这是的一行有256个数据,需要注意下一行数据是不是连续显示的。

这个仿真过程是比较痛苦的,具体的就是不断的重复仿真,不断的去凑波形,当然这也应该是一名合格的工程师的必备技能,在不断重复过程中就体现出了do脚本自动化仿真的必要性,找到波形中错误的地方,回去对照代码,一级一级的往上推错误的原因,大概就是这样,掌握了仿真的技巧,其实仿真也不难。确保仿真没问题,下板子基本也就会成功了。

最后效果如下

https://v.qq.com/x/page/y0644dld7dt.html

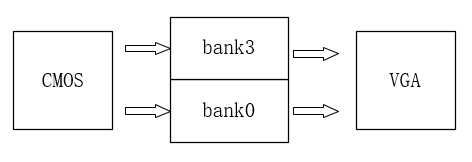

为了达到显示的实时性和同步性,设计SDRAM里的两片bank乒乓操作来进行显示,我先用串口发送一次发送两幅图片分别到两个bank里,调试VGA显示驱动能正常显示。

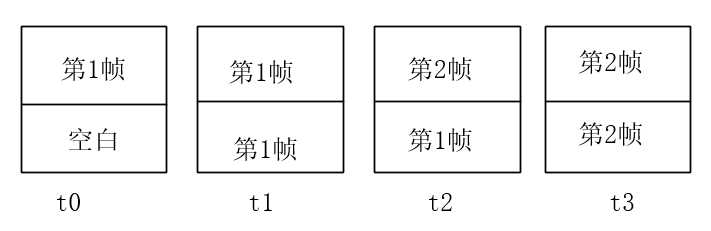

摄像头输入的视频源为640*480@30Hz,VGA的驱动显示为640*480@60Hz,也就是说,摄像头发送过来一帧,但VGA已经扫描了两帧,这里就会存在问题是,直接把摄像头发送过来的视频流数据显示,可能会出现两帧重叠现象。

如图是没有乒乓操作的存储,在t0时刻sdram完成了1/2帧的存储,VGA已经显示了1帧,t1时刻sdram完成1帧的存储,VGA显示了两帧,到了t2时刻可以看到第一帧和第二帧的是交叠的,在理想的情况下这样显示其实是没有什么问题,即使你的t2时刻第一帧图像和第二帧的图像重合,人的肉眼也察觉不到。但是实际上考虑到硬件本身的因素,摄像头输出的帧率并不能保证完整的640*480@30Hz,这样如果继续单帧存储,那么这样的两帧交叠可能会更严重,乒乓操作可以解决这个问题。

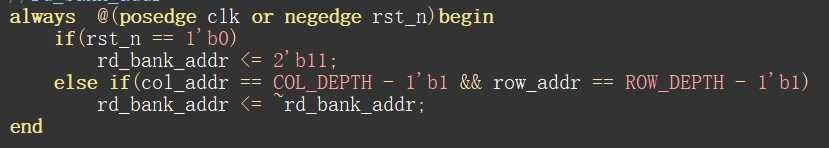

我们为了确保当前显示的一帧是完整的一帧,使用两个bank进行分别存取,在刚开始的时候摄像头给bank0写入数据,写满bank0然后切换到bank3写数据,VGA读取bank3的数据,读完一帧切换到bank0读取数据。这样基本上可以保证两帧交叠的概率降低。Verilog代码实现起来也是非常简单的。

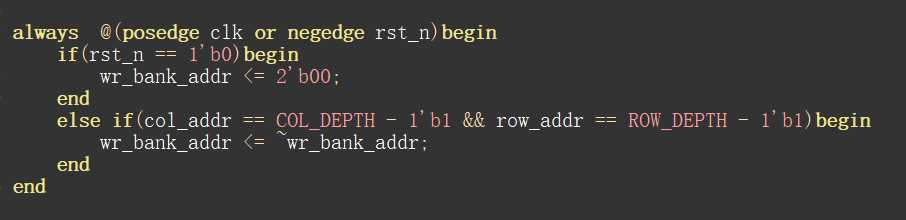

在写模块里加上

在读模块里加上

然后就可以实现乒乓操作了

我先用串口发送了分别发送了两幅640*480的图片到sdram的两个bank里,最后乒乓操作显示的效果还是比较有趣,视频如下。

https://v.qq.com/x/page/w06602k4eho.html

如果完成到上面的过程,sdram控制器基本上没毛病了,在上面写的SDRAM的基础上加上OV7725摄像头驱动显示,摄像头驱动和采集部分代码移植的是CrazyBingo的,这个过程还是比较顺利的,sdram部分基本不用改,直接把摄像头采集到的数据和写sdram使能连接到一起就可以了,我的sdram控制器跑到100Mhz,并实现视频图像实时采集没毛病。

https://v.qq.com/x/page/m06607w3y9s.html

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:https://www.cnblogs.com/ninghechuan/p/9096671.html

标签:file 掌握 jpg 完成 基于 成功 时钟 ref 串口发送

原文地址:https://www.cnblogs.com/ninghechuan/p/9096671.html