标签:Zedboard

工具:vivado 2015、SDK

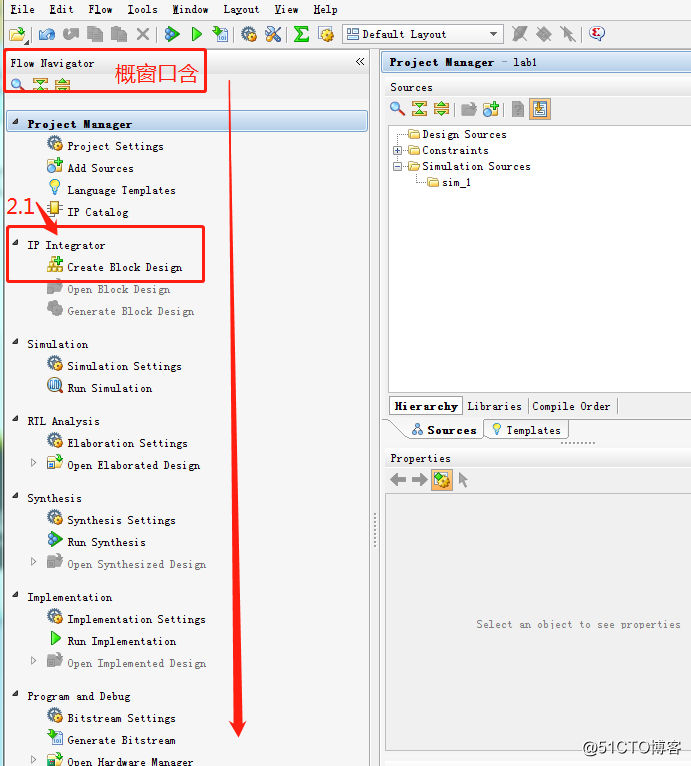

2、Then,使用IP集成器创建处理器系统

使用vivado集成开发环境提供的IP集成器创建一个新的设计块,用于生成基于ARM Cortex- A9处理器的嵌入式硬件系统。

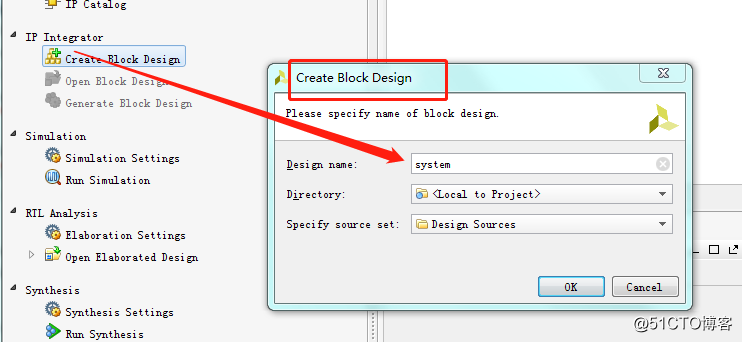

2.1create block design

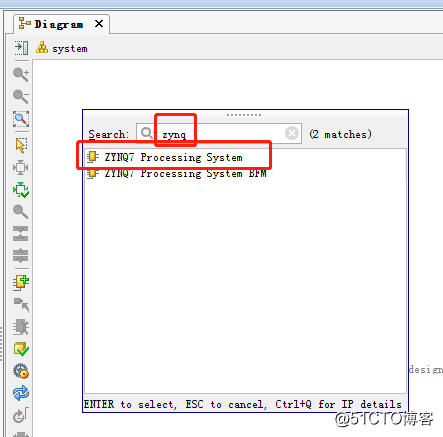

输入zynq搜索,选中标红,回车

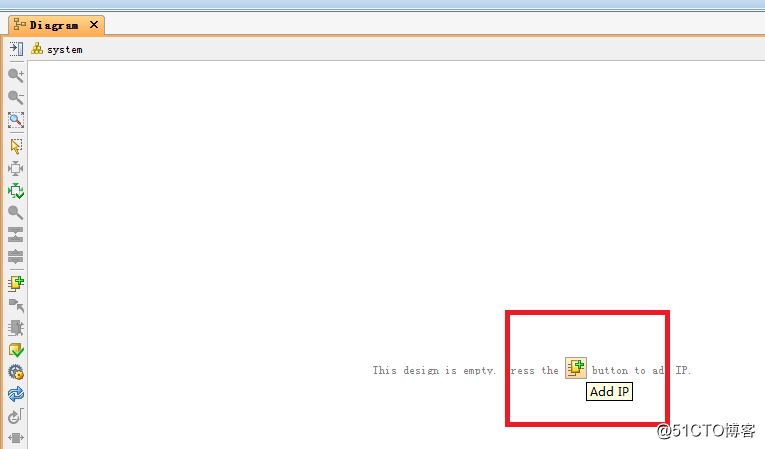

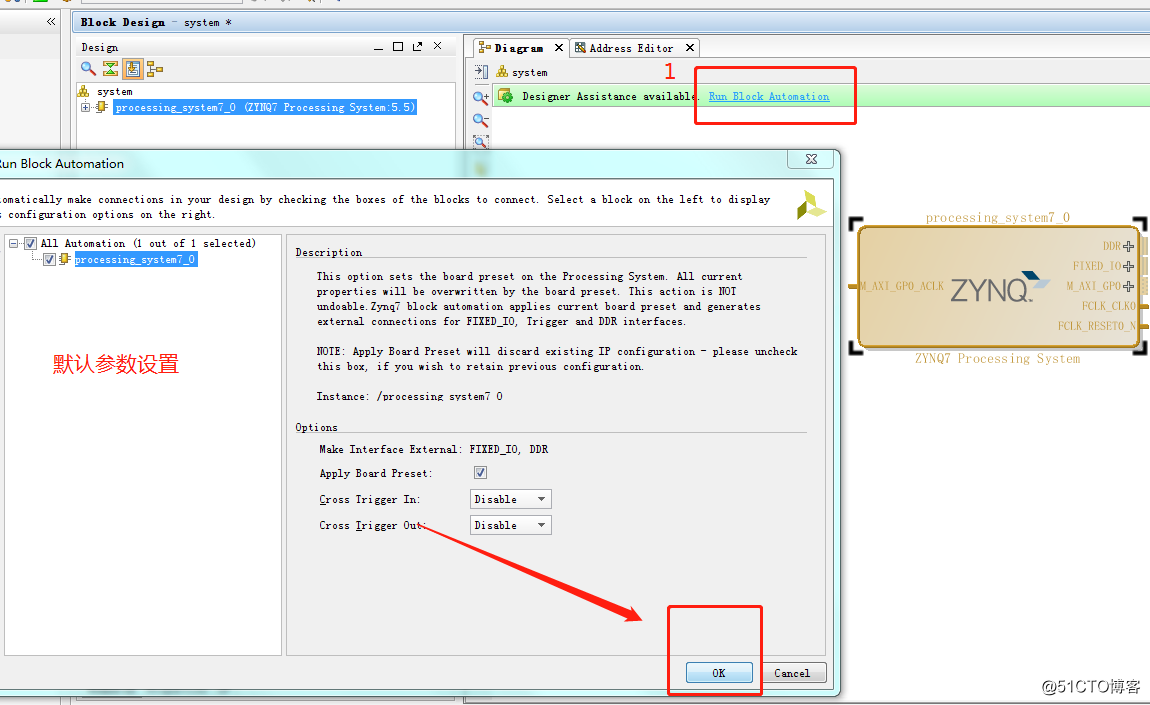

点击标红的绿色字

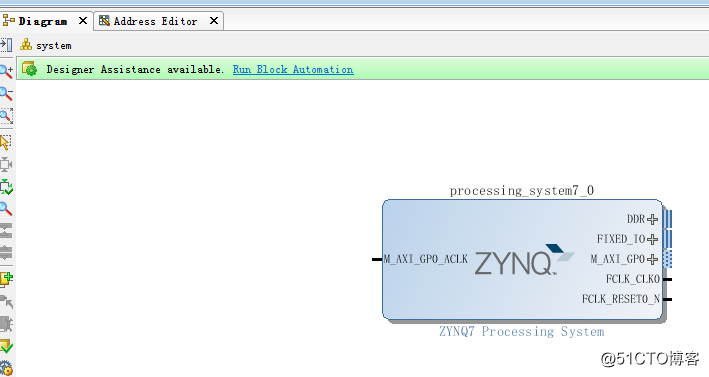

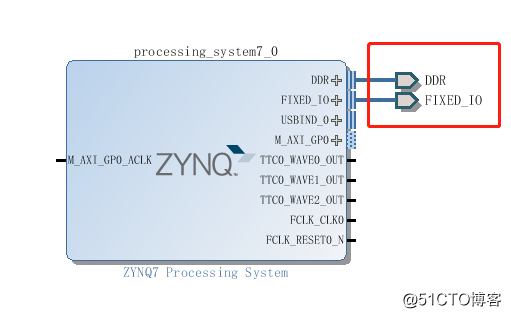

可以得到如下,自动为ddr和固定IO添加了端口,同时也出现很多多余的端口。

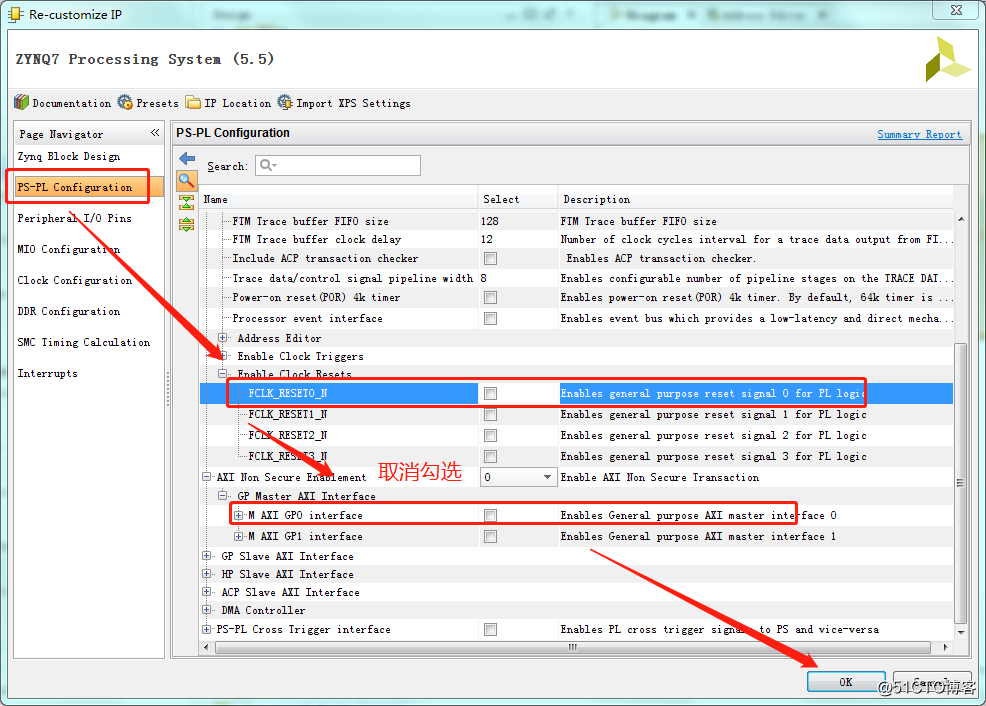

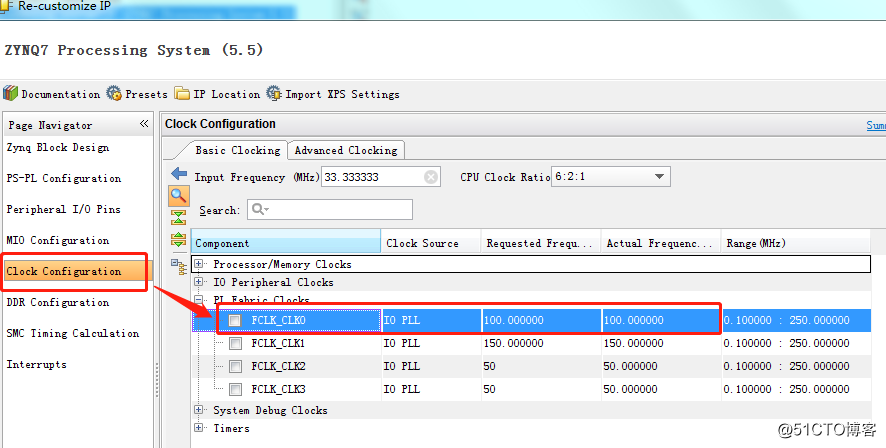

下面准备修改zynq的默认设置,移除那些多余的端口。

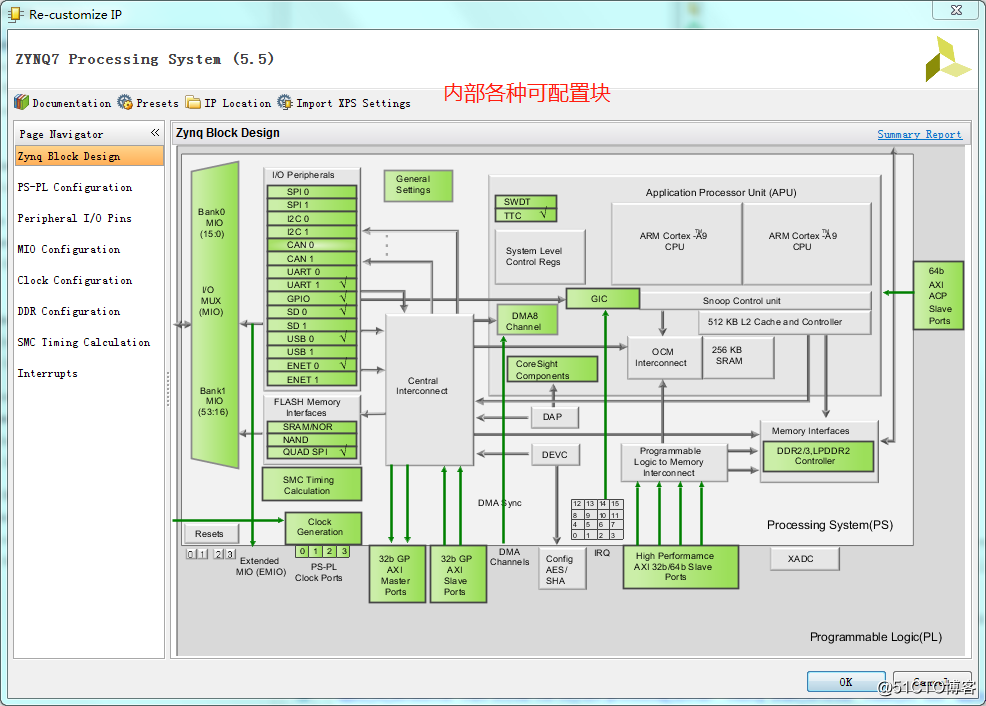

双击zynq符号,出现re-customize IP:ZYNQ7 Processing System。

得到如下图。其中凡是可配置的块,都是以绿色高亮显示。

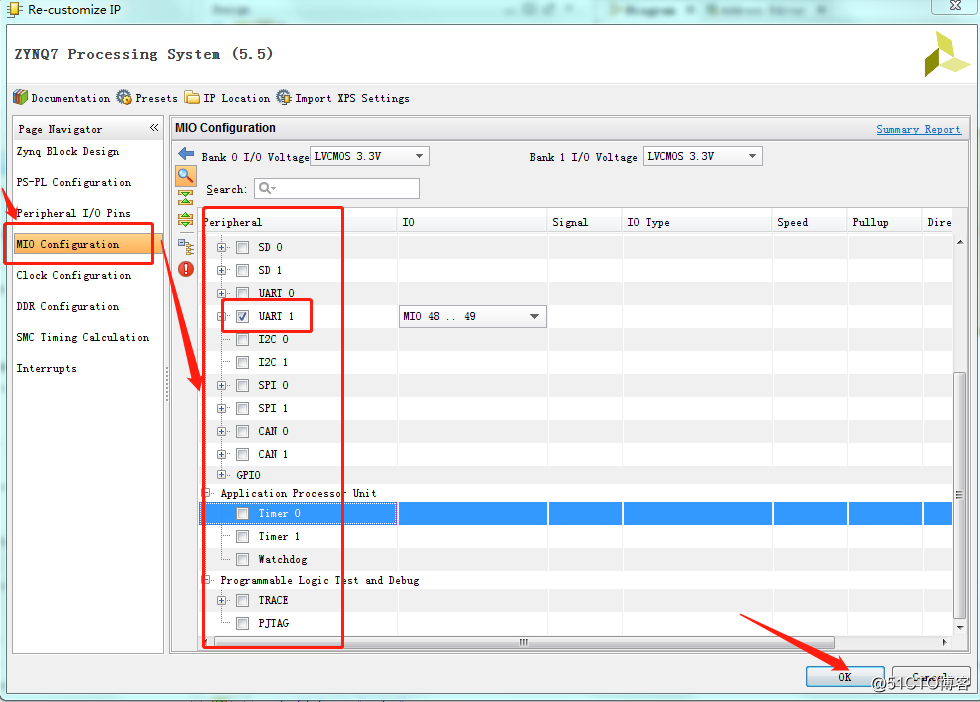

在本设计中只使用UART1,所以其余的都取消勾选。右侧电压也要选3.3

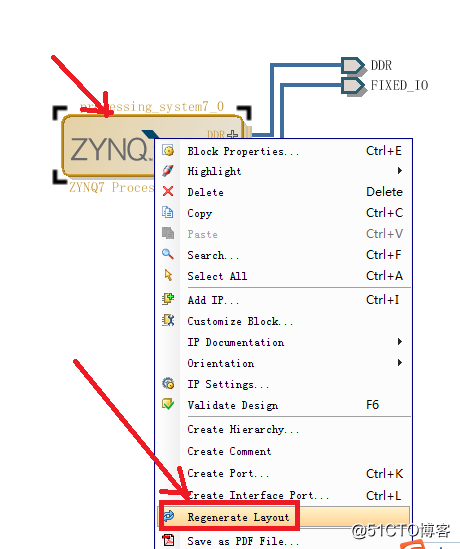

点击OK退出,右键,重新布局。

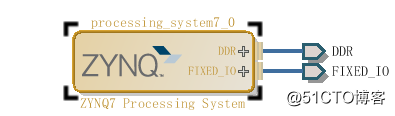

得到如下最小系统

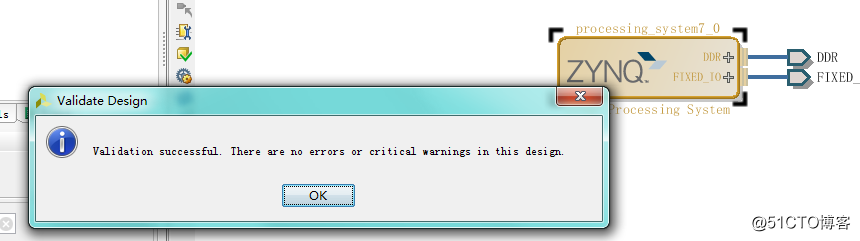

有效性验证:

OK,表示当前设计正确。

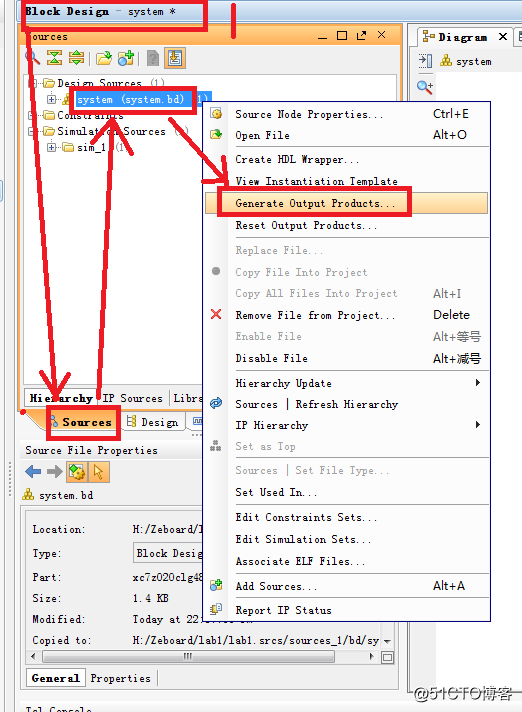

3、生成顶层HDL并导出设计到SDK.

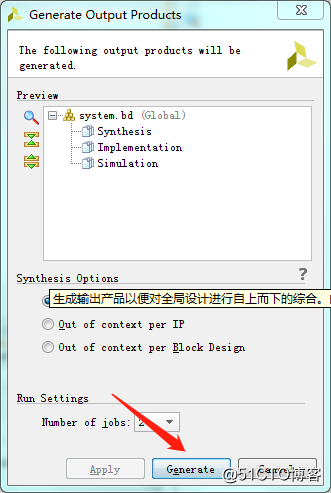

将生成IP集成器输出,顶层HDL,启动SDK.

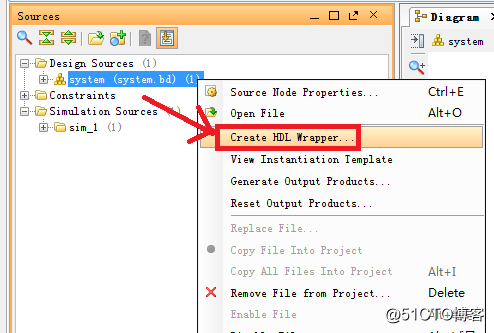

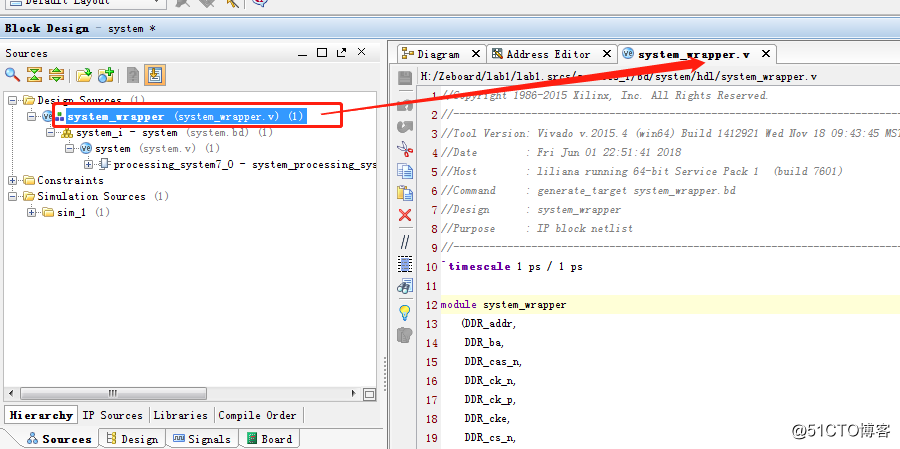

再次选中,生成顶层HDL模型。

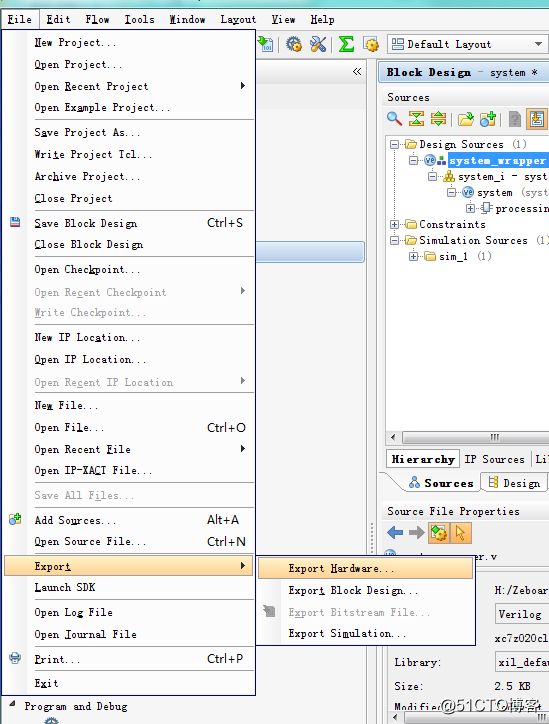

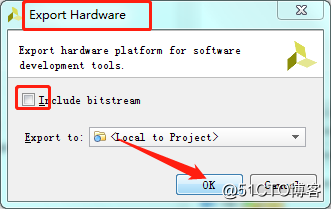

将设计导出到SDK

按提示保存工程。

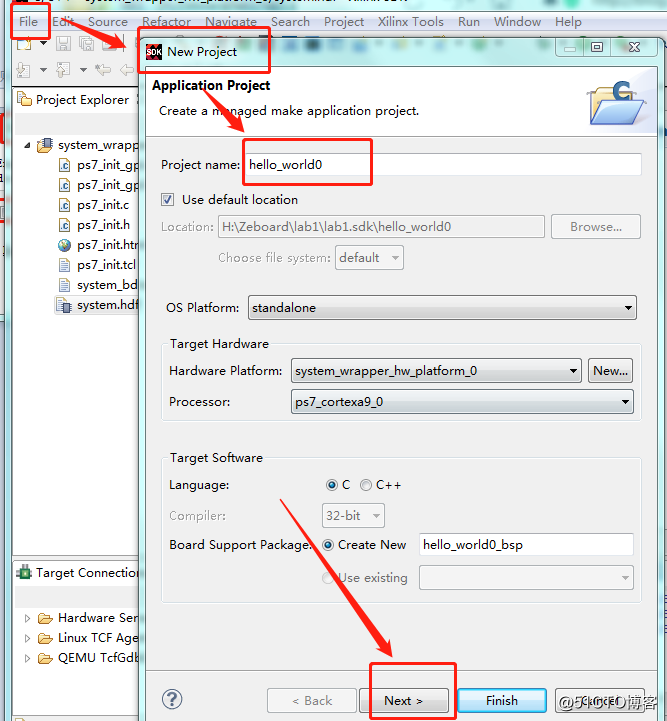

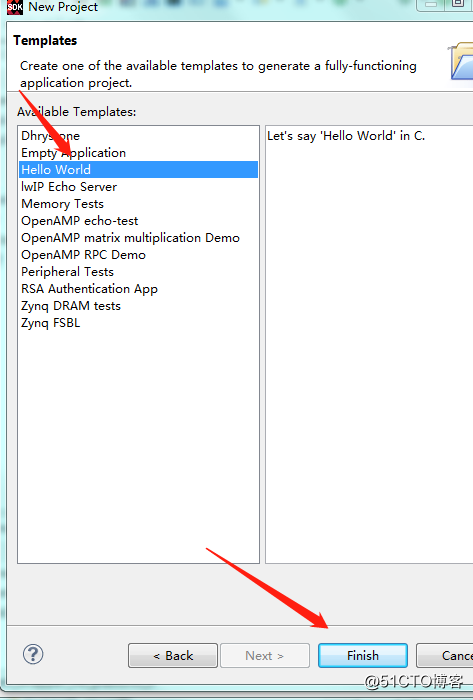

lanch SDK.打开,自动打开.hdf文件。新建按如下提示:

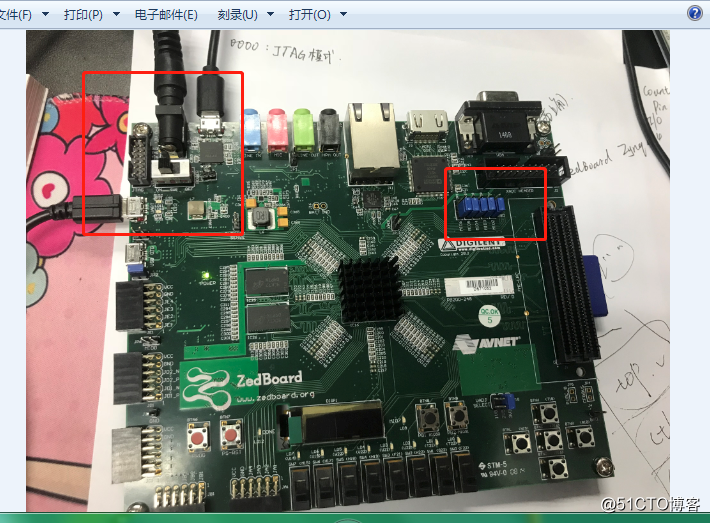

SDK terminal 端口点击绿色+,添加端口。

OK.

标签:Zedboard

原文地址:http://blog.51cto.com/xiaoqiaoya/2123386