标签:简单 i+1 The finish xtu HERE reg 处理 .com

在简单双端口ram中最简单有9个端口:分别是

clka 为输入端口的时钟

wea 读写控制端,高为写,低为读

addra 写地址

dina 待写入的数据

clkb 为输出端口的时钟的

addrb 读地址

doutb 读出的数据

在ip核中还可以加入ena/enb端口,这两个端口的作用是控制相应写入和读出端口的数据,为高是正常写入或读出,为低时写入为0,读出为0。

也可以加入复位端口rst,不过复位有两种优先级CE和SR,选择CE时,rst的优先级低于ENA的优先级;选择SR时,rst的优先级高于ENA的优先级。

还可以选择复位的方式,同步还是异步,一般选择同步。

端口介绍完后,就开始使用双端口ram,工作方式是:可以写入也可以预先用coe文件存入数据,写入数据后就可以读取数据了 ,这里的读取数据和rom的相同,写入地址是多少,就去读取相应地址的数据。

双端口ram和单端口的ram不同,单端口的ram读取数据方式是,写入数据的下一个时钟自动输出数据,仅可用于流水线式数据处理。

这里写了一个简单双端口的ram测试代码

1 `timescale 1ns / 1ps 2 `define clk_period 20 3 //////////////////////////////////////////////////////////////////////////////// 4 // Company: 5 // Engineer: 6 // 7 // Create Date: 11:39:21 06/04/2018 8 // Design Name: ram 9 // Module Name: E:/digital image processing/finial_code/ram_test/testbench/ram_tb.v 10 // Project Name: ram_test 11 // Target Device: 12 // Tool versions: 13 // Description: 14 // 15 // Verilog Test Fixture created by ISE for module: ram 16 // 17 // Dependencies: 18 // 19 // Revision: 20 // Revision 0.01 - File Created 21 // Additional Comments: 22 // 23 //////////////////////////////////////////////////////////////////////////////// 24 25 module ram_tb; 26 27 // Inputs 28 reg clka; 29 reg ena; 30 reg [0:0] wea; 31 reg [3:0] addra; 32 reg [7:0] dina; 33 reg clkb; 34 reg enb; 35 reg [3:0] addrb; 36 reg clk; 37 38 // Outputs 39 wire [7:0] doutb; 40 41 // Instantiate the Unit Under Test (UUT) 42 ram uut ( 43 .clka(clk), 44 .ena(ena), 45 .wea(wea), 46 .addra(addra), 47 .dina(dina), 48 .clkb(clk), 49 .enb(enb), 50 .addrb(addrb), 51 .doutb(doutb) 52 ); 53 integer i; 54 initial clk = 1; 55 always #(`clk_period/2)clk = ~clk; 56 initial begin 57 // Initialize Inputs 58 ena = 1; 59 enb = 1; 60 wea = 0; 61 dina = 0; 62 addra = 0; 63 addrb = 0; 64 #(`clk_period*20 +1 ); 65 for (i=0;i<=15;i=i+1)begin 66 wea = 1; 67 dina = 255 - i; 68 addra = i; 69 #`clk_period; 70 end 71 wea = 0; 72 #(`clk_period*20); 73 /*for (i=0;i<=15;i=i+1)begin 74 addrb = i; 75 #`clk_period; 76 end */ 77 addrb = 4; 78 #`clk_period; 79 addrb = 2; 80 #`clk_period; 81 addrb = 10; 82 #`clk_period; 83 84 // Wait 100 ns for global reset to finish 85 #100; 86 87 // Add stimulus here 88 89 end 90 91 endmodule

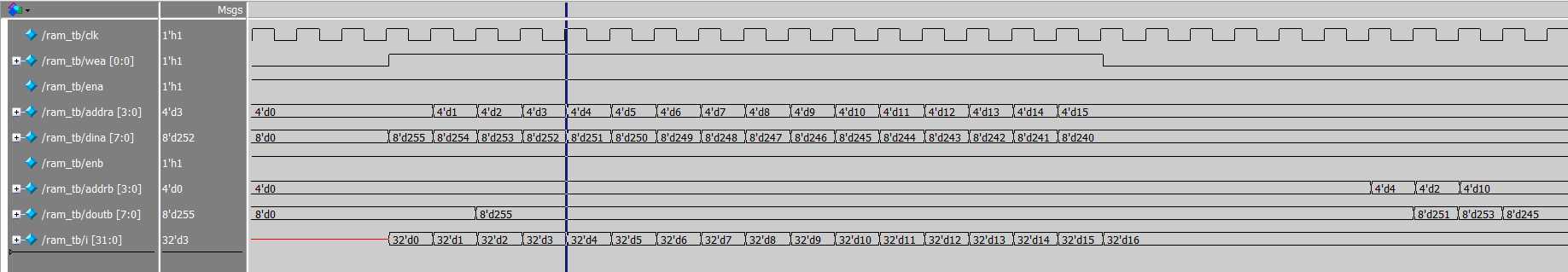

modelsim的仿真结果为:

xilinx fpga中块ram的使用——简单双端口ram的使用

标签:简单 i+1 The finish xtu HERE reg 处理 .com

原文地址:https://www.cnblogs.com/danielwc/p/9133342.html