标签:运算 通道 信号 IV width 模式 spl splay ip核

ZYNQ的优势在于通过高效的接口总线组成了ARM+FPGA的架构。我认为两者是互为底层的,当进行算法验证时,ARM端现有的硬件控制器和库函数可以很方便地连接外设,而不像FPGA设计那样完全写出接口时序和控制状态机。这样ARM会被PL端抽象成“接口资源”;当进行多任务处理时,各个PL端IP核又作为ARM的底层被调用,此时CPU仅作为“决策者”,为各个IP核分配任务;当实现复杂算法时,底层算法结构规整可并行,数据量大,实时性要求高,而上层算法则完全相反,并且控制流程复杂,灵活性高。因此PL实现底层算法后将运算结果交给PS端软件后续处理是非常高效的。

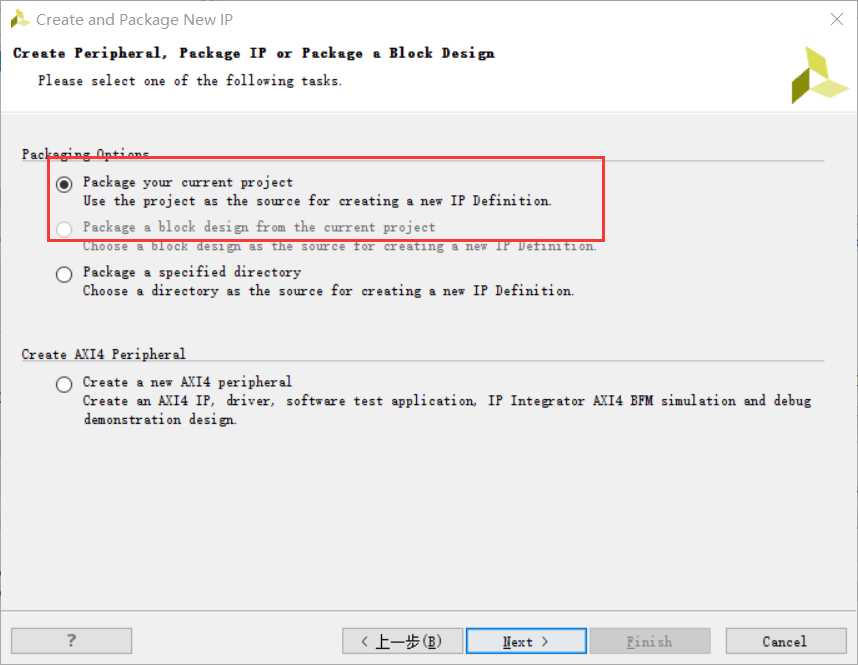

因此PS与PL端数据交互是至关重要的,在传输数据量小的控制 配置初始化等应用场合下无疑会选择简单的AXI-Lite总线,以下对总线接口 自定义IP操作及使用注意事项加以说明。打开Vivado新建工程,选择主菜单栏Tools选项下的Create and package new IP...

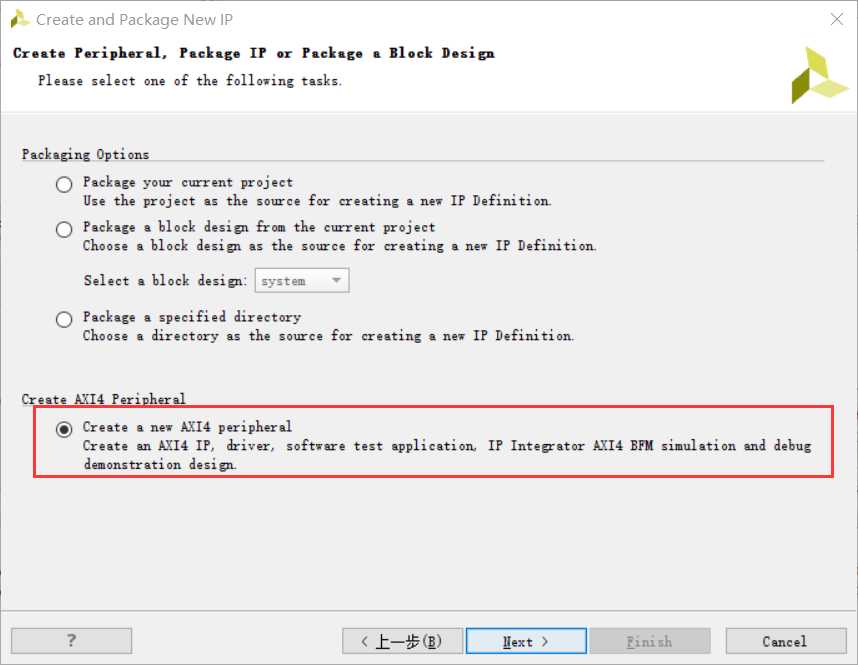

选择创建新的AXI4外设可以自动生成总线接口逻辑

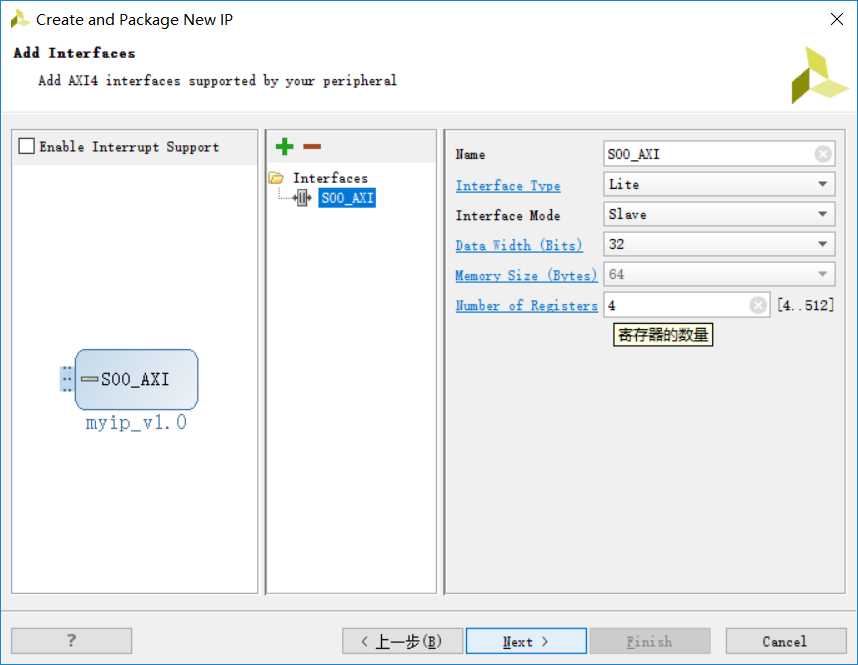

采用AXI-Lite总线的Slave模式,只有寄存器数量是可修改的。注意数据位宽固定32bit,计算机中数据以字节(8bit)为单位存储,因此各个寄存器地址的偏移量为4.这一点在写软件时会有所体现。

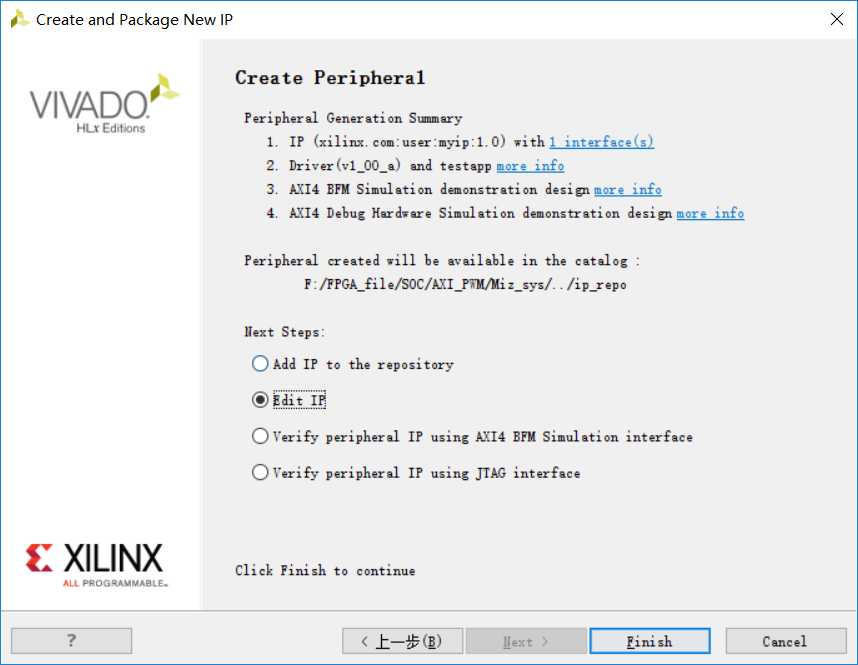

选择编辑IP,打开的工程由顶层Wrapper和AXI-Lite总线接口逻辑组成。关闭自动弹出的IP封装向导,当添加好用户自定义逻辑后再重新封装,否则封装的仅仅是软件生成的接口逻辑。接口比较多,分为写通道和通道,而每个通道基本逻辑又由地址通道和数据通道组成。除了以上四个通道外,写通道包含应答通道以返回CPU确认信息。每个接口以S_AXI_开头,之后AW代表地址写,W代表数据写,AR代表地址读,R代表数据读,B代表响应。关于AXI总线的基本特性在之前的博文中已有阐述,无非就是READY和VLD信号的“握手”。因此这五个核心信号包括VALID DATA和READY。

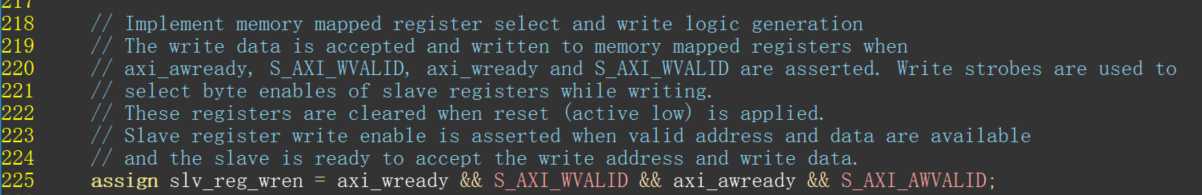

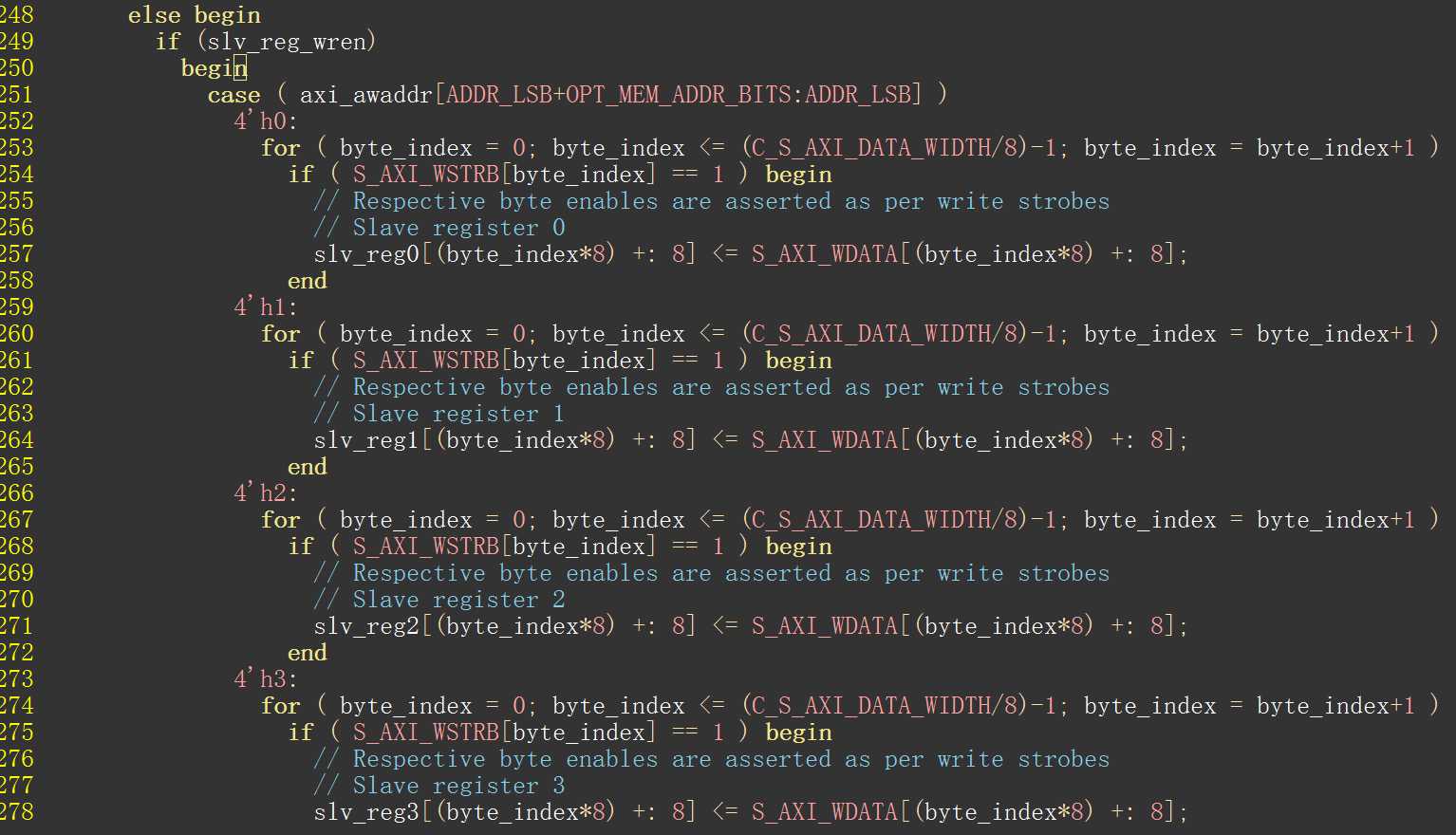

从上述代码可以看出,只有在写地址通道和写数据通道均握手成功时才能有效写入寄存器。

![]()

根据参数声明和寄存器选择与写操作逻辑可知,是根据地址[5:2]这四位来判断写入哪一个寄存器。如:

地址0,即6‘b0000_00

地址4,即6‘b0001_00

地址8,即6‘b0010_00

地址12,即6‘b0011_00

因此[5:2]部分依次是0 1 2 3,从而验证了之前地址偏移量是4的观点。这里的slv_regx信号就是我们需要送入自定义逻辑的控制信号了。

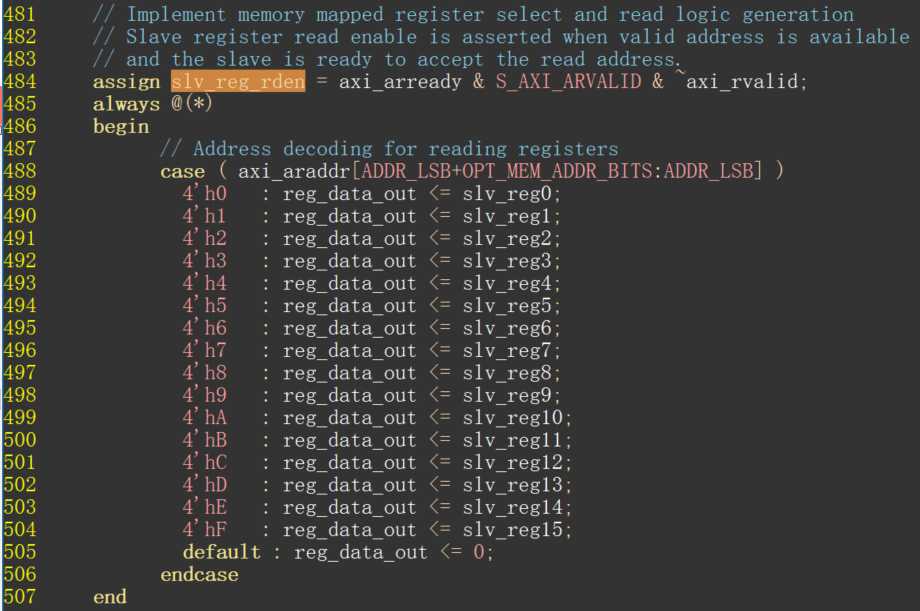

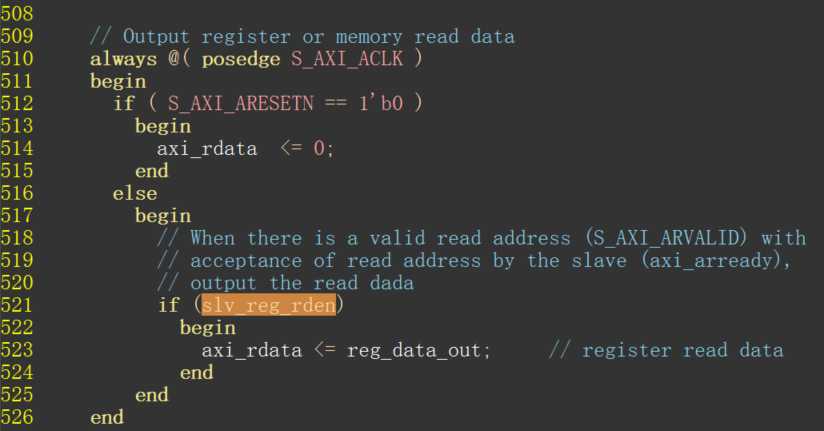

上面是读操作核心逻辑,当从机收到有效的读操作地址且准备好后,会将寄存器数据送回到主机。换句话说读操作读到的数据仅是单纯写入的控制数据,并不是自定义逻辑的处理结果。所以读操作要将489行开始的右侧数据源更换成自定义逻辑处理后有效数据。如:reg_data_out <= user_module_dout;

内部添加的自定义逻辑可以直接写在该模块内,也可以例化自定义模块或IP核。最后封装当前工程得到支持AXI-Lite总线的自定义IP核。

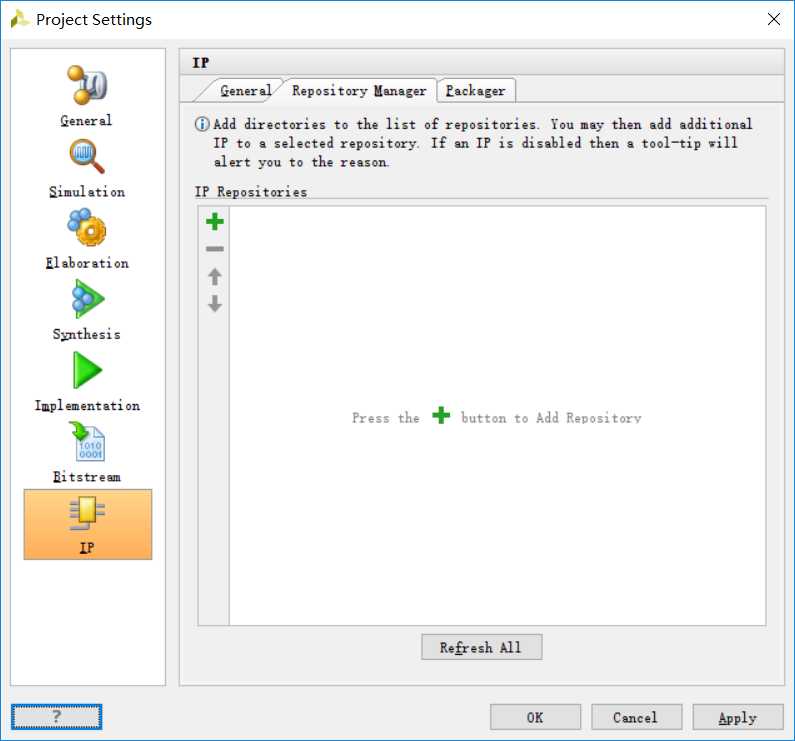

打开需要例化刚才产生IP核的工程,选择Project Setting -> IP -> Respository Manger添加IP核路径或,在block design或 IP Catalog中调用。

标签:运算 通道 信号 IV width 模式 spl splay ip核

原文地址:https://www.cnblogs.com/moluoqishi/p/9158833.html