标签:微处理器 设置 dram move 同传 class 直接 静态 处理

基础知识:

1:(1)位 bit :指一个二进制位,它是计算机中信息存储的最小单位。

(2)字节 byte:指相邻的八个二进制位。B,KB,MB,GB都是指字节

(3)字:计算机内部进行数据传递处理的基本单位。

(4)字长:一个字所包含的二进制位数称为字长,通常把字定义为2字节(16位),双字为4字节(32位),四字为八字节(64位)

2:8086从功能上分为

(1)总线接口单元(BIU):

(2)执行单元(EU):

3:16位通用寄存器:AX,BX,CX,DX,SI,DI,SP或BP。

8位通用寄存器:AH,BH,CH,DH,AL,BL,CL或DL

段寄存器:CS,DS,SS,ES,FS和GS

FLASH寄存器。

4:堆栈操作:push入栈减二:pop出栈加二。

5:输入输出指令:IN:输入指令它能把一个字节(或一个字)由一个输入端口,传送至AL(或AX)。端口地址若是由指令中n所决定,则可寻址256个端口;端口地址也可包含在寄存器DX中,则允许寻址64K个端口

6:OR:按位逻辑或 ,XOR:按位逻辑异或,NOT:按位逻辑非

7:8086处理器有以下七种基本的串操作指令:

(1)MOVES:MOVES/MOVESB 传送串/传送字节串;MOVES/MOVESW 传送串/传送字串

(2)CMPS:CMPS/CMPSB 比较串/比较字节串;CMPS/CMPSW 比较串/比较字串

(3)SCAS:SCAS/SCASB 扫描串/扫描字节串;SCAS/SCASW 扫描串/扫描字串

(4)STOP:STOS/STOSB 存储串/存储字节串;STOP/STOPW 存储串/存储字串

(5)LODS:LODS/LODSB 存储串/存储字节串;LODS/LODSW 存储串/存储字串

(6)串输入指令INS/INSB/INSW/INSD----从端口输入字串

(7)串输出指令 OUTSB/OUTSW-----拷贝串到端口

8:8086引脚:

INTR(输入)可屏蔽中断请求信号。这是一个电平触发输入信号,高电平有效。CPU在每一个指令周期的最后一个T状态采样这条线,以决定是否进入中断响应周期。

RESET(输入)复位输入引起处理器立即结束当前操作。这个信号必须保持有效(高电平)至少四个时钟周期,以完成内部的复位过程。当其返回为低电平时,它重新启动执行.

8086标准时钟周期频率为8MHz,一个T状态为125nsTw只能在T3和T4之间插入

9:RAM分类:

双极性RAM:

MOS RAM:

静态RAM:不需要刷新,故可以省去刷新电路,存取速度较动态RAM快

动态RAM:

1:8086(16位)

2:中断控制器:它可以接收多个外部中断源的中断请求,并进行优先级判断,选中当前优先级最高的中断请求,并将此请求送到CPU的INTR端(8259A)

3:数据缓冲器:当数据在具有不同传输能力的元件之间通过时,用来暂存这些数据的存储器。缓冲器的常见型号有四总线缓冲器74f125和八总线缓冲器(通常74f244)

4:寻址方式:

5:8086微处理器读写总线周期各包括4个时钟周期。

每个时钟周期间隔称为一个T状态

T1 状态:BIU将RAM或I/O地址放在地址/数据复用总线(A/D)上。

T2 状态: 读总线周期:A/D总线为接收数据做准备。改变线路的方向。 写总线周期: A/D总线上形成待写的数据,且保持到总线周期的结束(T4)。

T3, T4:对于读或写总线周期,AD总线上均为数据。

Tw: 当RAM或I/O接口速度不够时,T3与 T4 之间可插入等待状态 Tw 。

Ti : 当BIU无访问操作数和取指令的任务时,8086不执行总线操作,总线周期处于空闲状态 Ti 。

6:段寄存器说明语句的助记符:ASSUME。段定义伪指令:SEGMENT。指针:ptr。定义单字节数据段:DB(编译时,DB后面的数据将视为纯数据而不是指令代码)。

7:寄存器:

16位通用寄存器(AX,BX,CX,DX,SI,DI,SP或BP)

8位通用寄存器(AX,BH,CH,DH,AL,BL,CL或DL)

SRAM:存取速度最快的存储器

DRAM:

EPROM:

E2PROM:

8:中断向量表:中断源的识别标志,可用来形成相应的中断服务程序的入口地址或存放中断服务程序的首地址称为中断向量。

中断类型号和中断向量之间有下面的关系: 中断类型号×4=存放中断向量的首地址 有了存放中断向量的首地址,从该地址开始的4个存储单元中取出的就是中断服务程序的入口

9:逐次逼近型A/D转换器:其实质是逐次把设定的SAR中数字量经D/A转换后得到电压Vc,与待转换的模拟电压Vx进行比较,比较时,先从SAR的最高位开始,逐次确定各位的数码应是“1”还是“0”。

10:DMA(Direct Memory Access,直接内存存取) 是所有现代电脑的重要特色,它允许不同速度的硬件装置来沟通,而不需要依赖于 CPU 的大量中断负载。否则,CPU 需要从来源把每一片段的资料复制到暂 存器,然后把它们再次写回到新的地方。在这个时间中,CPU 对于其他的工作来说就无法使用。

DMA方式的工作原理:

一个设备接口试图通过总线直接向另一个设备发送数据(一般是大批量的数据),它会先向CPU发送DMA请求信号。外设通过DMA的一种专门接口电路――DMA控制器(DMAC),向CPU提出接管总线控制权的总线请求,CPU收到该信号后,在当前的总线周期结束后,会按DMA信号的优先级和提出DMA请求的先后顺序响应DMA信号。CPU对某个设备接口响应DMA请求时,会让出总线控制权。于是在DMA控制器的管理下,外设和存储器直接进行数据交换,而不需CPU干预。数据传送完毕后,设备接口会向CPU发送DMA结束信号,交还总线控制权。

实现DMA传送的基本操作如下:

(1)外设可通过DMA控制器向CPU发出DMA请求:

(2)CPU响应DMA请求,系统转变为DMA工作方式,并把总线控制权交给DMA控制器;

(3)由DMA控制器发送存储器地址,并决定传送数据块的长度;

(4)执行DMA传送;

(5)DMA操作结束,并把总线控制权交还CPU。

用途:

DMA方式主要适用于一些高速的I/O设备。这些设备传输字节或字的速度非常快。对于这类高速I/O设备,如果用输入输出指令或采用中断的方法来传输字节信息,会大量占用CPU的时间,同时也容易造成数据的丢失。而DMA方式能使I/O设备直接和存储器进行成批数据的快速传送。

11:奇偶校验是一种校验代码传输正确性的方法。根据被传输的一组二进制代码的数位中“1”的个数是奇数或偶数来进行校验。采用奇数的称为奇校验,反之,称为偶校验。采用何种校验是事先规定好的。通常专门设置一个奇偶校验位,用它使这组代码中“1”的个数为奇数或偶数。若用奇校验,则当接收端收到这组代码时,校验“1”的个数是否为奇数,从而确定传输代码的正确性。

12:

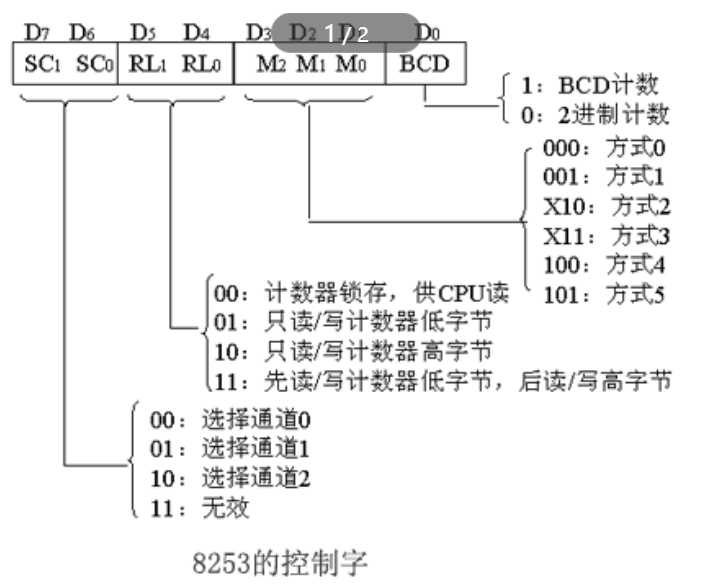

13:可编程定时器/计数器8253

(1)控制字:

(2)计数初值:==输入频率/输出频率

(3)初始化程序:

MOV DX ,尾地址

MOV AL ,控制字

OUT DX,AL

MOV DX,头地址

MOV AL,计数初值低八位

OUT DX,AL

MOV AL,计数初值高八位

OUT DX,AL

14:可编程并行接口8255A

15:存储容量与地址线与数据线

地址线确定容量:2?n字节

数据线确定字长:若字长32位,则一字等于32bit,表示处理器一次可处理4个存储单元

1111

标签:微处理器 设置 dram move 同传 class 直接 静态 处理

原文地址:https://www.cnblogs.com/nullering/p/9131021.html