标签:style blog http color os 使用 sp 问题 c

门控时钟,英文名gate clock。所谓“门控”是指一个时钟信号与另外一个非时钟信号作逻辑输出的时钟。比如,你用一个控制信号“与”一个CLK,以控制CLK的起作用时间。

在ASIC中利用此来减少功耗,因为功耗主要消耗在MOS的翻转上了,门控时钟的输出,有一段时间不翻转不变化,减少了功耗;但在FPGA中,由于时钟走专用的网络等原因将导致诸多问题,如门控时钟可能会有毛刺,skew和jitter,以及时序分析等等很多问题。因此,在FPGA设计中,应尽量避免使用门控时钟。

通常用阵列时钟构成门控时钟。门控时钟常常同微处理器接口有关,用地址线去控制写脉冲。然而,每当用组合函数钟控触发器时,通常都存在着门控时钟。如果符合下述条件,门控时钟可以象全局时钟一样可靠地工作:

1.驱动时钟的逻辑必须只包含一个“与”门或一个“或”门。如果采用任何附加逻在某些工作状态下,会出现竞争产生的毛刺。

2.逻辑门的一个输入作为实际的时钟,而该逻辑门的所有其它输入必须当成地址或控制线,它们遵守相对于时钟的建立和保持时间的约束。

我们往往可以将门控时钟转换成全局时钟以改善设计项目的可靠性。

组合逻辑中多用门控时钟,一般驱动门控时钟的逻辑都是只包含一个门,如果有其他的附加逻辑,就容易因竞争而产生不希望的毛刺。门控时钟通过一个时能信号控制时钟的开关。当系统不工作时可以关闭时钟,整个系统处于非激活状态,这样就能够在某种程度上降低系统功耗。

然而,使用门控时钟并不符合同步设计的思想,它可能会影响设计的实现和验证。单纯从功能上看,使用使能时钟替代门控时钟是一个不错的选择;但是使能时钟在使能信号关闭时,时钟信号仍然在工作,它无法像门控时钟那样降低系统的功耗。

Altera的解决方案:

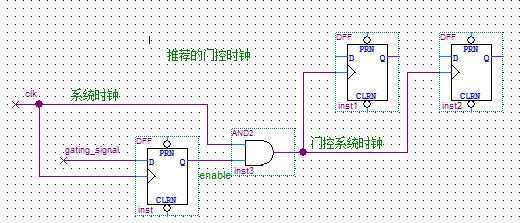

对于上升沿有效的系统时钟clk,他的下降沿先把门控时钟打一拍,然后再用这个使能信号和系统时钟clk相与后作为后续电路的门控时钟。

这样的门控时钟电路很好的解决了组合逻辑常见的一些问题。它避免了毛刺的出现,同时也有效的抑制了亚稳态可能带来的危害。但是从另一个方面来 说,如果这个设计的系统时钟占空比不是很稳定,或者输出的使能信号(enable)与时钟信号(clk)的逻辑过于复杂,那么它也会带来一些功能和时序上 的问题。总得来说,只要设计者控制好这个设计中时钟占空比和门控逻辑复杂度,他还是比下面这个简单的门控时钟电路方案可行。

标签:style blog http color os 使用 sp 问题 c

原文地址:http://www.cnblogs.com/sunmaoduo/p/3999647.html