标签:video ESS 指令 作用 src tor roc ssi 仿真

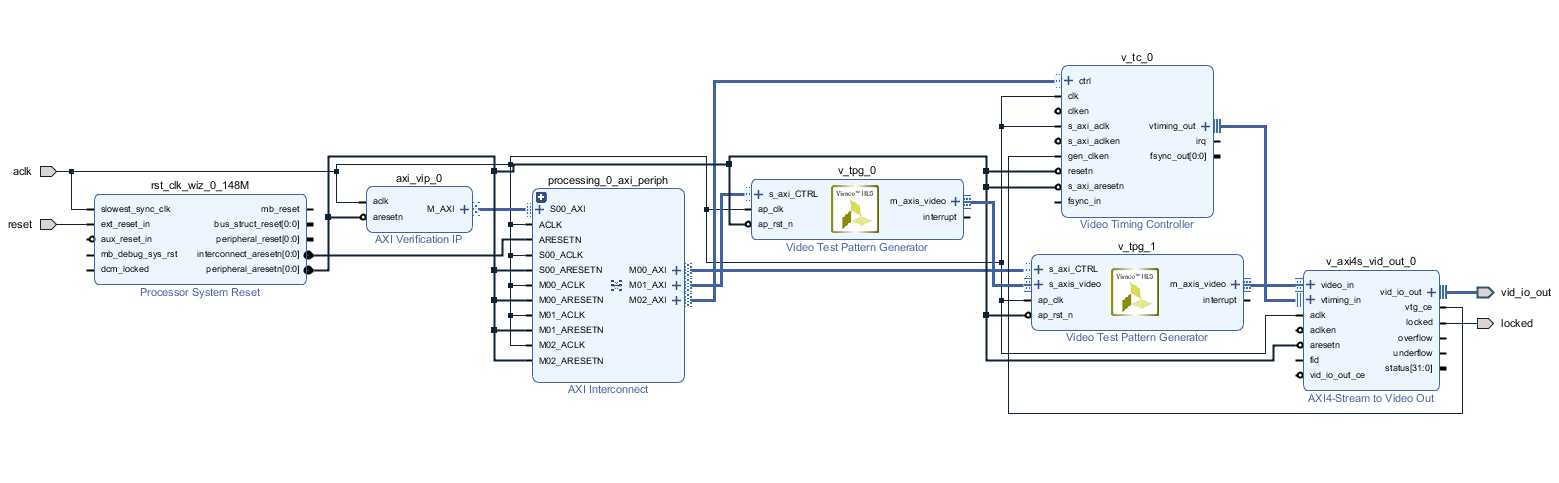

关于tpg例程的仿真

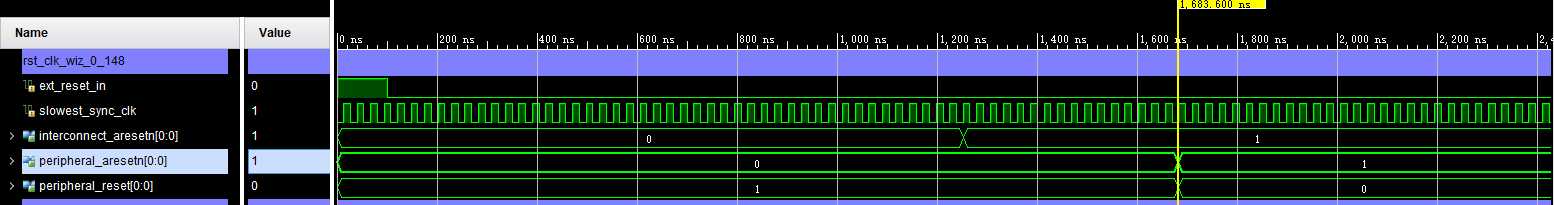

processor system reset---rst_clk_wiz_0_148M

可以看出interconnect_aresetn和peripheral_aresetn的复位作用时间不同,内部复位的时间会短好几个时钟周期。peripheral_aresetn和peripheral_rest是两个完全相反的信号。

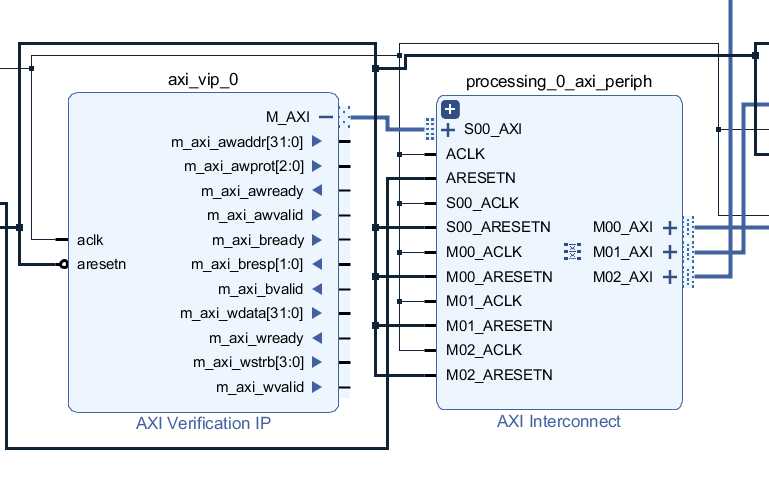

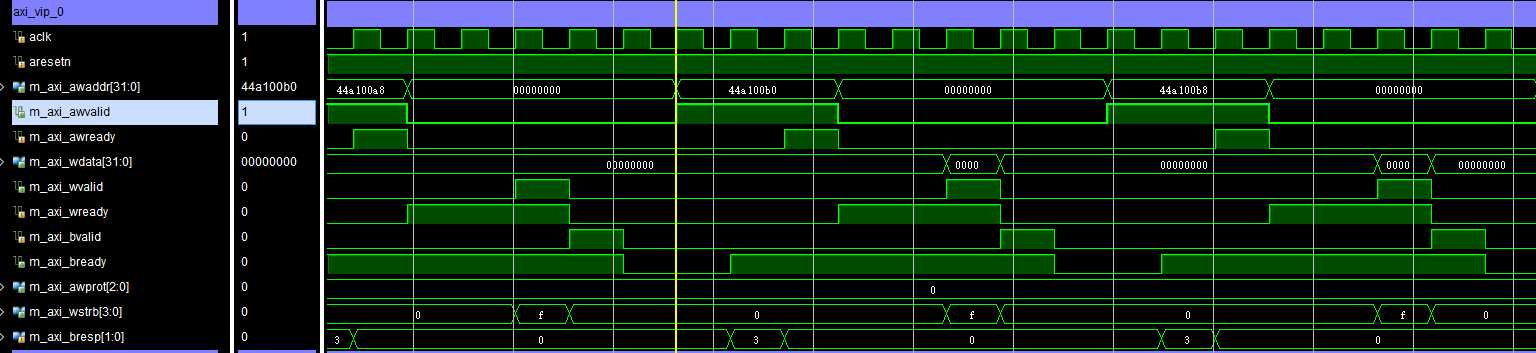

axi verification ip ---axi_vip_0

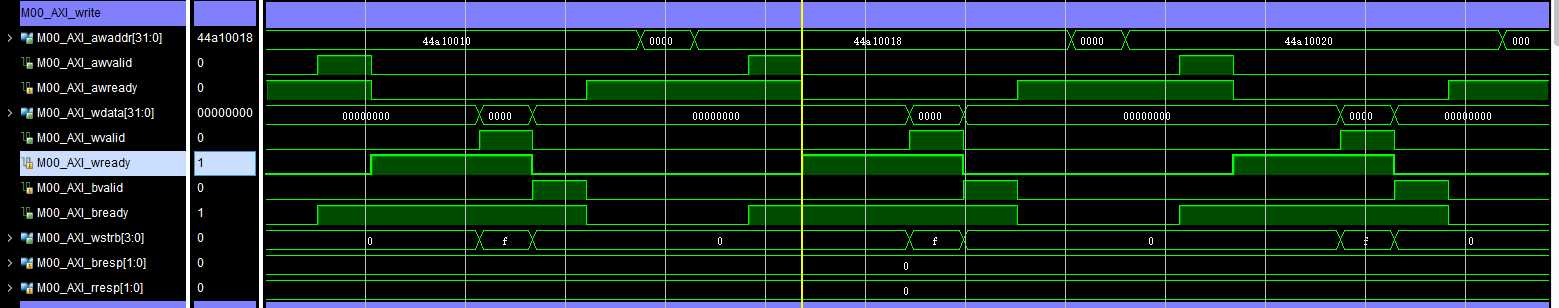

axi上的写数据,写地址,写反馈波形

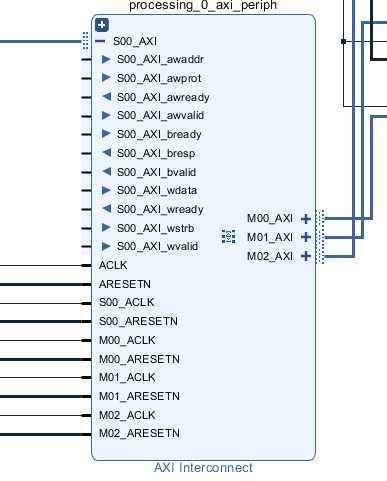

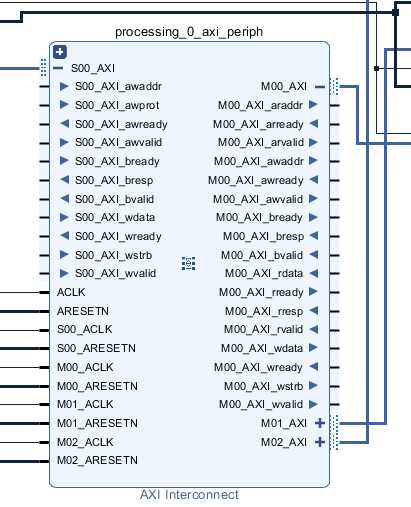

axi interconnect---processing_0_axi_preiph

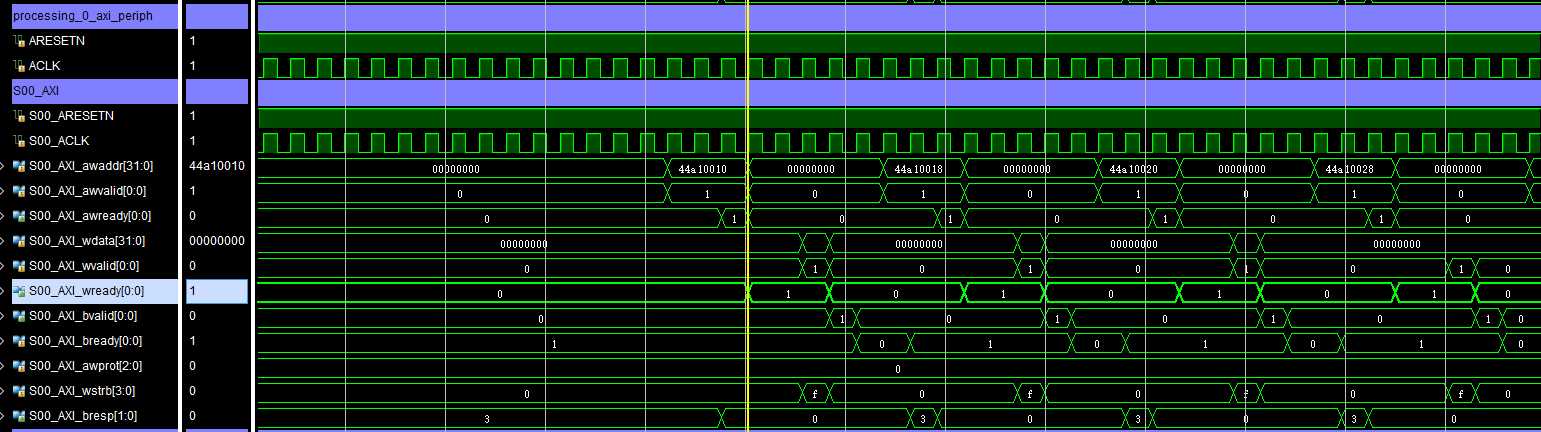

S00_AXI

S00_AXI

从波形上可以判断出,S00_AXI在接收完写地址信号后,马上就产生了wready信号,为接收写数据做好准备,数据接收完成后,wready信号再拉低。

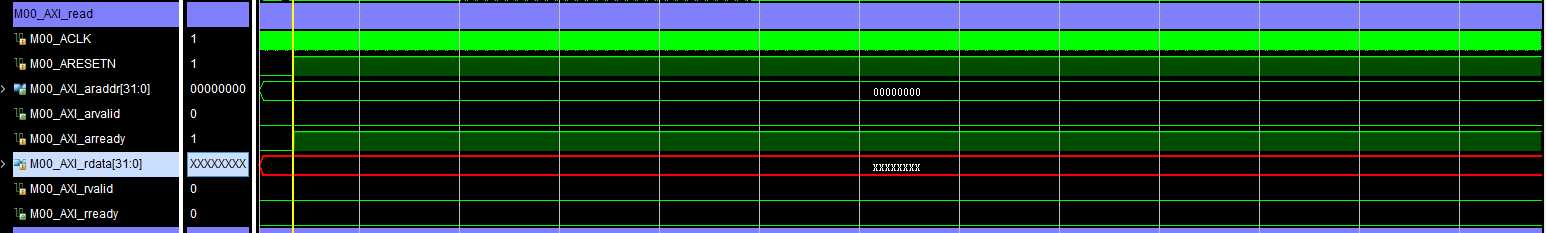

M00_AXI_read

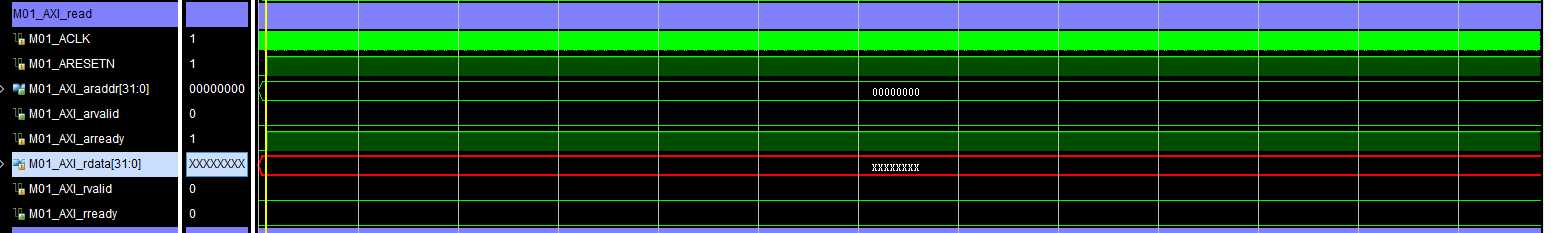

从波形上来看,读信道基本没用

M00_AXI_write

M01_AXI_read

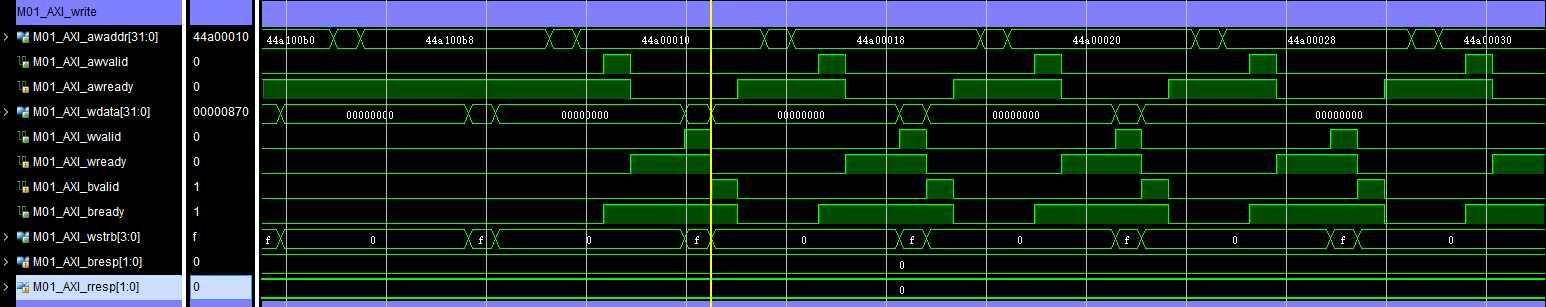

M01_AXI_write

M01_AXI连接的是tpg_0的控制端口。

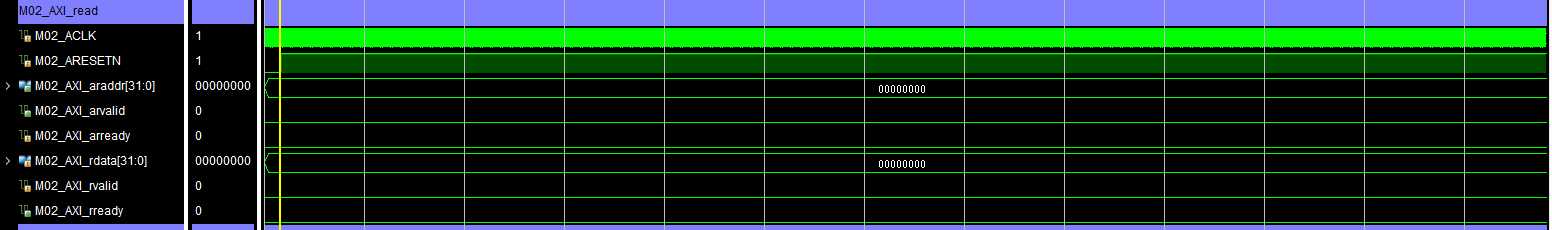

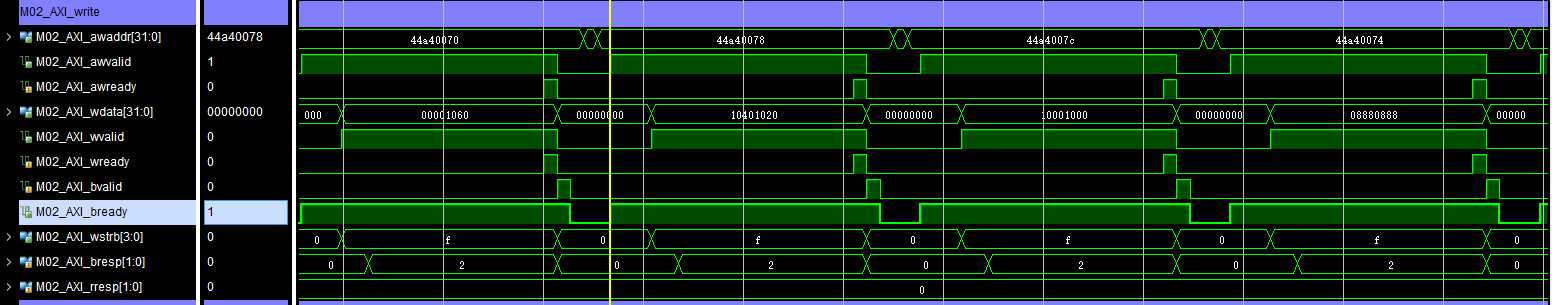

M02_AXI_read

M02_AXI连接的是VTC的控制信号

M02_AXI_write

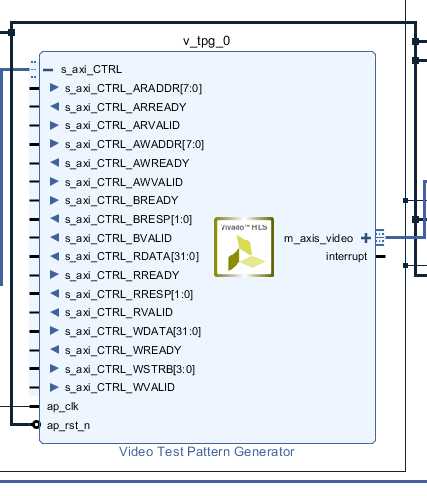

video test pattern generator---tpg_0

s_axi接口信号

接收控制指令

m_axi接口信号

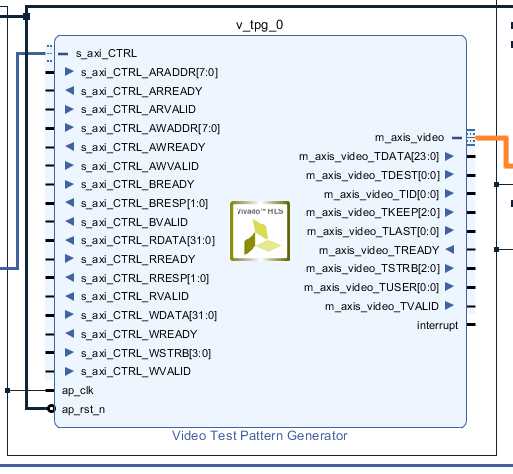

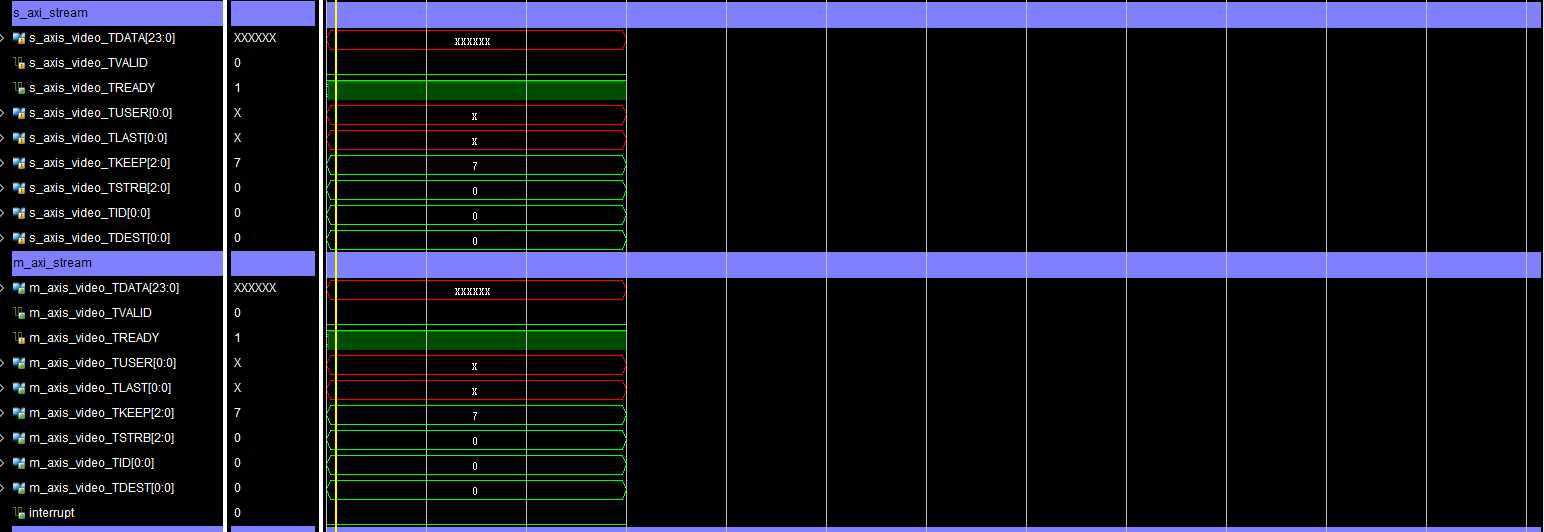

video test pattern generator---tpg_1

axi_lite 接收指令

s_axi_stream和m_axi_stream

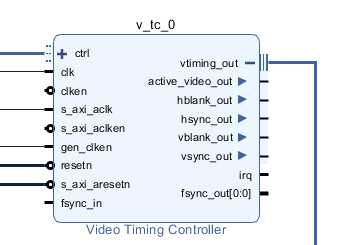

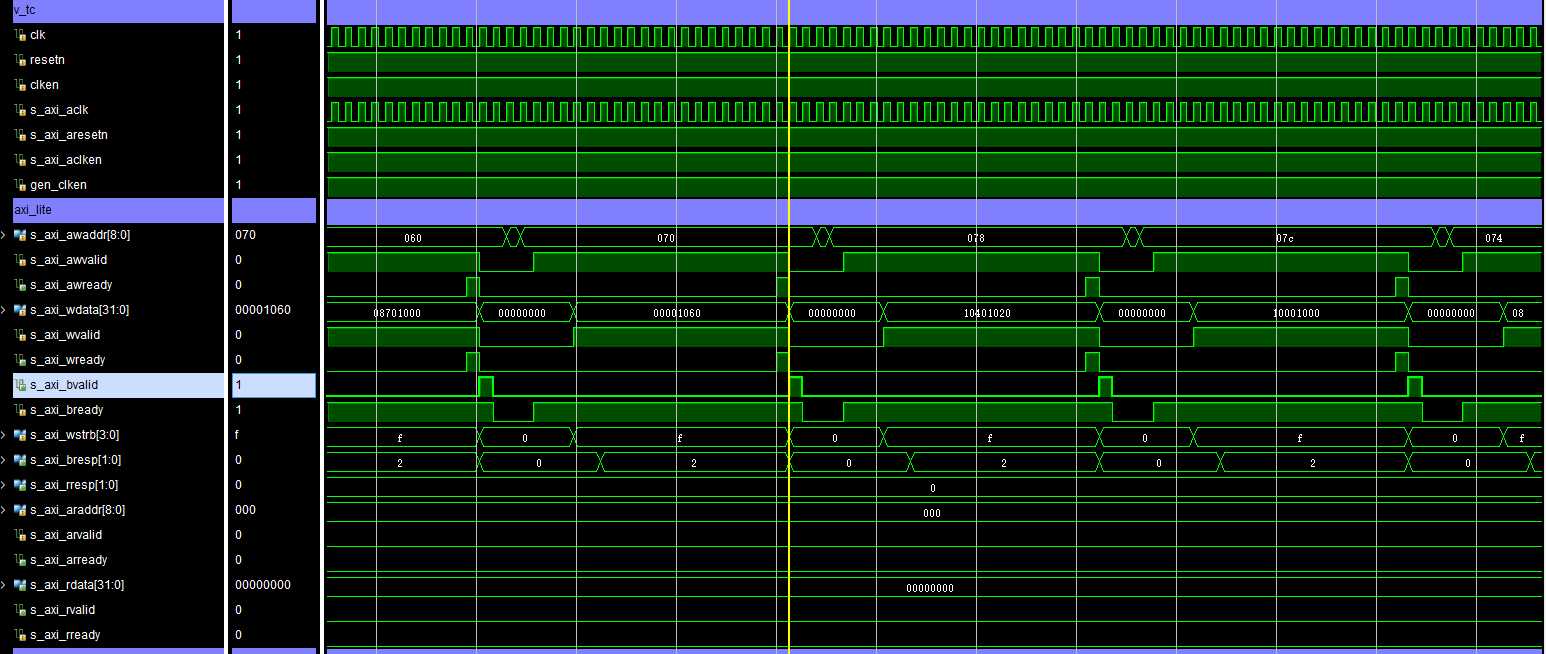

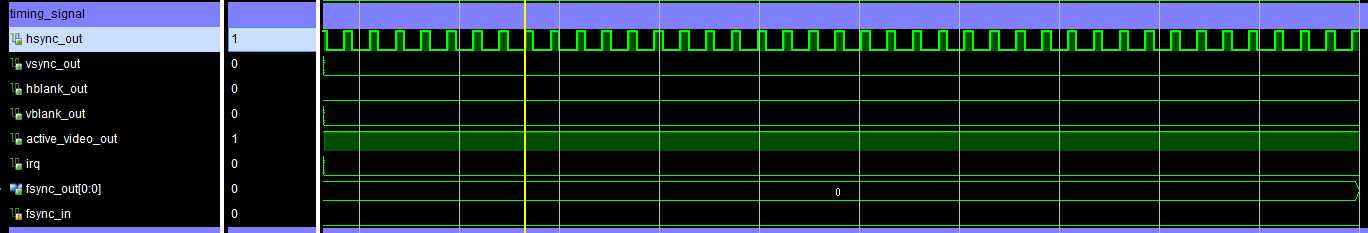

video timing controller---v_tc_0

axi_lite 控制接口

时序信号

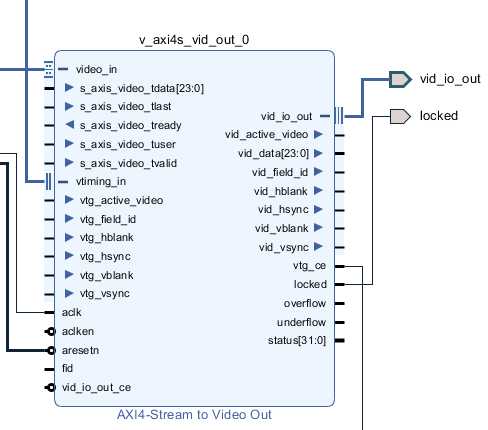

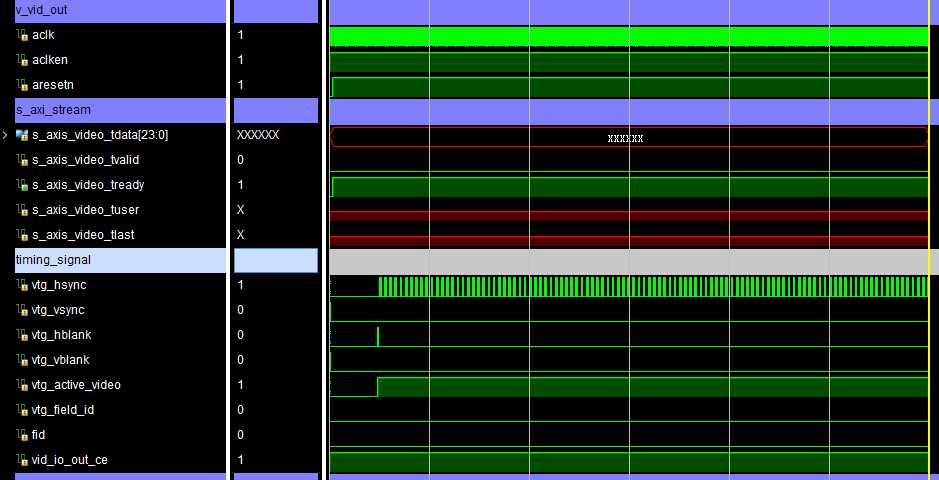

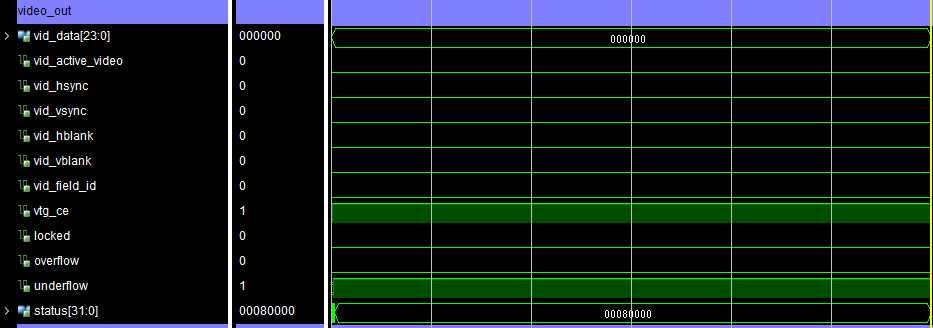

axi4 stream to video out---v_axi4s_vid_out_0

s_axi_stream, timing_signal_in

video_out

标签:video ESS 指令 作用 src tor roc ssi 仿真

原文地址:https://www.cnblogs.com/chensimin1990/p/9238678.html