标签:ESS 控制线 物理 有关 查询 多模块 技术分享 数据 3.4

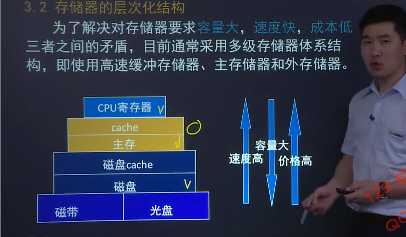

三、存储器层次结构

本章要求

掌握存储器的分类和各类存储器的基本工作原理,包括SRAM、DRAM、ROM,掌握主存储器与CPU的连接和数据交换、双口RAM和多模块存储器。

两个重要考点:

*Cache

*虚拟存储器

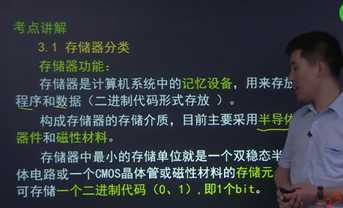

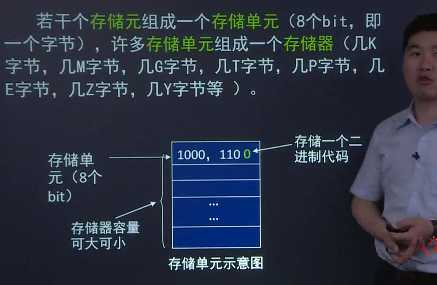

存储器的地址组织:

地址和内容的问题

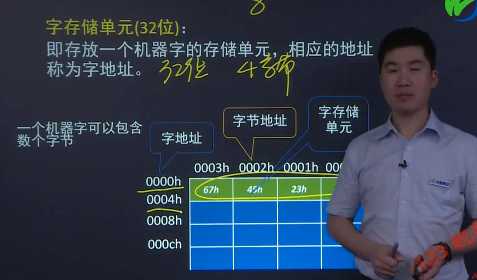

一个32位机一次能访问32个二进制数,4字节,这里讲一下字地址和字节地址的关系。

左边的首字节地址构成大房间的地址。

深入的了解一些问题:

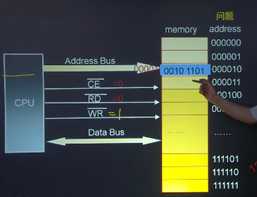

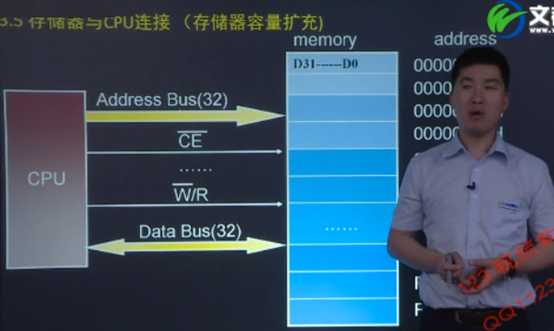

Address bus 地址总线

CE 片选信号(横线表示低电平有效)

RD 读(横线表示低电平有效)

WR 写(横线表示低电平有效)

Data bus 数据总线

cpu通过地址总线把地址发过去

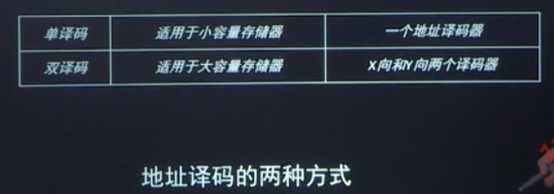

存储地址译码小结:

地址译码器:

将二进制代码标识的地址转换成输出端的高电位用来驱动相应的读写电路,以便选择所要访问的存储单元。地址译码有两种方式,单译码方式和双译码方式。

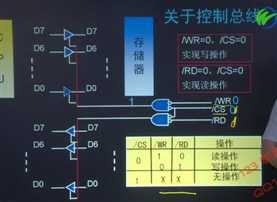

存储器的读写操作

存储器的存取仅仅与存储器的地址有关但是实际中还与其它的控制信号有关。与存储器有关的控制信号还有/cs(片选信号),/WR(写信号),/RD(读信号)。当/CS=1时标识本芯片没有被选中,对该芯片即不实现读操作也不实现写操作。

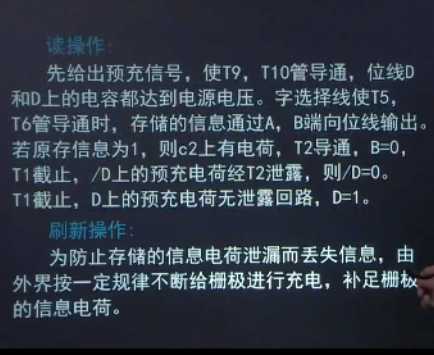

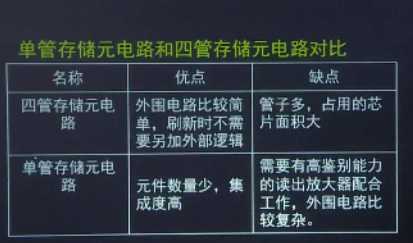

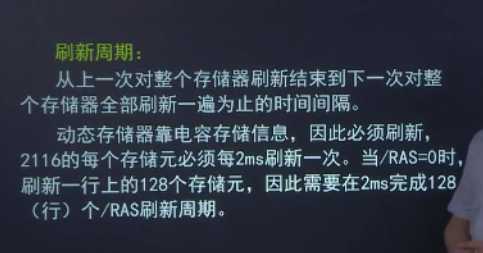

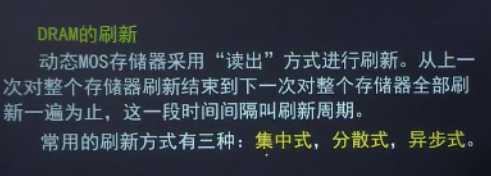

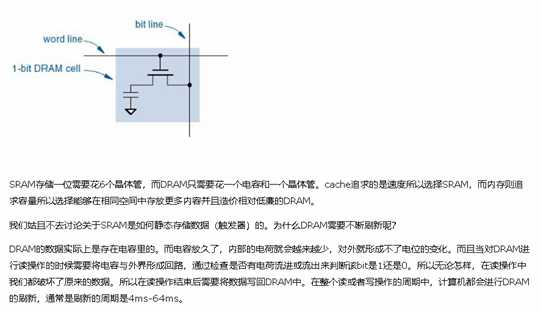

DRAM存储元

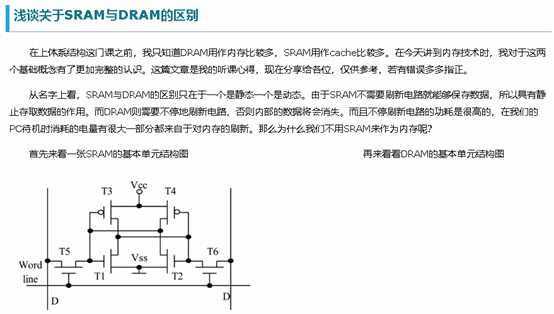

四管的动态存储电路时将六管静态存储元电路中的负载管T3,T4去掉而成的。

3.4 只读存储器和闪速存储器

3.4.1只读存储器

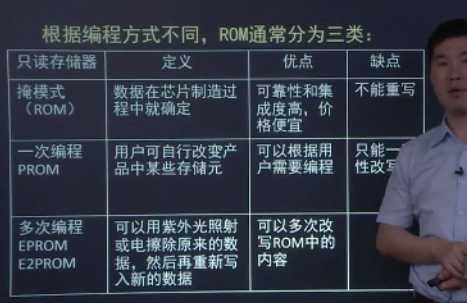

ROM的分类 只读存储器简称ROM,它只能读出,不能写入,最大优点具有不易失性

1) 掩模式ROM

掩模式ROM由芯片制造商再制造时写入内容,以后只能读而不能再写入。其基本存储原理是以原件的“有/无”来标识该存储但元的信息(1或0)可以用二极管或晶体管作为元件,显而易见,其存储内容是不会改变的。

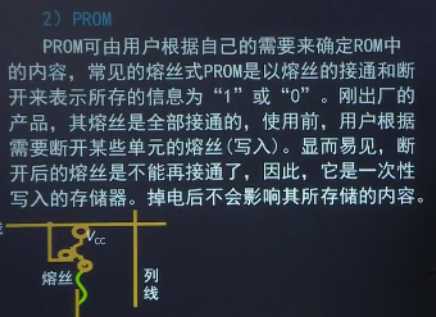

2) PROM

3,4,2闪速存储器

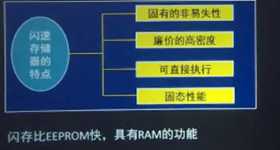

什么是闪速存储器

闪速存储器是一种高密度、非易失性的读/写半导体,它突破了传统的存储器体系,改善了现有存储器的结构。

*关于SRAM与DRAM

3.6双端口与多模块存储器

3.6.1双端口存储器

1.双端口存储器的逻辑结构

双端口存储器是指同一个存储器具有量足相互独立的读写控制线路,是一种告诉工作的存储器。

它提供了两个相互独立的端口,即左端口右端口,它们分别具有各自的地址线、数据线和控制线,可以对存储器中任何位置上的数据进行独立的存取操作。可以实现一个存储器挂接两个CPU。

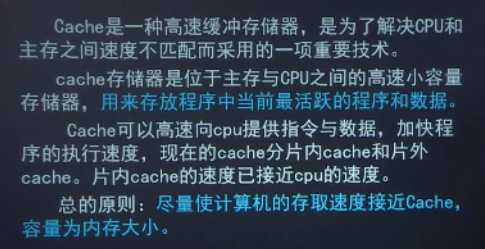

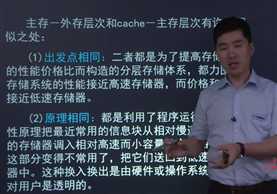

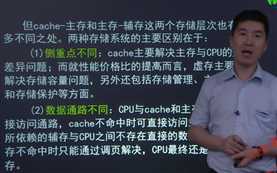

3.6 cache存储器

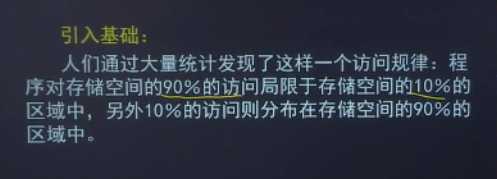

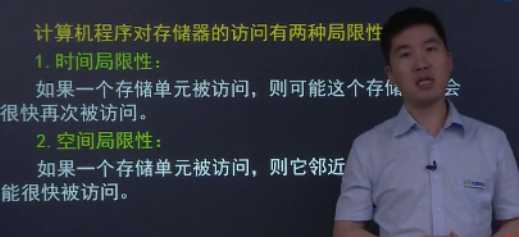

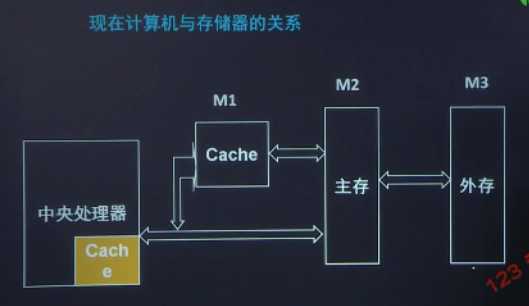

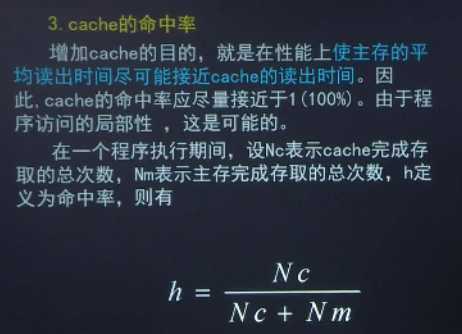

早期的计算机只有贮存和外存,没有cache,因为cpu速度不断提高,为了满足cpu与存储器之间的速度差异,采用cache技术

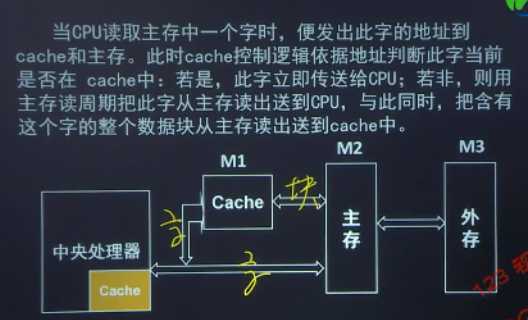

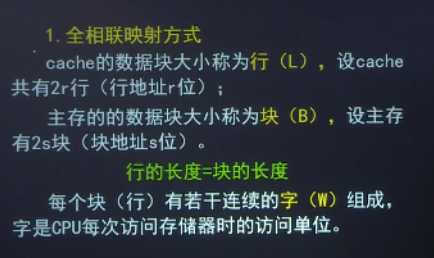

CPU与cache之间的数据交换是以字为单位的。

而cache与贮存之间的数据交换是以块为单位一个块由若干定长字组成的。

数据块(chunk)

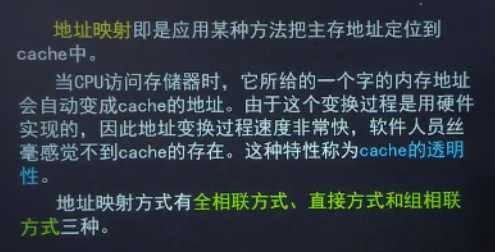

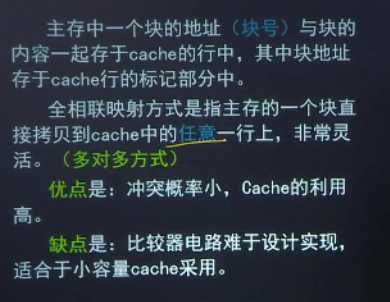

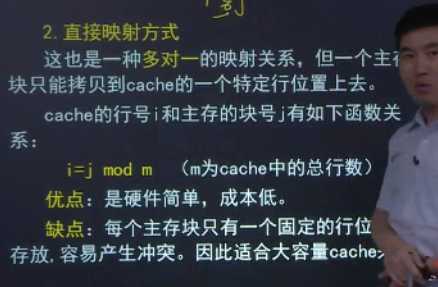

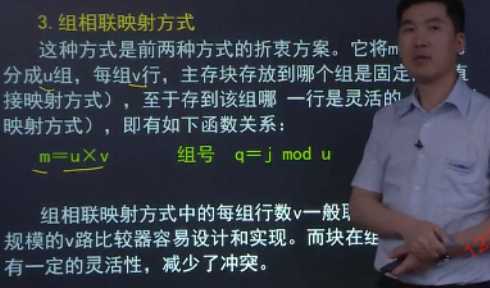

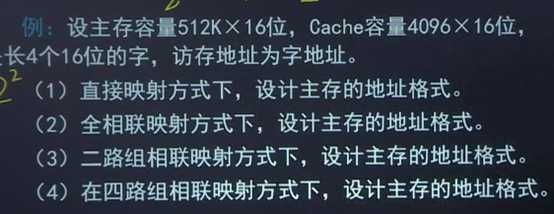

3.6.2主存与cache的地址映射

cache的容量很小,它保存的内容只是主存内容的一个子集,且cache与主存的数据交换是以块为单位。

问题:指令对存储器进行读写时,指令中的地址是内存系统中的存储器地址还是cache地址?

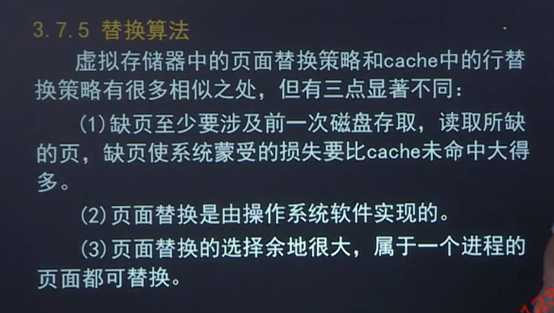

3.6.3替换策略

cache工作原理要求它尽量保存最新数据,必然存在将游泳的信息从贮存调进cache中,这样九产生替换。

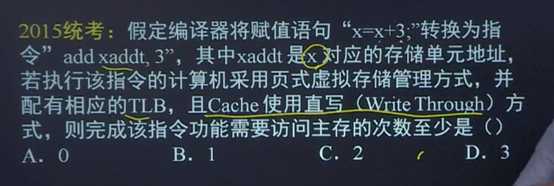

常见考题:

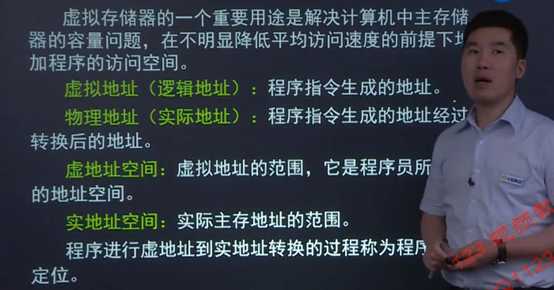

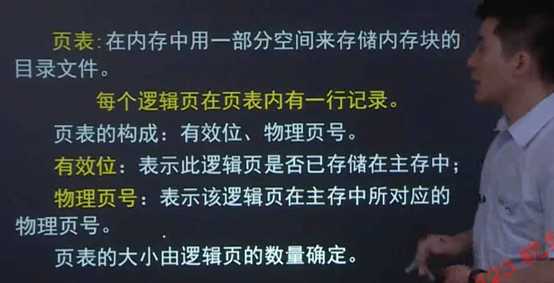

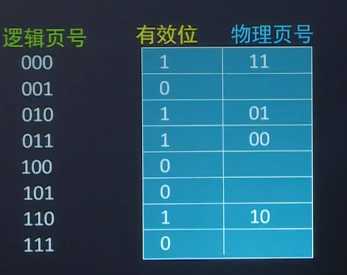

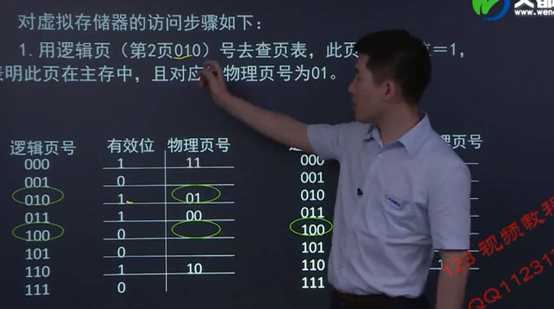

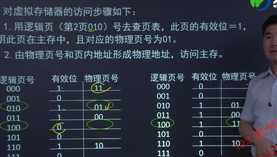

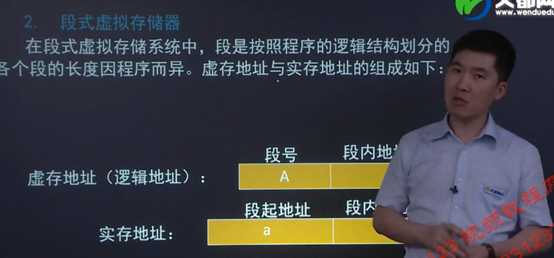

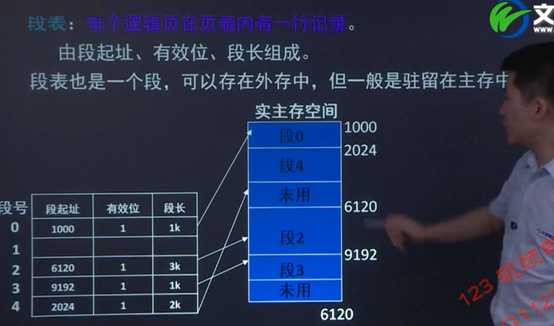

3.7虚拟存储器

3.7.1 虚拟存储器的基本概念

虚拟存储器只是一个容量非常大的存储器的逻辑模型,不是任何实际的物理存储器。

它借助于磁盘等辅助存储器来扩大主存容量,使之成为更大或更多的程序所使用。

它指的是主存-外存层次。以透明的方式给用户提供了一个比实际主存空间大得多的程序地址空间。

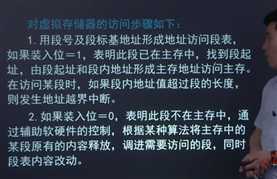

虚拟地址的访问的过程:

侧重点不同: 一个是解决CPU访问速度不匹配。另一个是解决空间不足的问题。

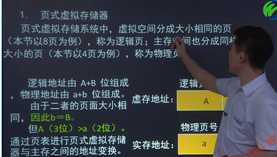

3.7.2主存-外存层次的基本信息传送单位

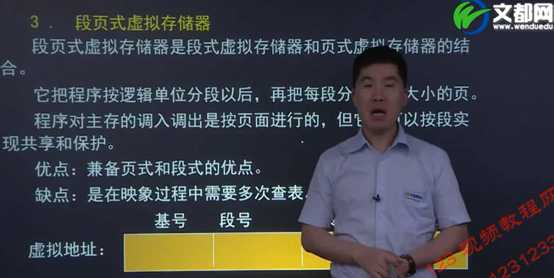

主存-外存层次的基本信息传送单位可采用几种不同的方案:段、页或段页。

骚操作:

标签:ESS 控制线 物理 有关 查询 多模块 技术分享 数据 3.4

原文地址:https://www.cnblogs.com/eret9616/p/9278180.html