标签:mod str 提高 alt 可见 控制器 缓存控制 info 使用

1.为什么要有缓存?

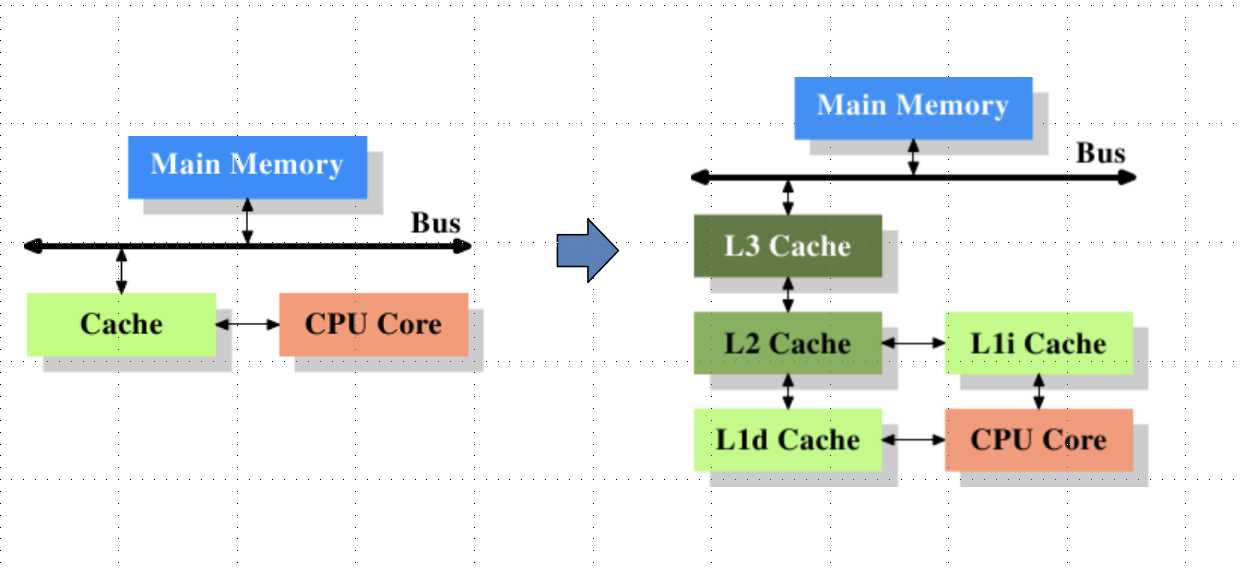

随着现代半导体工艺的发展,CPU的频率越来越快,相对内存快了一个数量级,对于访存的操作CPU就需要等待主存,这样会导致资源的白白浪费。所以cache的出现为了解决CPU与内存速度不匹配的问题。(cpu ->cache->memory)

cache的思想在我们日常的生活随处可见,我们周围的超市就是很好的例子。工厂把我们日常用品部分在超市,减少了我们去工厂购买的时间开销,方便了我们的生活。

2.CPU缓存有什么意义?

时间局部性:如果某个数据被访问,它在将来的某个时间也有可能在被访问。

空间局限性:如果某个数据被访问,那么它相邻的数据也有可能被访问。

3.CPU读取数据的过程

cache中保存着cpu刚用过的数据或者是循环使用的数据,这时,从cache中读取数据就会很快,减少了cpu等待的时间,提高了系统的性能

4.cache 缓存带来的问题

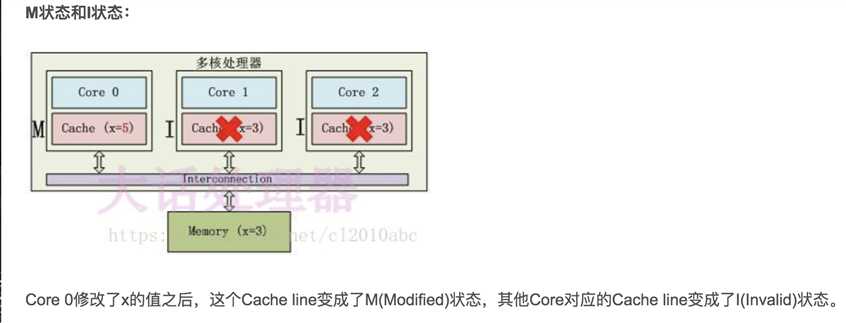

导致数据不一致的问题,对于多核系统来说。

5.如何解决缓存带来的问题,比较常见的缓存一致性(MESI),当然也有锁住总线。

我们来介绍一下缓存一致性:

在MESI协议中,每个cache line有4个状态,可用2个bit表示,它们分别是:

| 状态 | 描述 |

|---|---|

| M(Modified) | 这行数据有效,数据被修改了,和内存中的数据不一致,数据只存在于本Cache中。 |

| E(Exclusive) | 这行数据有效,数据和内存中的数据一致,数据只存在于本Cache中。 |

| S(Shared) | 这行数据有效,数据和内存中的数据一致,数据存在于很多Cache中。 |

| I(Invalid) | 这行数据无效 |

MESI为了保证多个CPU缓存中共享数据的一致性,定义了cache line的四种状态,而CPU对cache line的四种操作可能会产生不一致的状态,因此缓存控制器监听到本地操作和远程操作的时候,需要对地址一致的cache line 状态进行一致性修改,从而保证数据在多个缓存之间保持一致性(M:modified E:Exclusive S:shared I:invalid) 。

3个Core都访问变量x,它们对应的Cache line为S(Shared)状态

标签:mod str 提高 alt 可见 控制器 缓存控制 info 使用

原文地址:https://www.cnblogs.com/caibixiang123/p/9326714.html