标签:lse 关于 inpu 一个 esc com info ide 异步

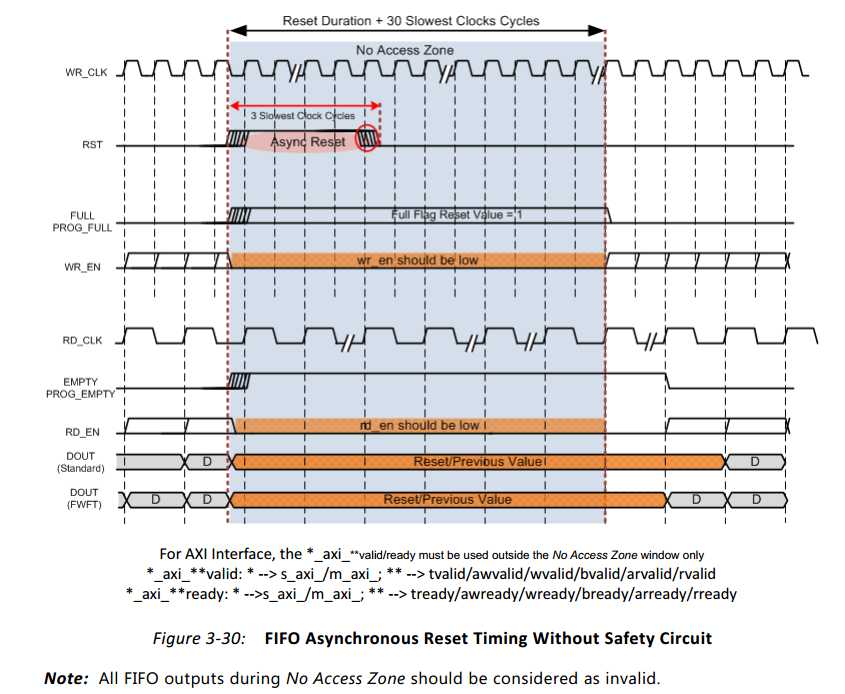

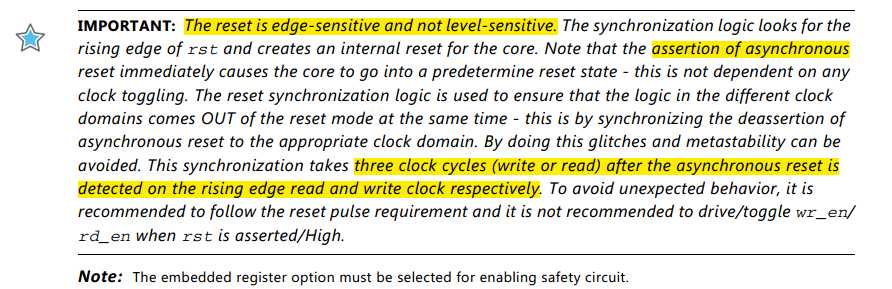

关于FIFO异步复位的问题

FIFO异步复位的宽度,需要保证至少3个较慢时钟的时钟周期长度。

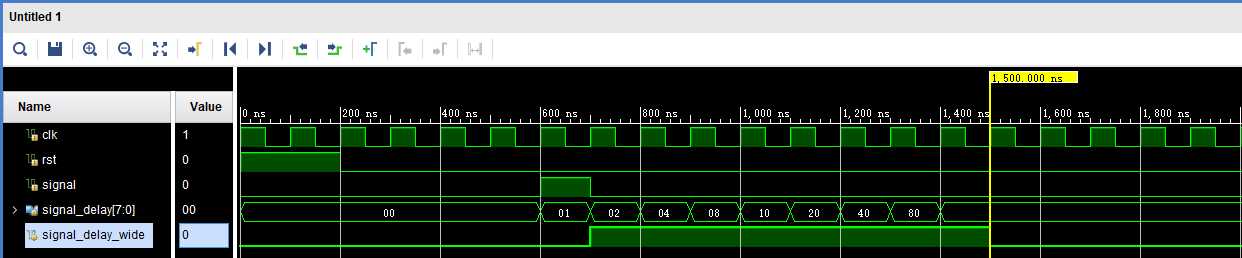

怎样对一个脉冲加宽呢?

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 2018/08/08 19:03:20 // Design Name: // Module Name: signal_wide // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module signal_wide( input wire clk, input wire rst, input wire signal ); reg [7:0] signal_delay = 0; reg signal_delay_wide = 0; always @ (posedge clk or posedge rst) begin if(rst) begin signal_delay <= 8‘b0; signal_delay_wide <= 1‘b0; end else begin signal_delay <= {signal_delay[6:0],signal}; signal_delay_wide <= | signal_delay; end end endmodule /* add_force {/signal_wide/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps add_force {/signal_wide/rst} -radix hex {1 0ns} {0 200ns} add_force {/signal_wide/signal} -radix hex {0 0ns} {1 600ns} {0 700ns} */

标签:lse 关于 inpu 一个 esc com info ide 异步

原文地址:https://www.cnblogs.com/chensimin1990/p/9448098.html