标签:摄像头 图片截取 bubuko bit 传输 时序图 行数据 工作 关注

目前FPGA用于图像采集 传输 处理 显示应用越来越多,主要原因是图像处理领域的火热以及FPGA强大的并行处理能力。本文以OV7725为例,对摄像头使用方面的基础知识做个小的总结,为后续做个铺垫。

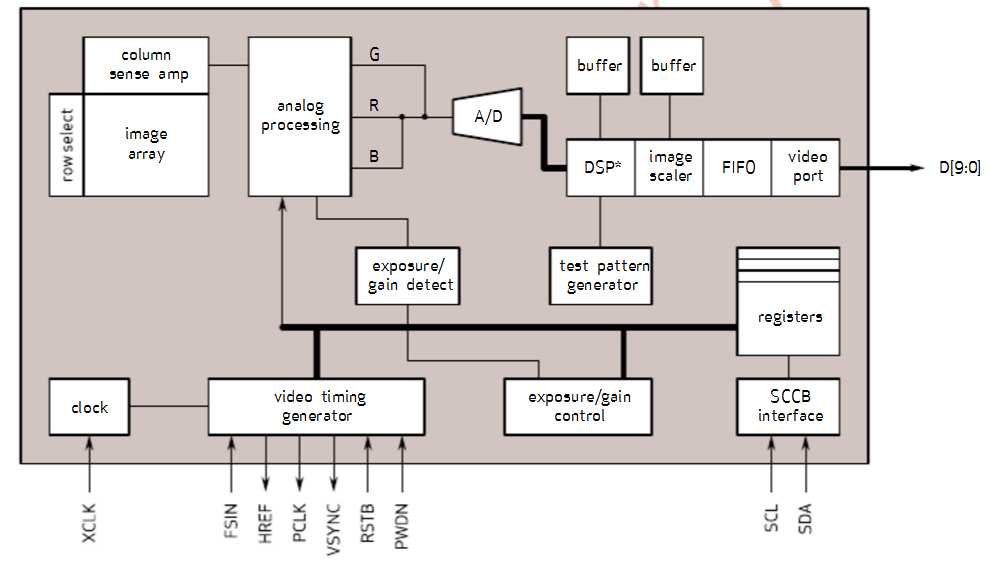

下图是OV7725 datasheet中摄像头传感器内部结构视图,我们主要关注用户接口。

XCLK:工作时钟输入,由主控器产生,频率为24MHz;

HREF:行参考信号输出;

PCLK:像素时钟输出,由XCLK产生,用于控制器采样图像数据;

VSYNC:场同步信号输出;

RSTB:复位输入,低电平有效;

PWDN:低功耗模式选择输入,正常工作期间需拉低;

SCL:SCCB管理接口时钟,最高频率400KHz;

SDA:SCCB接口串行数据总线;

D[9:0] 像素数据输出;

此处SCCB总线与IIC总线非常相近,帧结构不同但一个phase内的时序基本一致,故多数图像采集系统直接复用IIC控制器对图像传感器内部寄存器进行配置。具体见参考文献2。总结来说,SCCB与IIC的主要区别在以下两点:

1 IIC有重复开始的概念,读操作先写设备地址 再写寄存器地址,然后重新开始,写设备地址,读取数据。而SCCB读操作时在第一次写寄存器地址后必须有结束条件。

2 IIC主机写数据到从机时,从机必须在写8bit下一时钟拉低总线响应主机。IIC主机读取从机数据时,多字节连续读取除最后字节主句均在第9时钟周期拉低总线响应,单字节读取拉高总线便于下一拍提供停止条件。而SCCB每个phase第9bit为don‘t care bit /NACK,主机写从机第9bit不关心,读取从机数据由于不支持多字节操作第9bit主机必须拉高总线。

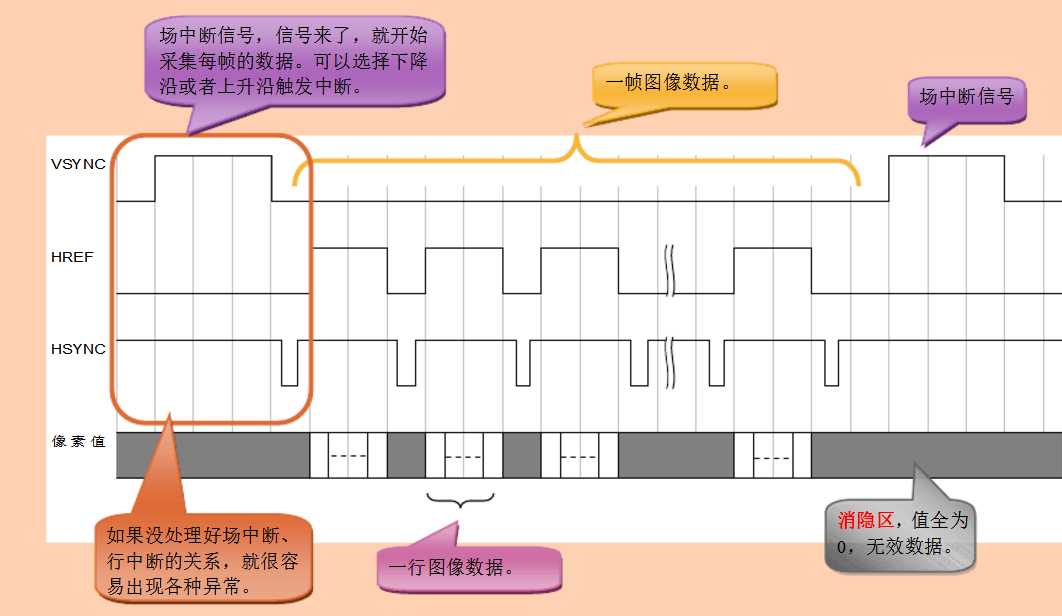

接下来从整体上把握输出图像数据与同步信号的关系。(图片截取自《OV7725摄像头编程基本知识笔记》,见参考文献3.

两个VSYNC高脉冲之间为包含一帧图像数据,但只有HREF高电平期间数据才为有效数据,每个HREF高电平区间对应一行图像数据。因此通过这两个信号即可找到有效的图像数据。OV7725摄像头支持多种图像输出格式,此处阐述常用的RGB565格式:

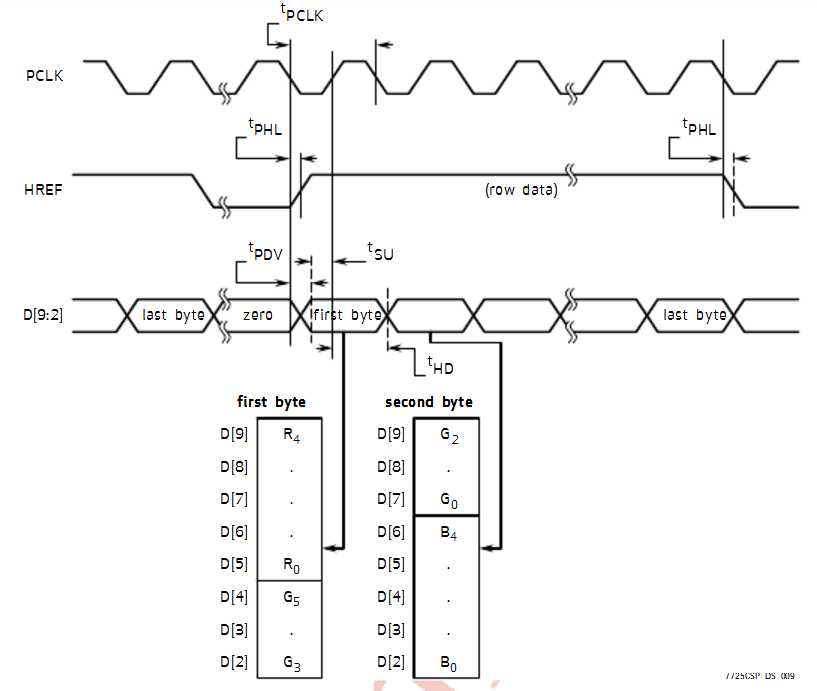

图像数据在PCLK下降沿输出,控制器在其上升沿采样。当选择此模式输入时,仅使用数据线高八位。时序图给出了相邻两个字节数据内容,可见两个字节表示一个像素点数据,从高位到低位依次是:R 5bit,G 6bit,B 5bit。Ov7725图像传感器的像素30万,分辨率:640*480,即每行640个有效像素点,一共480行。所以每个HREF高脉冲期间有640*2个PCLK周期,两个VSYNC高脉冲期间循环480次。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

参考文献:

1 ov7725手册(可注释)_图文_百度文库 https://wenku.baidu.com/view/3e5504004431b90d6c85c764.html

2 OV7725学习之SCCB协议(一) - aslmer - 博客园 https://www.cnblogs.com/aslmer/p/5965229.html

3 ov7725数字摄像头编程基本知识笔记_图文_百度文库 https://wenku.baidu.com/view/d1af7a731711cc7931b716c6.html

标签:摄像头 图片截取 bubuko bit 传输 时序图 行数据 工作 关注

原文地址:https://www.cnblogs.com/moluoqishi/p/9457069.html