标签:参数 检测 最大 clock 位置 指示 应该 strong date

SCDC State and Control Data Channel

接收端如果有SCDC,应该在E-EDID中包含一个有效的HF-VSDB,并且把SCDC_Present位设置为1。在访问SCDC之前,源端必须验证接收端E-EDID中,包含一个有效的HF-VSDB并且SCDC_Present位要设置为1,否则源端不能访问SCDC。

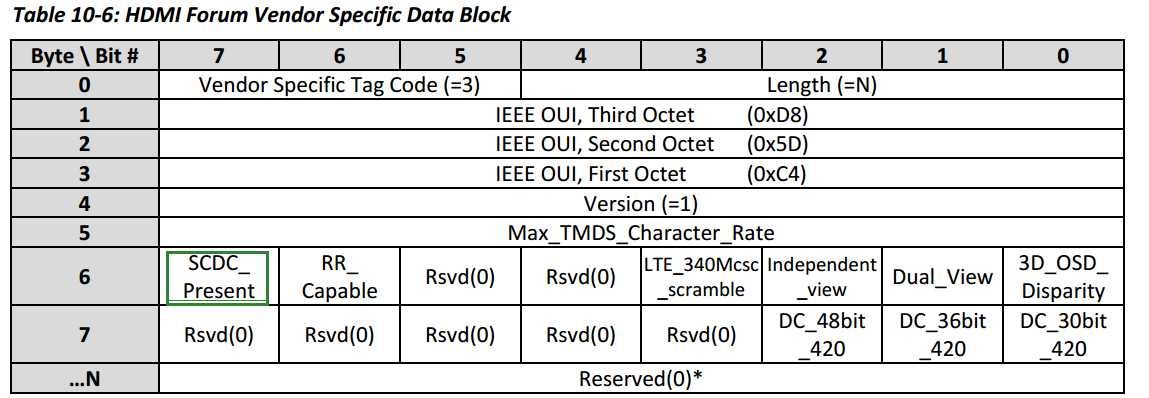

HF-VSDB在H2.0中定义,用于指示宿端支持的H2.0中定义的特性。HF-VDSB与H1.4b中定义的VSDB是有区别的。HF-VDSB不能取代VDSB,它们都是Vendor Specific Data Block

在E-EDID中是否要支持HF-VDSB是可选的,除非支持Table10-5(H2.0)的特征。如果包含的话,HF-VSDB应该位于宿端E-EDID中CEA 扩展版本3,在E-EDID中紧随H14b VSDB。下图是H2.0中Table10-6,它定义了HF-VDSB

在程序中,SCDC主要用于源端更新宿端TMDS_Bit_Clock_Ratio和Scrambler_Enable寄存器位,并且在这个版本中不支持HDMI RX对SCDC的读请求。

SCDC_Present[1bit] = 1,宿端支持SCDC功能

= 0,宿端不支持SCDC功能

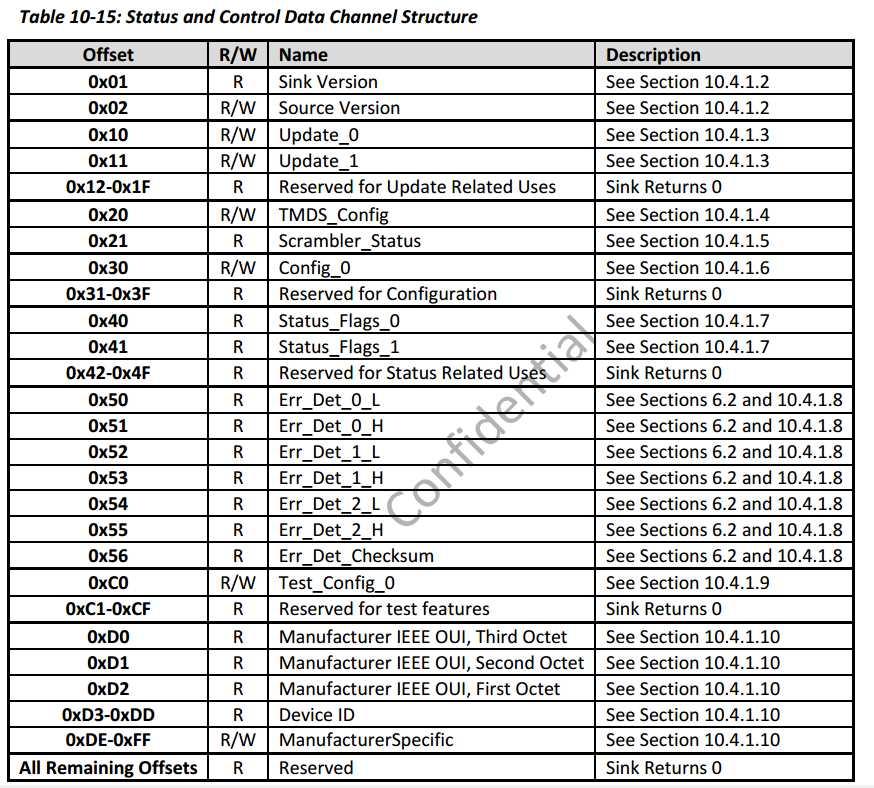

以下HDMI Specification 2.0 中的对应的寄存器及地址参数

按照版本2.0,接收端版本应该是1

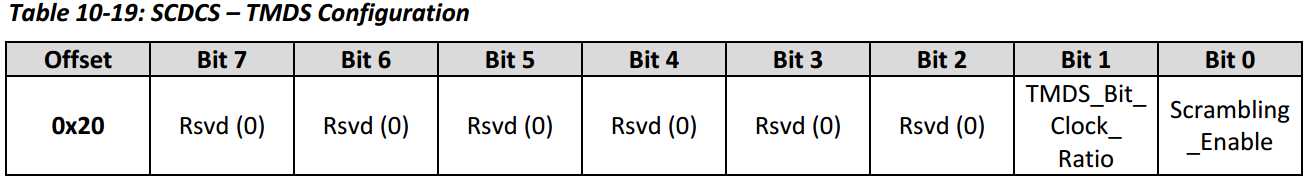

Table10-19:SCDC—TMDS Configuration

Scrambling_Enable:=1,源端设置该位为1使能宿端加扰

=0,源端设置该位为0,禁止宿端加扰

TMDS_Bit_Clock_Ratio:=0,(TMDS Bit Period)/ (TMDS Clock Period) = 1/10

=1, (TMDS Bit Period) / ( TMDS Clock Period) = 1/40

当宿端支持的TMDS位速率大于3.4Gbps时,就要提供TMDS_Bit_Clock_Ratio控制位。如果TMDS位速率小于3.4Gpbs,源端要设置TMDS_Bit_Clock_Ratio = 0,TMDS 时钟和数据信号要遵从HDMI1.4b。当TMDS位速率在3.4~6.0Gbps时,源端要设置TMDS_Bit_Clock_Ratio = 1,此时TMDS的时钟和数据信号要遵从HDMI2.0的6.1.1.4。设置之后源端可以读取Clock_Detected状态位来确保宿端接收到了传输的TMDS_Bit_Clock_Ratio设置。

源端修改宿端的TMDS_Bit_Clock_Ratio位的操作步骤:

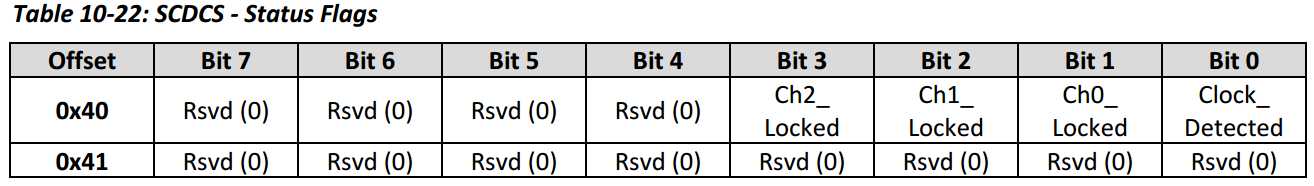

Clock_Detected:当宿端接收到有效的时钟信号时该位置1,反之置0

Ch0_Locked:当宿端在通道0上成功解码出数据时该位置高,反之置0.

数据传输协议

SCDC 的I2C从机地址是0xA8/0xA9

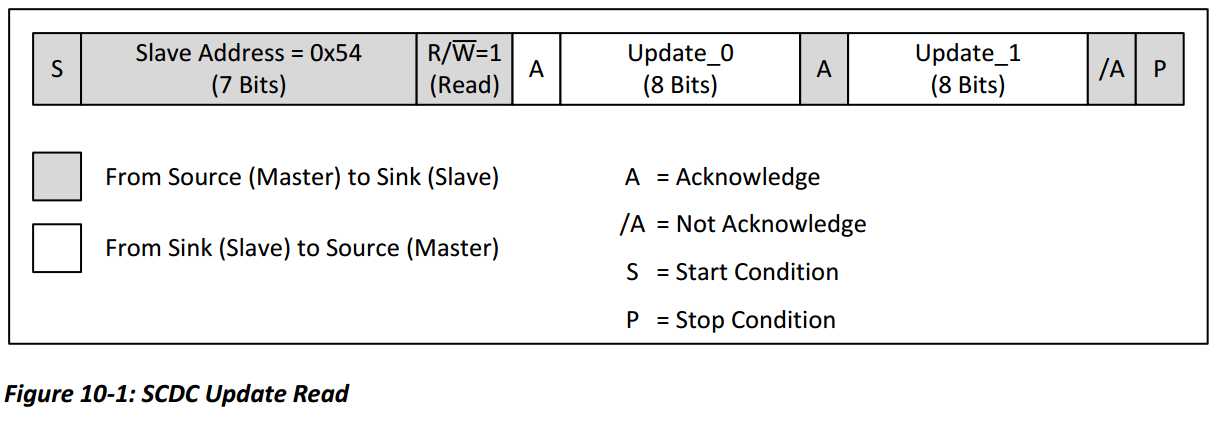

(1) 读update flags

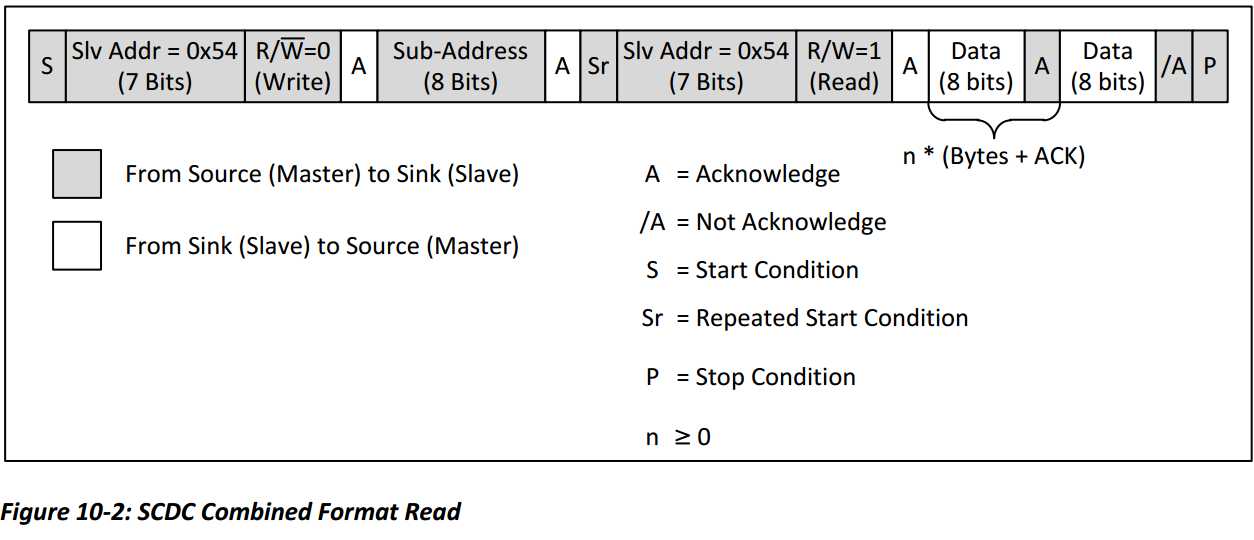

(2) 读其余数据

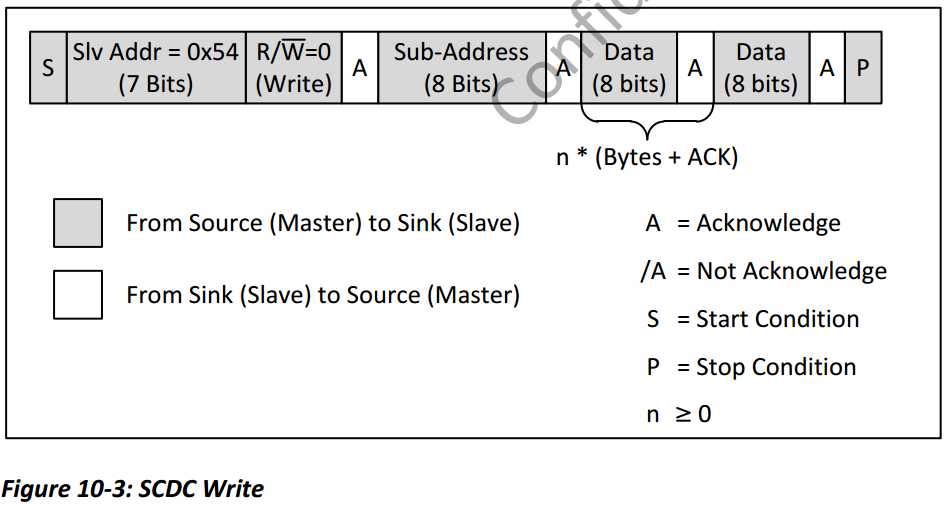

(3) 写操作

上面的程序对应一个地址为0Xa8,先看下在HDMI Specification2.0【10.4.3 Data Transfer Protocols】中的说明:

HDMI Specification2.0对SCDC(Satus and Control Data Channel)的参数进行了详细的讲述。

标签:参数 检测 最大 clock 位置 指示 应该 strong date

原文地址:https://www.cnblogs.com/zhongguo135/p/9458882.html