标签:方向 ima fun efault uil coding 错误 case 报错

1.clocking后面要跟紧标签,clocking里面的input/output方向与DUT相反,并且不能有位宽标识。

2.factory的注册语句后面不要加;用来结束,constraint后面也是不用加;,避免不必要的warning。

3.function如果不需要返回值,声明时加入void,在实际的处理中也要加上void,要匹配不然报错。

4.实例化fifo的port一定要xxx=new("xxx",this);不然直接用xxx=new()报错。所以基本上实例化都要用前一种,避免debug带来困扰。

5.task和function的区别:task可以有仿真时间的概念,可以使用@(posedge...),但是赋值必须用=;function没有仿真时间的概念,赋值可以用<=,=用<=表示下一个周期。

因此,在phase中,build_phase和connect_phase是不包含在仿真时间里的,因此其定义是function。而main_phase等可以有仿真时间的,定义是task。需要注意的是在driver中与DUT进行端口连接的功能应该使用function 使用<=赋值。

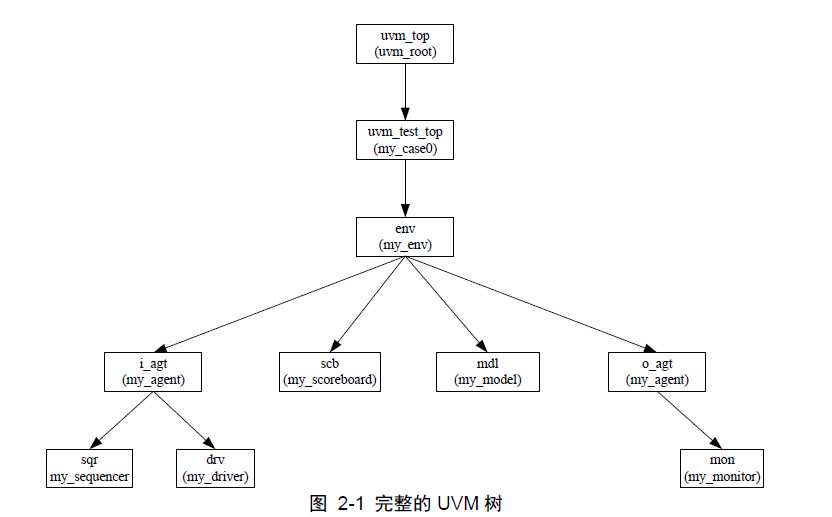

6.关于function new,object类的new只有一个name参数,component类有一个name和一个parent。name = “实例化的名字” parent表示UVM树形的某一个层次,有些class定义的时候这个new的参数可以使用默认的,有些不能。

这个如何判断有些用 new(name,uvm_component parent) 有些用new(name = " ",uvm_component = "null") ?

在这个uvm树中,env下一层的agent scb mdl都要写出具体的实例化名字,parent是null,表示其没有父类(从object继承过来的更要求这样,否则没法看到树形结构);

其他的使用默认,表示其父类就是声明的class。

7.一般通过define来选择是否打印model/scb/等模块的信息,这些信息有利于debug环境,但是会消耗仿真时间,所以要做一个开关。

`define mdl_info(info) `uvm_info("xx_model",info,UVM_MEDIUM)

实际引用只需调用mdl_info即可,可以加上$psprintf打印一些变量的信息。

8.sequence设定一个default sequence,在不同case下面如果要用其他的sequnence,在case下把sequence进行替换即可。

9.合理利用typedef来自己定义想要的数据结构会事半功倍,其次要先想清楚自己的验证环境的结构,然后思路实现的方法,model的实现等。具体化~

10.sv的数据结构比verilog丰富许多,实现的方法偏向软件化,因此思路应与设计的思路有所区分。

11.transaction的定义,要考虑的是model/rtl需要什么样的数据,scoreboard的判定又需要什么样的数据。所以其实写验证环境最重要的还是理解整个环境的各个部分的数据交互,

清楚了数据流,就清楚了整个结构,写起来也就很快了。

标签:方向 ima fun efault uil coding 错误 case 报错

原文地址:https://www.cnblogs.com/rongmouzhang/p/9480488.html