标签:接收机 _id des 常用 分享图片 targe https nbsp target

2018-08-23 22:11:31

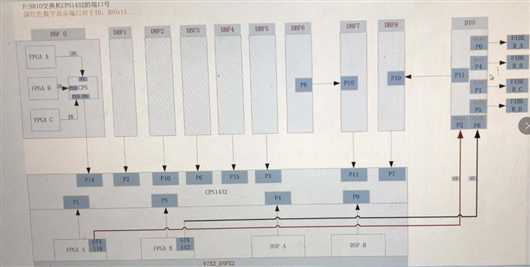

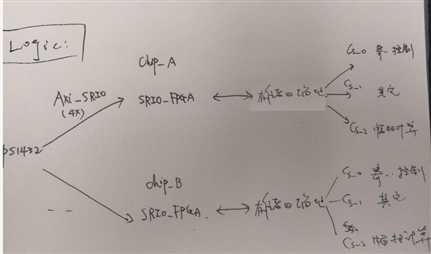

DSP可以直接与FPGA通信,但通常用一个DSP控制多个芯片器件,这个时候需要借助交换机网络。

主要的参数配置,在DSP中完成,例如接收机中的信道化控制:

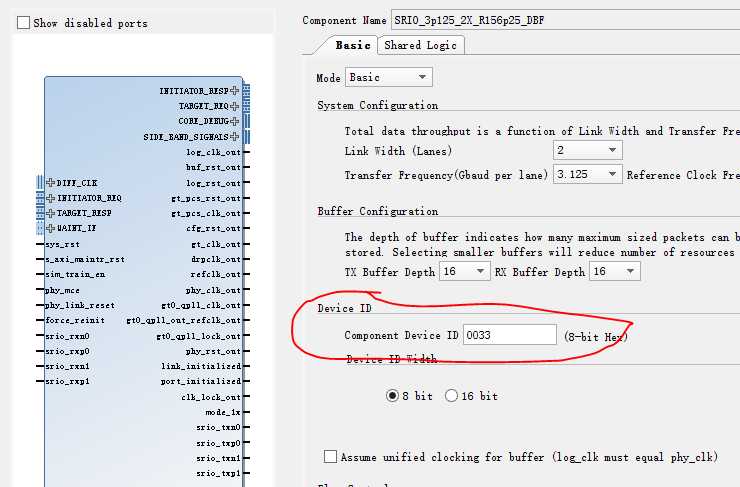

FPGA的IP核配置参考文档:pg007.pdf

if(clkmain_rst)begin

dest_id <= 16‘h0011; //DSP

end else begin

if(xcorrrdy)begin

dest_id <= 16‘h0011; //DSP

end

if(reqlock)begin

dest_id <= 16‘h0039; //邻片

end

end

对应IP核注意修改地址:

正常IP核生成后,generate example生成两个文件,request_generate(收DSP数据), request_check(发给DSP数据)

部门熟悉配置的人员:WL、ZRQ,以后用到再向他们学习。

标签:接收机 _id des 常用 分享图片 targe https nbsp target

原文地址:https://www.cnblogs.com/mia1004/p/9526937.html