标签:href src 实践 ash tags htm ext lan 技术

上一篇文章学习了总线的相关知识,途中ABC当时假设为一个个的8位寄存器。这一篇要学习怎么构建这个寄存器。

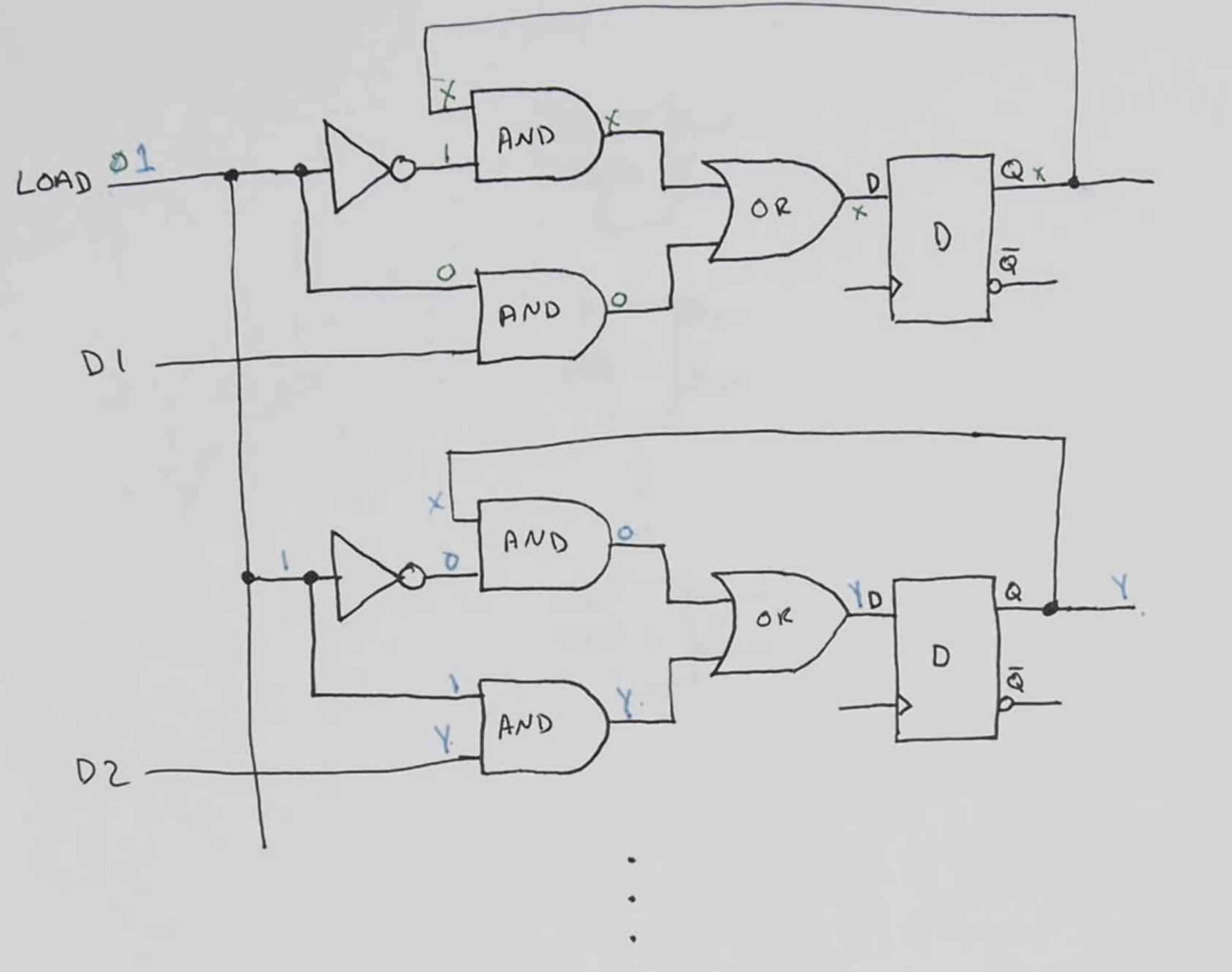

这分为两个三个部分,数据输入,寄存器,数据输出。首先不管输出,来看数据输入和寄存器这两个部分。【03触发器与锁存器】中讲了D型触发器,那么我们的寄存器(D寄存器)就由D锁存器(74LS74)构成,结构如下:

图中画了2位的寄存器,每一个部分就是一个1位的寄存器,如果一共8位的话就需要8个这样的1位寄存器。load端为0,那么数据端不论是多少,输出端Q都不会改变。如果load端为1,当时钟上沿时,Q就会保存D传入的数据。图中上面的寄存器拿load为0举例,下面的是load为1。实际搭建的图如下:

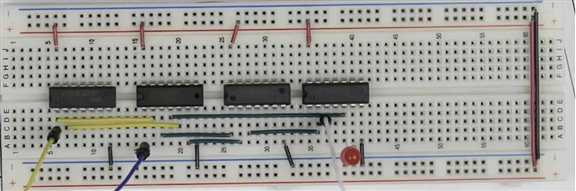

中间四个数字电路分别为 74LS04(反相器),74LS08(与门),74LS32(或门),74LS74(D型锁存器)。黄线为load,蓝线为数据data,白线为时钟clk,可以连接到之前用555定时器做的pc上。实验到时候可以把黄线接在+或者-,表示load到0和1。这是你会看到灯泡(寄存器的数据),会随着clk,相应的根据load的值,存储或无视蓝线data的值。

这样一个1位寄存器的输入和寄存就做完了,还差输出端。蓝线只需要接入到总线上,就能收到来自总线的数据了,但把数据输出到总线,需要做些处理,需要连接一个三态双向总线收发器。这个在【05总线】这一篇中由讲过为什么。

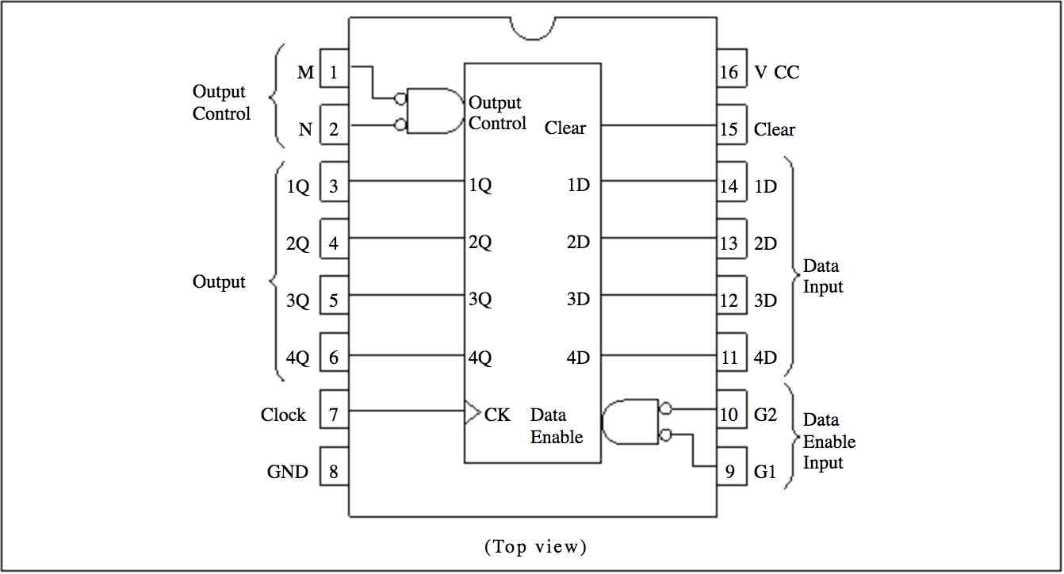

整合:至此我们了解了一个1位的寄存器从输入到输出的制作,8位的话则需要8个这样的组合。这里我们可以直接用两个 4bit D-type registers with 3-state outputs(74LS173)即可。顾名思义,即3态输出端的4位D型寄存器集成电路。这里要说明一下,虽然我们要亲手做cpu,但改方便时要方便。我们当然不能方便到直接用一个8086放在面包板上就算做了个cpu,可当然也不能全用基本门电路,甚至用二三极管和电容做cpu,我们要找一个折中到办法,在了解到原理,但重复度比较高的零件,就尽量用即成的。下图位74LS173针脚图:

这里引入官方说明:

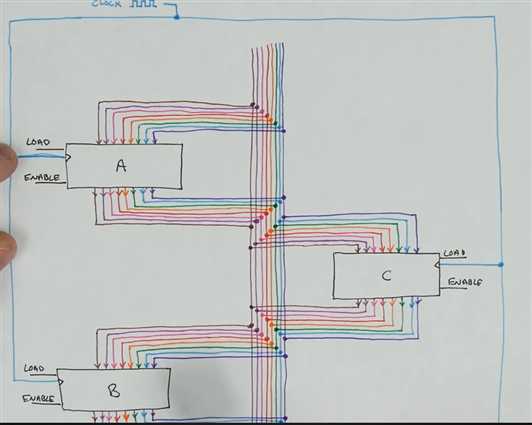

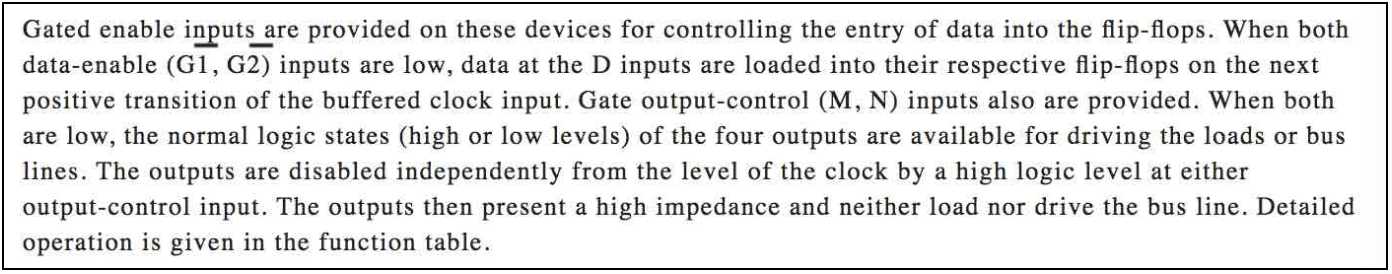

这样两个74LS173就组成了一个8位寄存器,包含输入和输出端的控制。由于实践中设计的cpu需要直观看到寄存器里的内容,所以不管输出到总线的控制信号如何,我们都希望能够通过LED灯来观察寄存器里的内容。所以我们使74LS173的输出端控制始终为可输出,连接到LED灯上,再在后面接一个74LS245(三态控制)来控制信号是否输出到总线。设计图如下:

其中M,N始终接地,即低电平有效,输出端一直有效,通过LED灯后再进行三态输出处理。

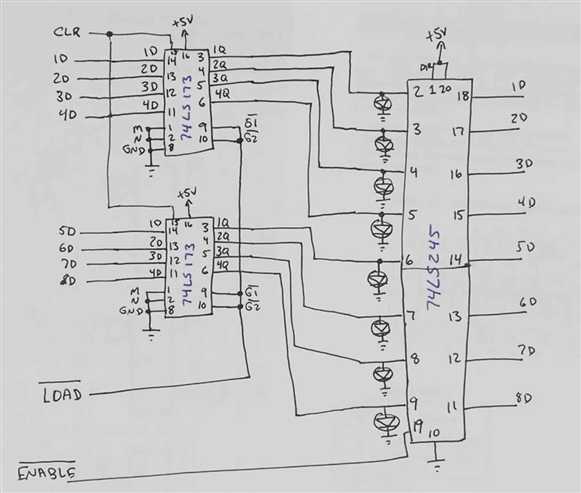

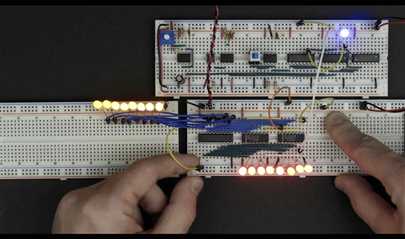

实操图第一步:

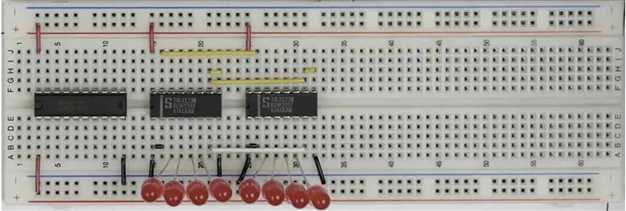

实操图第二步:寄存器输出端连接到三态上,三态的输出端连接到总线。总线又通过蓝线连接到寄存器到输入端,还有三根黄线,最右边是load(数据是否存入),中间是clear(永远0),左边是三态的允许(是否输出到总线)。白线是clk。

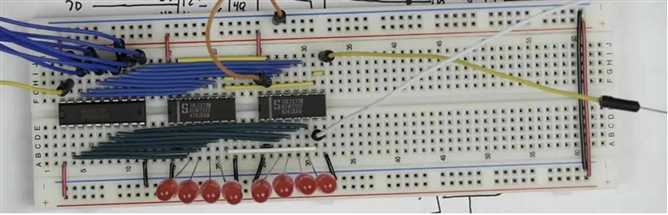

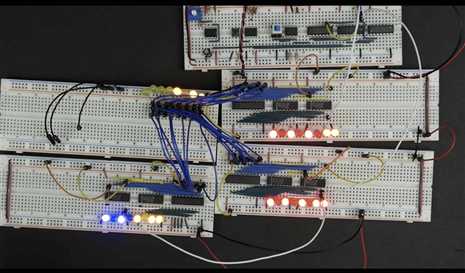

将设备连接到pc和总线上:

连接多个寄存器:

总结:至此多个寄存器已经可以和总线交互,并且连接到了pc上,随着时钟到改变,通过load和三态决定是否载入和输出数据。

参考视频:eater.net

标签:href src 实践 ash tags htm ext lan 技术

原文地址:https://www.cnblogs.com/flashsun/p/9579641.html