标签:运行 ruby city list 技术 cti marker libc 模型

概念辨析-Description Language还是Description Library?

Verilog, standardized as IEEE 1364, is a hardware description language (HDL) used to model electronic systems.

可以看到Verilog是Language。同样,VHDL和SystemVerilog也是。

Chisel虽然嵌于Scala,但只用了一个很小的子集,并且与正常的Scala写法也有很大的区别。再者,Chisel: Constructing Hardware in a Scala Embedded Language,也表明了是嵌于Scala的语言,而非独立的语言。

Language之所以成为Language是因为其独特的语法,如关键字和语法结构。

比如VHDL、Verilog、SystemVerilog的关键字和提供的语法糖就有很大不同,表达效率也因此而异。

无论是什么language,其目的都是model electronic systems.

建模得到的只是模型,而非electromic systems本身。这也是HDL中D之所以是Description的原因。

任何语言都可以建模。

进而,任何语言都可以model electronic systems. 只是术业有专攻,各种擅长的领域不同。专有的Hardware Description Language或者Hardware Modeling Language,如VHDL, Verilog、SystemVerilog的表达效率高,模型较精确。

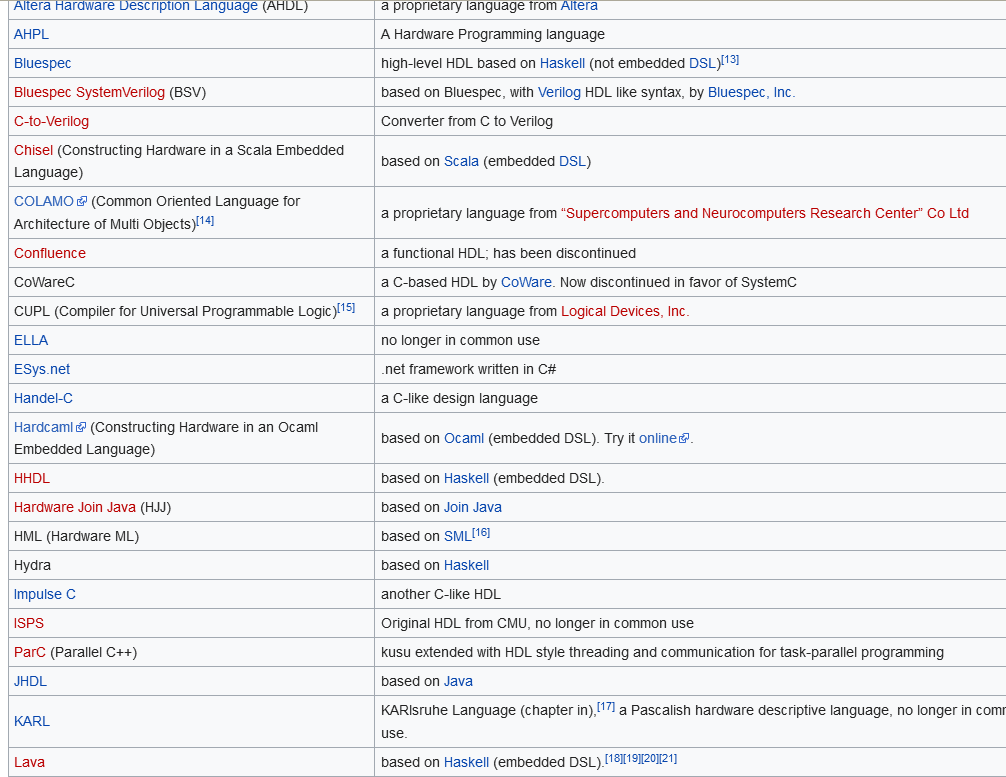

但不能否定,其他语言也可以model electronic systems. 如C,C++,C#, Python, Java, Haskell, Ruby等等。

? ?

?

使用其他语言建模硬件,则需要基于该语言针对硬件建模的库,即Library。Library则是基于某种语言的库,为语言提供某一个专业领域的基础能力。比如libc,glibc,就是C语言的运行时库;libc++是C++的运行时库。libssl是ssl的库,凡此种种。

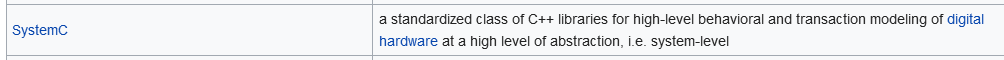

举个例子:SystemC(不甚了解):

? ?

?

总结一下,无论是Language还是Library都是用于model electronic systems. 只是Language是专用硬件建模语言,而Library则是基于现有语言,提供硬件建模能力。

概念辨析-Description Language还是Description Library?

标签:运行 ruby city list 技术 cti marker libc 模型

原文地址:https://www.cnblogs.com/wjcdx/p/9590366.html