标签:转换 复位 splay 分享图片 https ilo option load lin

用状态机思想编写的verilog代码生成状态机图会很方便检查和调试,quartus好像可以直接生成,ISE不行,需要用modelsim,步骤如下。

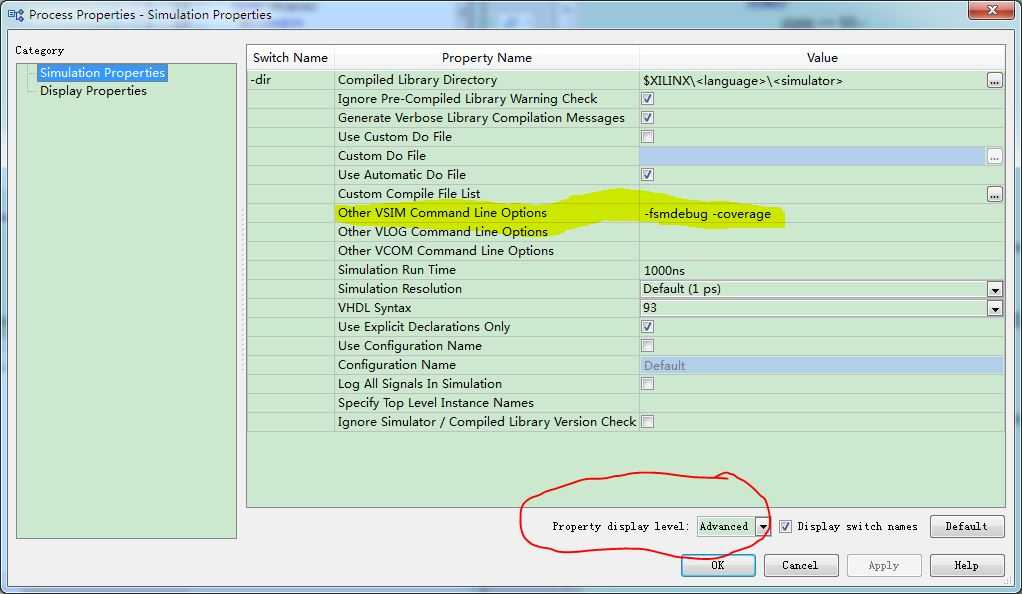

右键单击Simulate Behavioral Model,选择Process Properties。然后把Property display level改为Advanced,在Other VSIM Command Line Options下面,输入-fsmdebug –coverage这两个选项(务必输入,否则ModelSim无法产生FSM视图):

双击Simulate Behavioral Model,将打开ModelSim。

在ModelSim中执行View---FSM list命令,如下图所示:

然后就会发现ModelSim左边这部分的标签多了一项,如下面两幅图的对比:

未执行命令前是这样子的:

执行完命令是这样子的:

这时候在FSM List标签下,可以看到如下内容,双击之:

于是出现了下面的状态转换图:

这时观察生成的状态转换图发现,所有的状态都在复位的情况下返回了状态IDLE,这是我们不期望的,仔细观察这时的菜单栏可以发现,有一个FSM View项:

将Show Transitions to "Reset"项前面的对勾去掉,就会发现不显示复位情况下返回状态IDLE了,如下图所示:

参考资料:

https://blog.csdn.net/jbb0523/article/details/7932026

http://xilinx.eetrend.com/blog/7391

标签:转换 复位 splay 分享图片 https ilo option load lin

原文地址:https://www.cnblogs.com/zlll/p/9597678.html