标签:b2c init 调用 enc 解析 java intel git ilo

https://docs.qq.com/doc/DR2VaWXNxVFFEb3dw

https://github.com/wjcdx/jchdl/blob/master/src/org/jchdl/model/gsl/operator/conditional/Mux.java

? ?

?

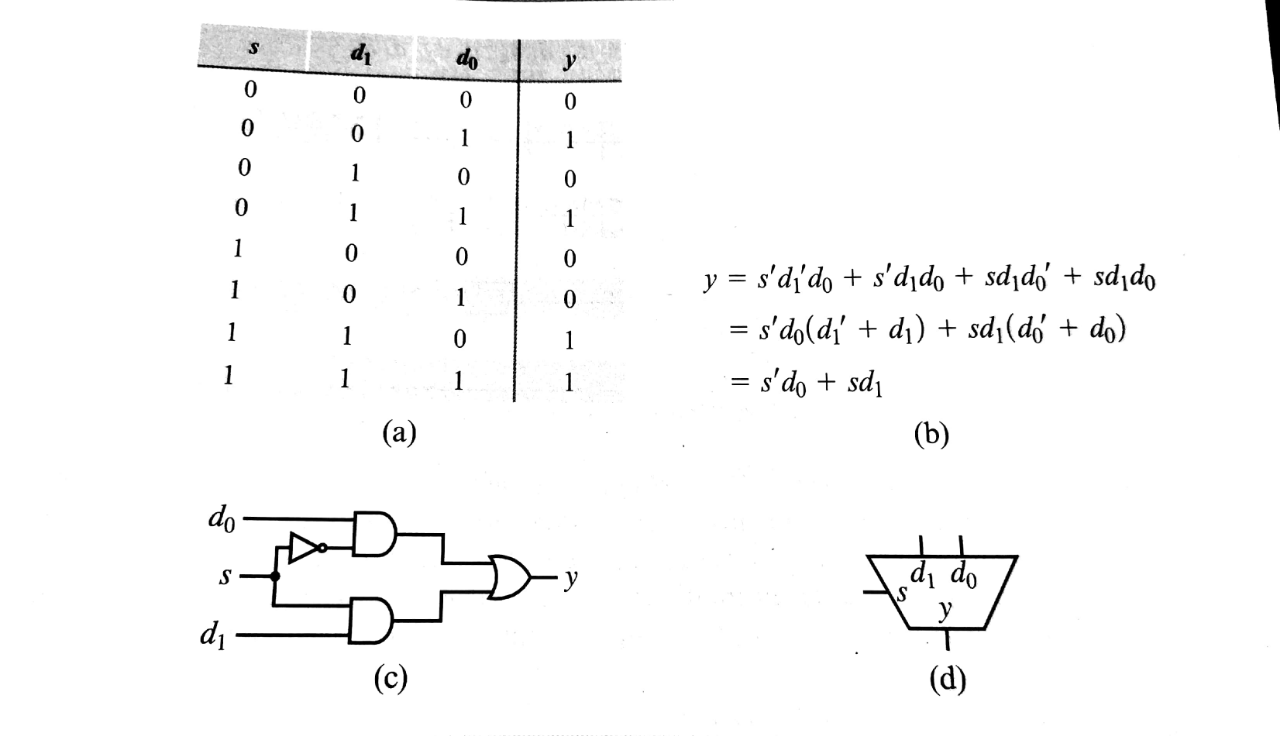

Mux根据选择位的值,从两位数据中选择一位输出。

下面基于Intellj IDEA创建Mux选择器,验证基本功能,并生成Verilog。

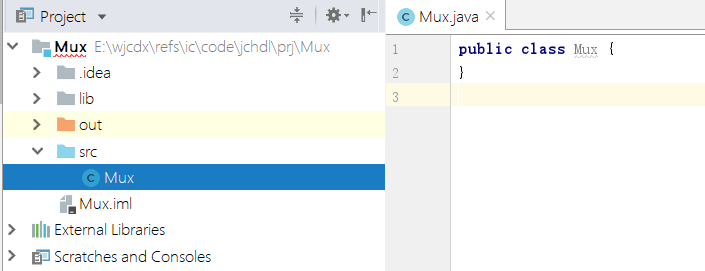

1. 创建Mux.java类。

? ?

?

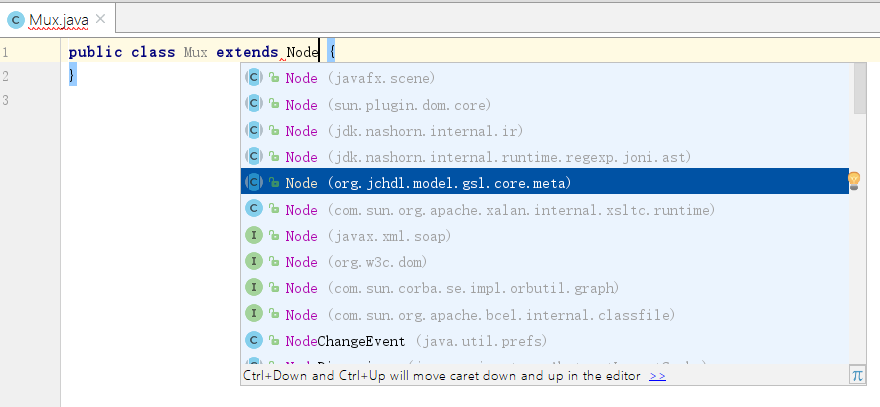

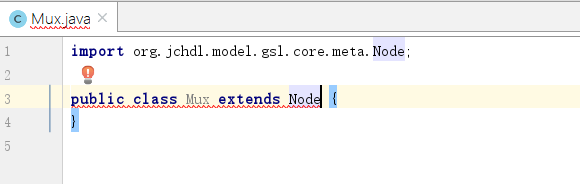

2. 添加代码使Mux继承Node类

? ?

?

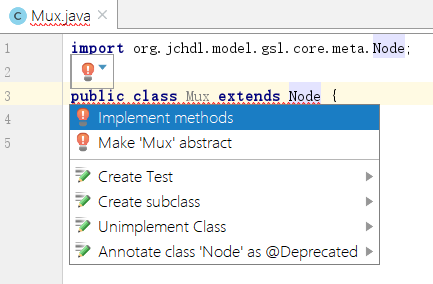

利用Intellj IDEA强大的提示功能,直接从选项中选择即可:

? ?

?

3. 生成logic()方法

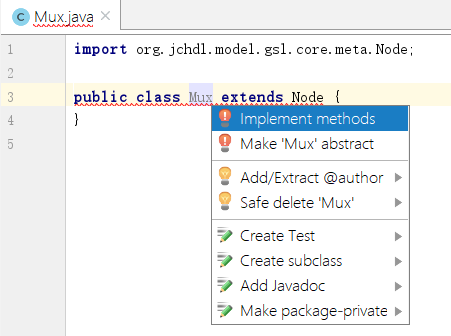

红色波浪线为出错的地方。可以点提示符号看提示:

? ?

?

也可以使用快捷键Alt+Enter:

? ?

?

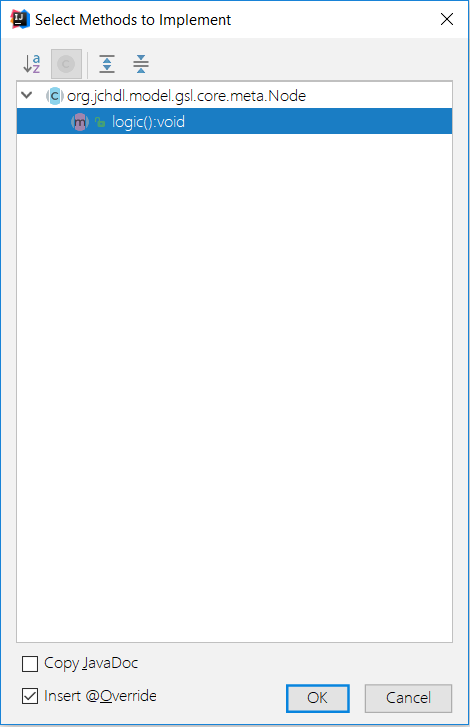

我们选择实现方法,会询问要实现的父类中的抽象方法:

? ?

?

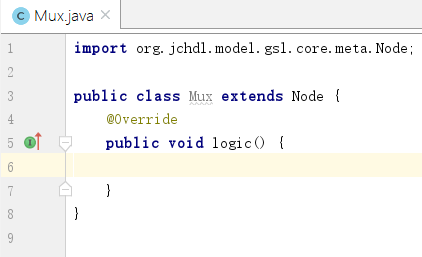

这里只有一个,直接点OK,可以看到生成了一个logic()方法:

? ?

?

4. 生成构造方法

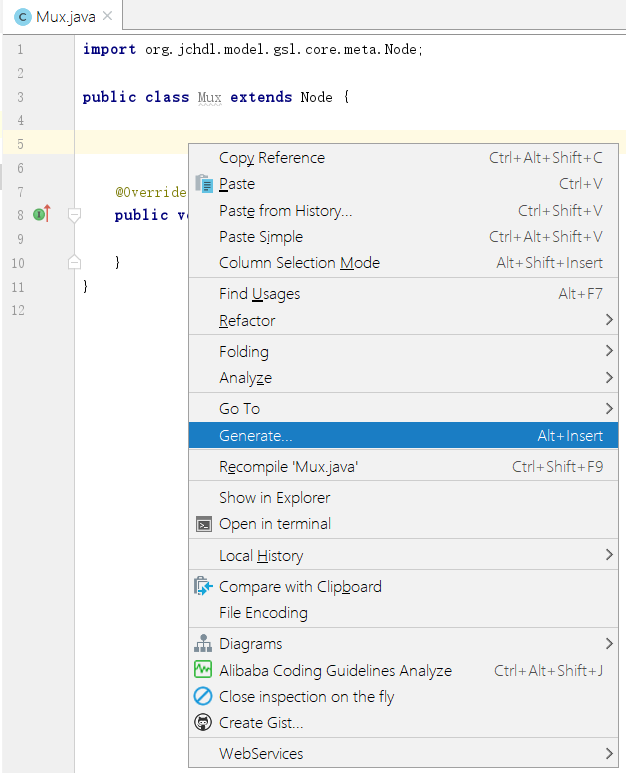

把构造方法放在logic()方法的上面,添加几个空行,右击选择Generate:

? ?

?

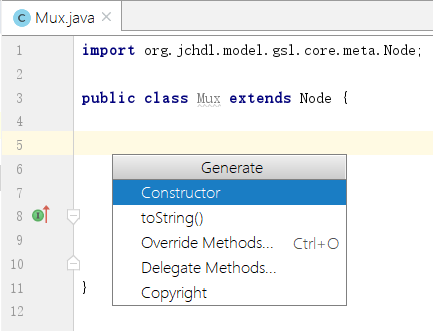

选择Constructor:

? ?

?

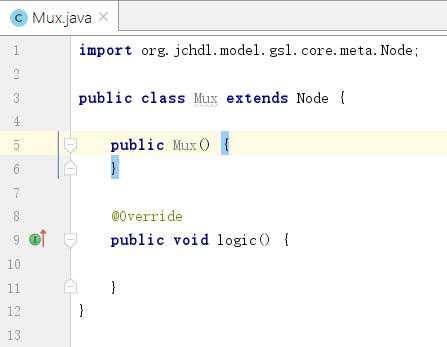

即生成构造方法:

? ?

?

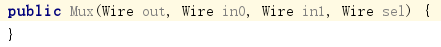

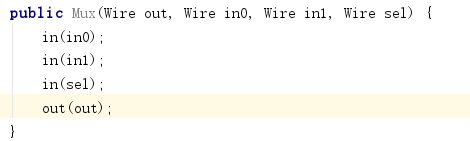

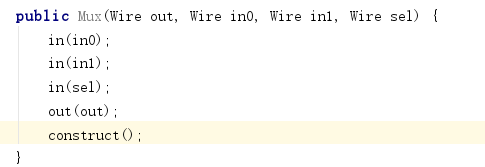

5. 为构造方法添加输入和输出

从原理图可以看出,Mux有两个数据输入和一个选择输入,一个输出。

? ?

?

搜集一下输入线和输出线:

? ?

?

调用construct()方法构建节点:

? ?

?

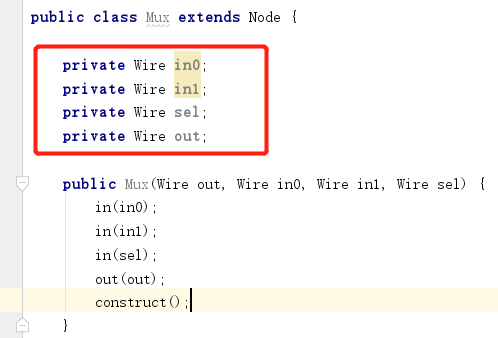

5. 声明节点内部的线

节点内部需要从input/output port引出线连接到内部的子节点上,可以作为Mux类的属性声明;

? ?

?

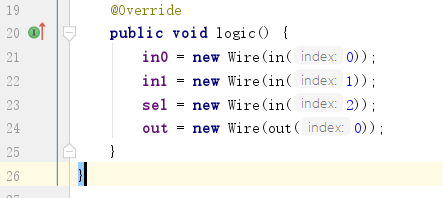

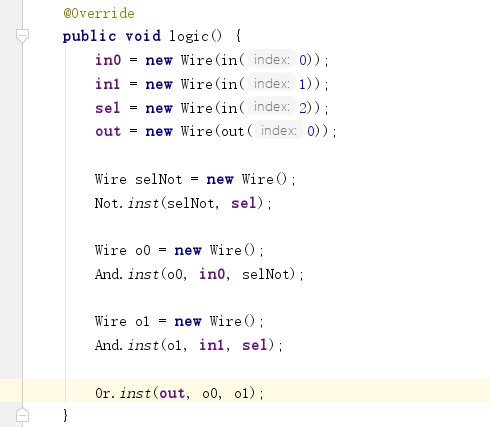

6. 实现logic()方法:

logic()方法需要从input port引出线连接到子节点,并把子节点的输出线连接到Mux节点的output port上。

从input port 0,1,2分别引出线in0,in1,sel, 创建线out连接到output port 0.

? ?

?

创建子节点并连接:

? ?

?

这样所有的线就连接完成了。

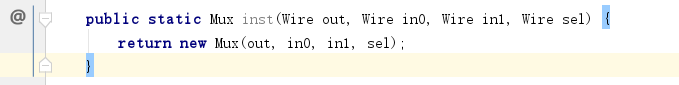

7. 创建inst静态方法返回Mux节点实例,方便使用:

? ?

?

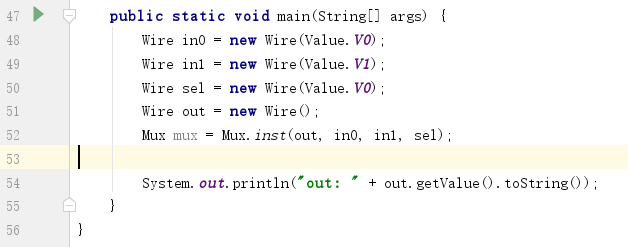

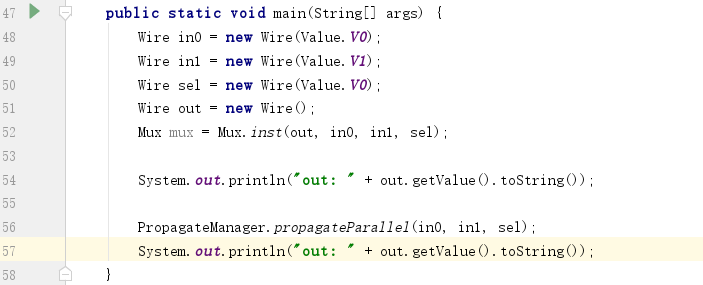

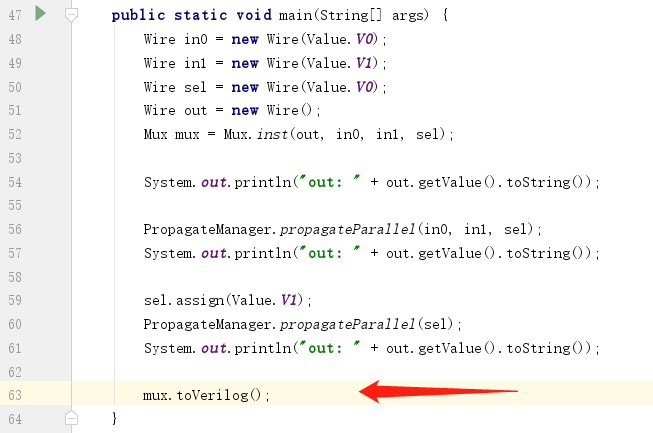

8. 创建main函数执行并验证结果。

? ?

?

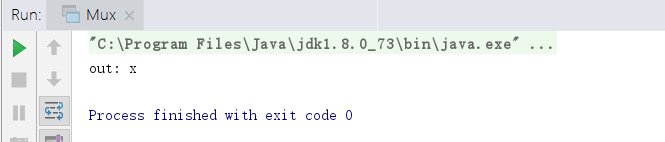

点击三角符号运行查看结果:

? ?

?

结果为x,这是因为in0, in1, sel的初值并没有向后传播,所以打印的为out的初值。

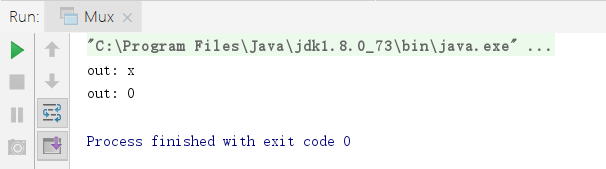

使用PropagateManager传播一下值,

? ?

?

运行结果为:

? ?

?

可以看到与真值表中的第3行相同,out的值为in0的值,即0.

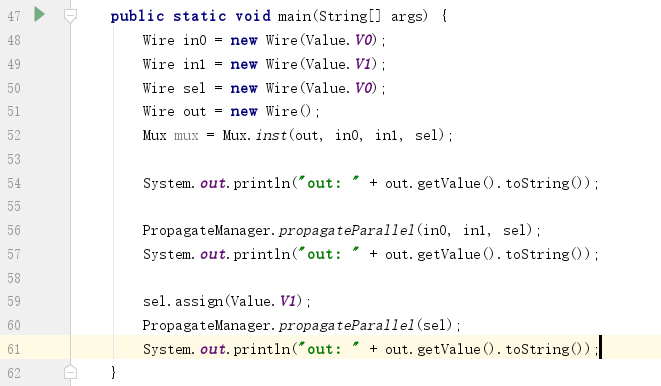

改变sel的值,选择输出in1,

? ?

?

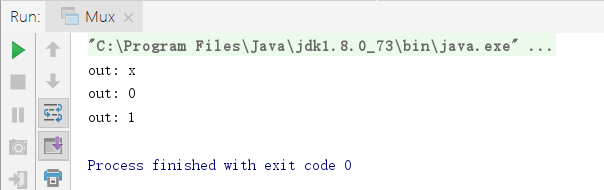

因为只有sel的值发生改变,所以只需要传播sel的值即可。运行结果如下:

? ?

?

可以看到与真值表倒数第2行一致,选择了in1的值,即1.

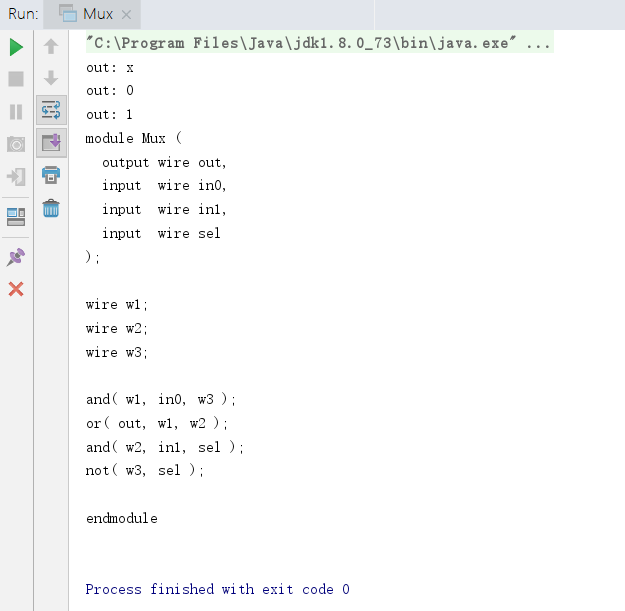

9. 生成Verilog

直接添加一行,调用mux.toVerilog()即可。

? ?

?

运行输出如下:

? ?

?

可以直接拷贝出来使用。

因为节点内部使用的线,没有声明为节点属性。并且暂时没有支持logic()内部局部变量解析,所以使用了普通的命名。

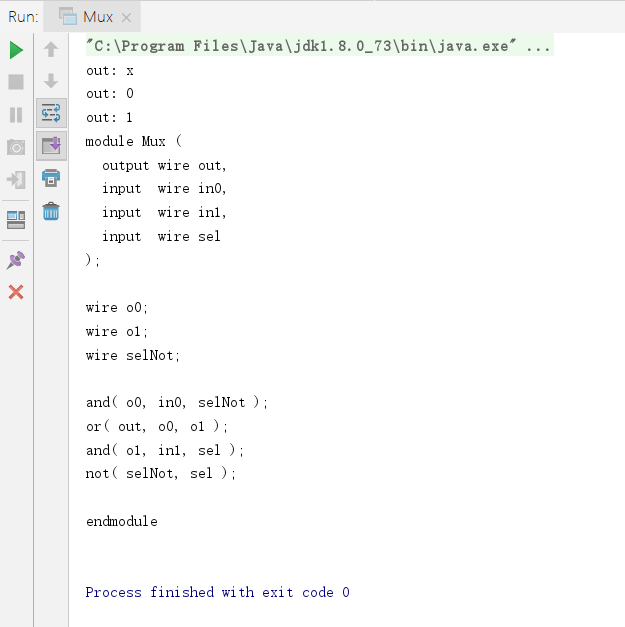

修改一下,作为节点类的属性声明:

? ?

?

运行生成的Verilog如下:

? ?

?

jchdl-GSL-实例 - 使用Intellij IDEA创建Mux

标签:b2c init 调用 enc 解析 java intel git ilo

原文地址:https://www.cnblogs.com/wjcdx/p/9656936.html