标签:检测 系统 mbr uri 3.3 占空比 alt 客户 反馈

节选自 http://www.dianyuan.com/bbs/987183.html 【草根大侠】贴 关于MOS管导通内阻和米勒电容(Qgd)差异对效率的影响

http://www.epc.com.cn/subject/200910/13172.html 理解功率MOSFET的开关损耗(图)

最近做了一款正激有源钳位电源,DC48输入,DC28V输出,功率200W,频率100K。下边分别说说MOS管的差异

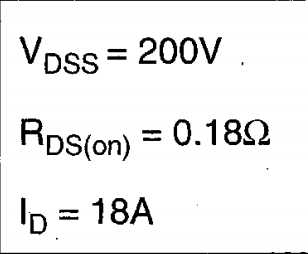

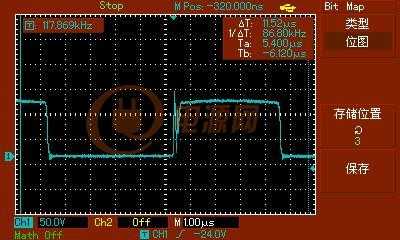

1.主MOS管用的IRF640,钳位管也用的IRF640 ,输出整流管用的MBR20200;实测效率满载87.5%。IRF640的主要参数

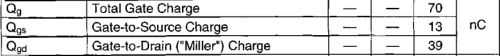

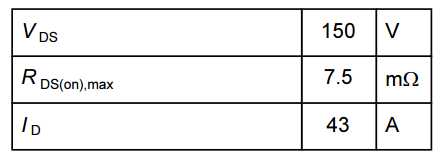

2.正好参加了元器件网的特约评论员活动,给了几片英飞凌的IPA075N15N3 G,在此先谢谢元器件网及源源。拿到手了就想换上去看看有啥区别,就把主MOS管换了个075N15,结果还真不一样,满载效率直接上升3个百分点,到了90.5%。再把IPA075N15N3 G的主要参数放上来

先从原理上分析下

1.第一种情况,IRF640的总输入功率Pin640=200/0.875=228.5W,输入电流Iin640=228.5/48=4.76A,导通损耗Pd640=4.764.760.18(IRF640的导通内阻)*ton

2.第二种情况,075N15的总输入功率PinN15=200/0.905=221W,输入电流IinN15=221/48=4.6A,导通损耗PdN15=4.64.60.0075*ton

3.两个导通损耗相差Pd=Pd640 -PdN15 两个的总功率相差P=228.5-221=7.5W

两个的开关损耗相差Pk=P-Pd

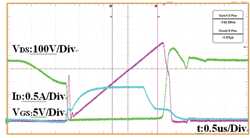

以上所算的都是大概值,因开关损耗的算法比较繁琐,这就不算了,好多电源资料上都有。米勒电容主要影响开关速度,他里边所存的电量会和变压器漏感,还有MOS的一些寄生参数,PCB的一些寄生参数等产生谐振,影响效率。所以应选择米勒电容比较小的MOS,从测试的波形可以形象的表达出来!

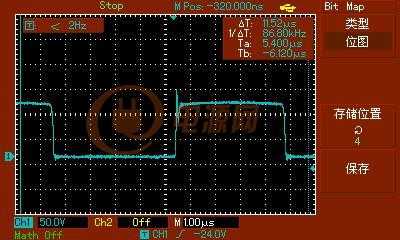

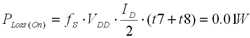

这个是640的

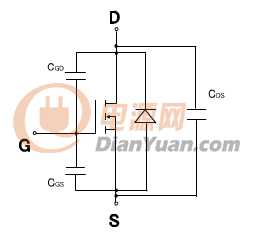

这个是IPA075N15N3 G的

实际用的时候,我用的是国产640,他的资料里边关于640的特性特别少,所以就用了IR的资料。变压器是我自己绕的,绕的不好,用的骨架太大,公司没小的了,骨架一半都没用完,所以漏感大了。

物有所长,必有所短。075N15效率高但价格很高,效率高,可靠性好,散热好做;而640的效率低点,但价格很低(尤其国产640更低)。在选取时大家可根据自己的情况选取,尽量的满足客户要求。

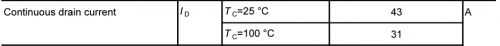

因MOS导通时是从输入电容充电,Ciss为Cgs与Cgd之和,Cgs与Cgd一样有米勒效应关系,所以就一并考虑.MOS完全导通时,Vgs必增加,Cgd也会增加,Ciss也会增加

今天先从导通内阻说起吧大家都知道,一般情况下电压越高,导通内阻越大。这个就和MOS的制作工艺有关系了,为了保证足够大的漏源击穿电压Vds,需要有高电阻率外延层,这会使MOS的导通电阻增大。

根据选择的拓扑选择合适的MOS管及吸收电路,再保证高端Vds不超的情况下,尽量选择耐压低的管子,耐压高的管子一般会很贵,品种单一没有耐压低的可选性多,而且效率不好提升。

耐压相同的管子一般情况下,导通内阻越小价格越高,根据自己的实际使用,在性价比中尽量折中。尽量把鱼和熊掌全得到!

栅源电压Vgs的选择对导通电阻也有影响,电压越高导通越好,导通程度越好,内阻越小,但随着栅源电压Vgs的升高,开关速度会降低,这个以后说;还有可能导致栅源电压Vgs击穿,器件失效。栅源电压越低,导通越差,内阻越大,效率越低。所以建议大家选取栅源电压Vgs为10V-18V之间。

做好散热,导通内阻随着温度的升高而增大,所以要把热设计搞好,温升尽量的低,效率尽量的高。

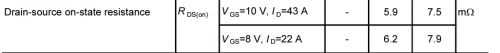

这个在管子的datasheet里边都有体现,下边咱看下075N15的

栅源电压不同,导通内阻也不一样。

这个虽然没有直接标出导通内阻,但从电流上可以体现出来,温度升高电流减小,输入电压不变说明内阻增大。

以上所说,希望对大家在以后选取MOS时有些帮助

再说下MOS管的寄生电容对效率的影响把,这个涉及的比较多了。咱一切从简单的说,以照顾新人为主,好多大侠比我还懂!

大家知道MOS的极间电容直接影响其开关特性,其等效电路如图

输入电容Ciss=Cgs+Cdg (D,S短接),输出电容Coss=Cds+Cgd(G,S短接)

反馈电容Crss=Cgd(也叫米勒电容)

以上是MOS管的电容特性,有定义Q=C*V可得,在电压一定时,电容量越小,Qg越小。

而Qg为栅极的总电荷量,Qgs为栅源极间的电荷量,Qgd为栅漏极间的电荷量。再根据公式t=Q/I得,当电流一定时,Q越小,时间越短,即开关速度越快,开关损耗越小。

所以再选取MOS时尽量选取Qg小的,以减小开关损耗。

而Qgs主要影响开启时间,Qgd主要影响关断时间。

1.在两个MOS管的耐压及电流一定时,选取Qg小的MOS;

2.如我上边的波形及两个资料来看,在Qg一样时要选取Qgd小的MOS。

3.根据自己的实际功率选择合适的MOS,一般情况下内阻越小,Qg越大;Vds越小,Qg越 大。

4.根据实际频率选择合适MOS,频率越高开关损耗越大,这个时候可能你的开关损耗远大 于你的导通损耗,这时要适当的选择内阻大点的MOS,以提升开关损耗;

5.尽量选择贴片的MOS,这样MOS的引脚短,引脚上的寄生电感等参数会小的多,减小损耗!

同频率下开关速度越快,开关损耗越小。而你同频率的开关速度取决于哪,你的寄生电容的冲放电速度。那个公式是对的,是频率越高开关损耗越大。但你的频率高了,更应该选寄生电容小的MOS,这样才能有效减小开关损耗,提升效率!

个人觉得,MOS管的寄生电容小,EMI也会减小。你的寄生电容小,开关速度快,MOS管的反峰小,就拿我上边两个波形图可以体现出来,明显640的EMI要大!

你要这样想呢,你开的快,你关的也快呢;或者你开的慢,关的快呢。开启速度可以在你的PWM到你的栅极加个电阻限制下电流,但关断速度就全靠你管子的寄生电容参数了。这个一般我会看Qgd,就像我上边波形显示的一样,那个Qgd大的640关断波形和速度就是没075N15的快,所以这就和你选择管子有关系了。你说的“我觉得还是应该看你的开关管漏端电压的下降/上升和开关管电流的上升/下降时间的交叠时间吧,你开得快,交叠时间多;和你开得慢,交叠时间少”是对的,但你可以通过选择MOS管的寄生电容尽量的去减小你的交叠时间,去提高效率。软开关不也是刻意去改变管子的导通关断,去实现零电压或零电流,这也是软开关技术效率高的原因之一吧!

本文详细分析计算开关损耗,并论述实际状态下功率MOSFET的开通过程和自然零电压关断的过程,从而使电子工程师知道哪个参数起主导作用并更加深入理解MOSFET。

MOSFET开关损耗

1 开通过程中MOSFET开关损耗

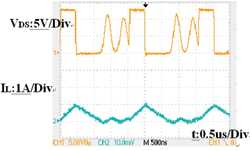

功率MOSFET的栅极电荷特性如图1所示。值得注意的是:下面的开通过程对应着BUCK变换器上管的开通状态,对于下管是0电压开通,因此开关损耗很小,可以忽略不计。

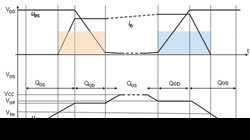

图1 MOSFET开关过程中栅极电荷特性

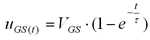

开通过程中,从t0时刻起,栅源极间电容开始充电,栅电压开始上升,栅极电压为

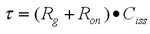

其中:

,VGS为PWM栅极驱动器的输出电压,Ron为PWM栅极驱动器内部串联导通电阻,Ciss为MOSFET输入电容,Rg为MOSFET的栅极电阻。

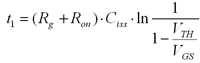

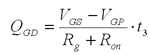

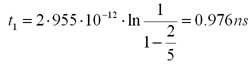

VGS电压从0增加到开启阈值电压VTH前,漏极没有电流流过,时间t1为

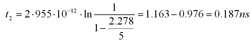

VGS电压从VTH增加到米勒平台电压VGP的时间t2为

VGS处于米勒平台的时间t3为

t3也可以用下面公式计算:

注意到了米勒平台后,漏极电流达到系统最大电流ID,就保持在电路决定的恒定最大值ID,漏极电压开始下降,MOSFET固有的转移特性使栅极电压和漏极电流保持比例的关系,漏极电流恒定,因此栅极电压也保持恒定,这样栅极电压不变,栅源极间的电容不再流过电流,驱动的电流全部流过米勒电容。过了米勒平台后,MOSFET完全导通,栅极电压和漏极电流不再受转移特性的约束,就继续地增大,直到等于驱动电路的电源的电压。

MOSFET开通损耗主要发生在t2和t3时间段。下面以一个具体的实例计算。输入电压12V,输出电压3.3V/6A,开关频率350kHz,PWM栅极驱动器电压为5V,导通电阻1.5Ω,关断的下拉电阻为0.5Ω,所用的MOSFET为AO4468,具体参数为Ciss=955pF,Coss=145pF,Crss=112pF,Rg=0.5Ω;当VGS=4.5V,Qg=9nC;当VGS=10V,Qg=17nC,Qgd=4.7nC,Qgs=3.4nC;当VGS=5V且ID=11.6A,跨导gFS=19S;当VDS=VGS且ID=250μA,VTH=2V;当VGS=4.5V且ID=10A,RDS(ON)=17.4mΩ。

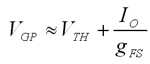

开通时米勒平台电压VGP:

计算可以得到电感L=4.7μH.,满载时电感的峰峰电流为1.454A,电感的谷点电流为5.273A,峰值电流为6.727A,所以,开通时米勒平台电压VGP=2+5.273/19=2.278V,可以计算得到:

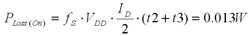

开通过程中产生开关损耗为

开通过程中,Crss和米勒平台时间t3成正比,计算可以得出米勒平台所占开通损耗比例为84%,因此米勒电容Crss及所对应的Qgd在MOSFET的开关损耗中起主导作用。Ciss=Crss+Cgs,Ciss所对应电荷为Qg。对于两个不同的MOSFET,两个不同的开关管,即使A管的Qg和Ciss小于B管的,但如果A管的Crss比B管的大得多时,A管的开关损耗就有可能大于B管。因此在实际选取MOSFET时,需要优先考虑米勒电容Crss的值。

减小驱动电阻可以同时降低t3和t2,从而降低开关损耗,但是过高的开关速度会引起EMI的问题。提高栅驱动电压也可以降低t3时间。降低米勒电压,也就是降低阈值开启电压,提高跨导,也可以降低t3时间从而降低开关损耗。但过低的阈值开启会使MOSFET容易受到干扰误导通,增大跨导将增加工艺复杂程度和成本。

2 关断过程中MOSFET开关损耗

关断的过程如图1所示,分析和上面的过程相同,需注意的就是此时要用PWM驱动器内部的下拉电阻0.5Ω和Rg串联计算,同时电流要用最大电流即峰值电流6.727A来计算关断的米勒平台电压及相关的时间值:VGP=2+6.727/19=2.354V。

关断过程中产生开关损耗为:

Crss一定时,Ciss越大,除了对开关损耗有一定的影响,还会影响开通和关断的延时时间,开通延时为图1中的t1和t2,图2中的t8和t9。

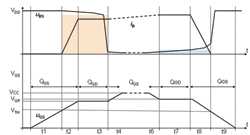

图2 断续模式工作波形

Coss产生开关损耗与对开关过程的影响

1 Coss产生的开关损耗

通常,在MOSFET关断的过程中,Coss充电,能量将储存在其中。Coss同时也影响MOSFET关断过程中的电压的上升率dVDS/dt,Coss越大,dVDS/dt就越小,这样引起的EMI就越小。反之,Coss越小,dVDS/dt就越大,就越容易产生EMI的问题。

但是,在硬开关的过程中,Coss又不能太大,因为Coss储存的能量将在MOSFET开通的过程中,放电释放能量,将产生更多的功耗降低系统的整体效率,同时在开通过程中,产生大的电流尖峰。

开通过程中大的电流尖峰产生大的电流应力,瞬态过程中有可能损坏MOSFET,同时还会产生电流干扰,带来EMI的问题;另外,大的开通电流尖峰也会给峰值电流模式的PWM控制器带来电流检测的问题,需要更大的前沿消隐时间,防止电流误检测,从而降低了系统能够工作的最小占空比值。

Coss产生的损耗为:

对于BUCK变换器,工作在连续模式时,开通时MOSFET的电压为输入电源电压。当工作在断续模式时,由于输出电感以输出电压为中心振荡,Coss电压值为开通瞬态时MOSFET的两端电压值,如图2所示。

2 Coss对开关过程的影响

图1中VDS的电压波形是基于理想状态下,用工程简化方式来分析的。由于Coss存在,实际的开关过程中的电压和电流波形与图1波形会有一些差异,如图3所示。下面以关断过程为例说明。基于理想状态下,以工程简化方式,认为VDS在t7时间段内线性地从最小值上升到输入电压,电流在t8时间段内线性地从最大值下降到0。

图3 MOSFET开关过程中实际波形

实际过程中,由于Coss影响,大部分电流从MOSFET中流过,流过Coss的非常小,甚至可以忽略不计,因此Coss的充电速度非常慢,电流VDS上升的速率也非常慢。也可以这样理解:正是因为Coss的存在,在关断的过程中,由于电容电压不能突变,因此VDS的电压一直维持在较低的电压,可以认为是ZVS,即0电压关断,功率损耗很小。

同样的,在开通的过程中,由于Coss的存在,电容电压不能突变,因此VDS的电压一直维持在较高的电压,实际的功率损耗很大。

在理想状态的工程简化方式下,开通损耗和关断损耗基本相同,见图1中的阴影部分。而实际的状态下,关断损耗很小而开通损耗很大,见图3中的阴影部分。

从上面的分析可以看出:在实际的状态下,Coss将绝大部分的关断损耗转移到开通损耗中,但是总的开关功率损耗基本相同。图4波形可以看到,关断时,VDS的电压在米勒平台起始时,电压上升速度非常慢,在米勒平台快结束时开始快速上升。

图4 非连续模式开关过程中波形

Coss越大或在DS极额外的并联更大的电容,关断时MOSFET越接近理想的ZVS,关断功率损耗越小,那么更多能量通过Coss转移到开通损耗中。为了使MOSFET整个开关周期都工作于ZVS,必须利用外部的条件和电路特性,实现其在开通过程的ZVS。如同步BUCK电路下侧续流管,由于其寄生的二极管或并联的肖特基二极管先导通,然后续流的同步MOSFET才导通,因此同步MOSFET是0电压导通ZVS,而其关断是自然的0电压关断ZVS,因此同步MOSFET在整个开关周期是0电压的开关ZVS,开关损耗非常小,几乎可以忽略不计,所以同步MOSFET只有RDS(ON)所产生的导通损耗,选取时只需要考虑RDS(ON)而不需要考虑Crss的值。

注意到图1是基于连续电流模式下所得到的波形,对于非连续模式,由于开通前的电流为0,所以,除了Coss放电产生的功耗外,没有开关的损耗,即非连续模式下开通损耗为0。但在实际的检测中,非连续模式下仍然可以看到VGS有米勒平台,这主要是由于Coss的放电电流产生的。Coss放电快,持续的时间短,这样电流迅速降低,由于VGS和ID的受转移特性的约束,所以当电流突然降低时,VGS也会降低,VGS波形前沿的米勒平台处产生一个下降的凹坑,并伴随着振荡。

标签:检测 系统 mbr uri 3.3 占空比 alt 客户 反馈

原文地址:https://www.cnblogs.com/ramlife/p/9673794.html