标签:sys stat tac tput lock 四种 统一 aci display

https://mp.weixin.qq.com/s/yJx_dV6ScUStJtPWVuD38w

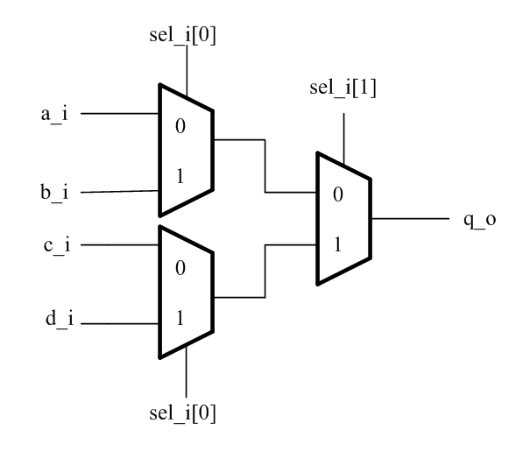

原理图

? ?

?

参考链接

https://github.com/wjcdx/jchdl/blob/master/src/org/jchdl/model/gsl/example/Mux4.java

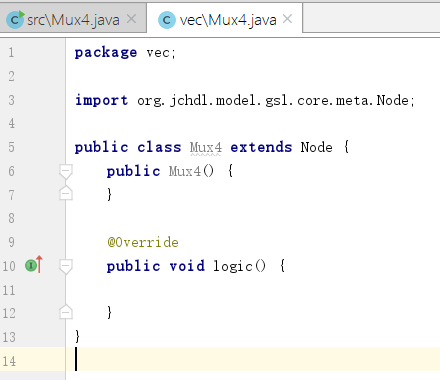

1.创建Mux4.java, 并生成构造方法和logic()方法

? ?

?

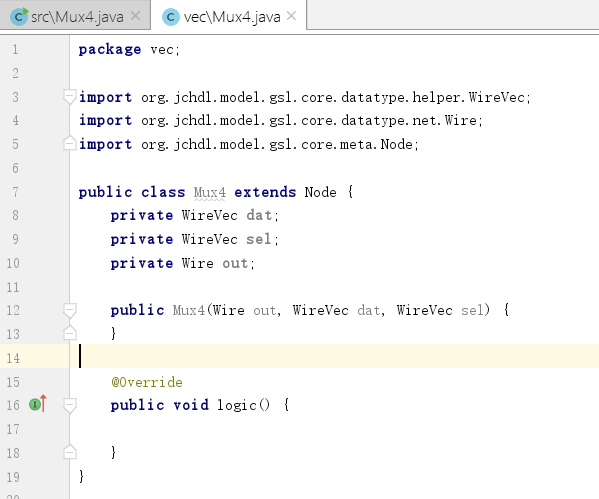

2. 根据逻辑原理图,添加输入输出线

? ?

?

需要注意的是,这里使用了WireVec,而不是Wire来声明输入线,以便统一处理一排线。

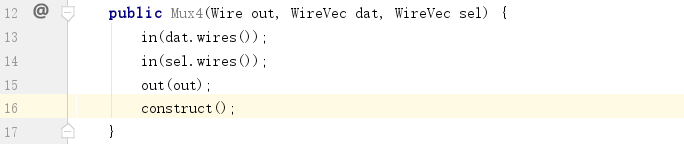

3. 在构造方法中搜集输入输出线并调用construct()方法

? ?

?

这里一次性的把dat, sel中的所有线都加到输入线中。

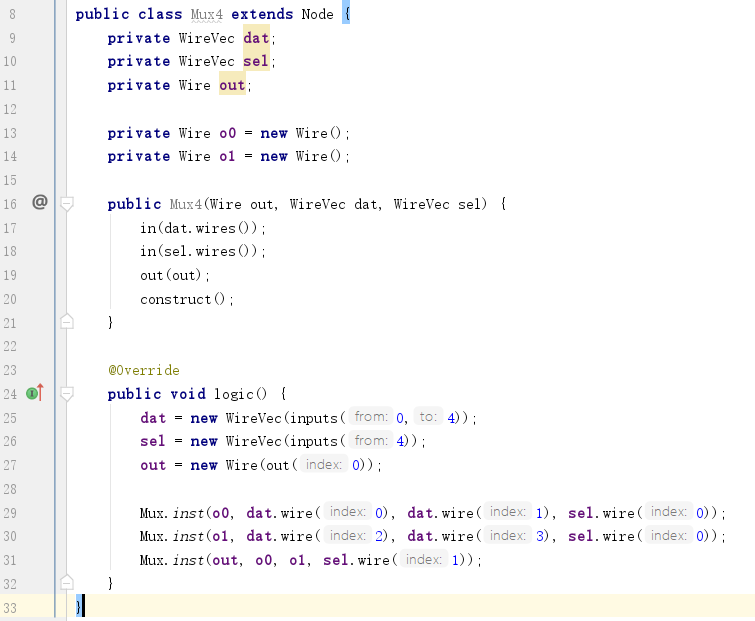

4. 在logic()方法中创建子节点并连线

? ?

?

创建WireVec时可以直接与input/output相连;使用时从WireVec中取出某一条线使用即可。

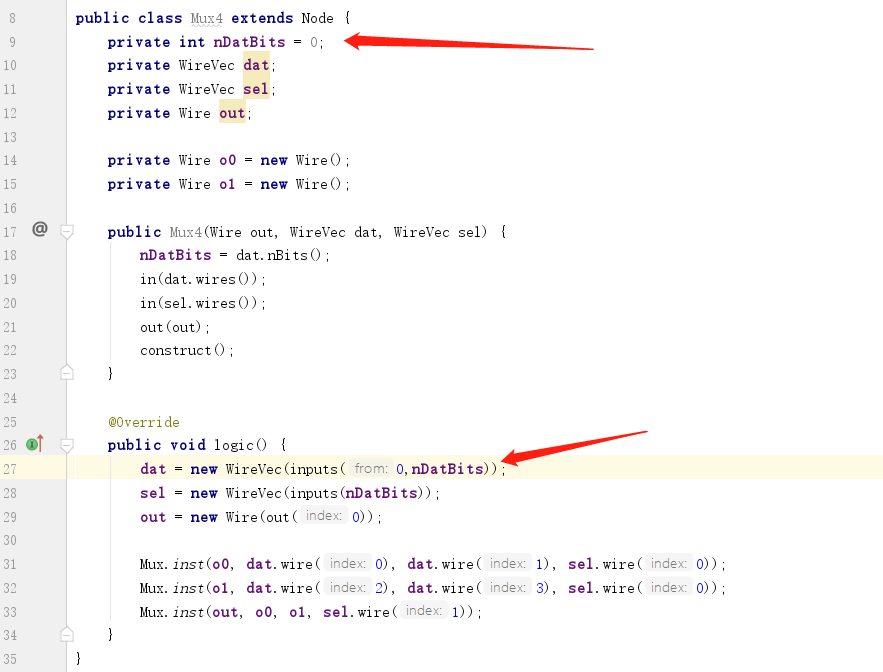

这里更通用的做法,是记录输入WireVec dat的位数,这样在logic()取的时候,就不需要把数字写死了:

? ?

?

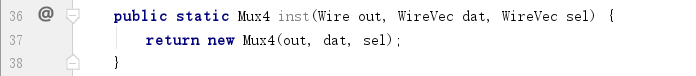

5. 创建inst静态方法方便后续使用

? ?

?

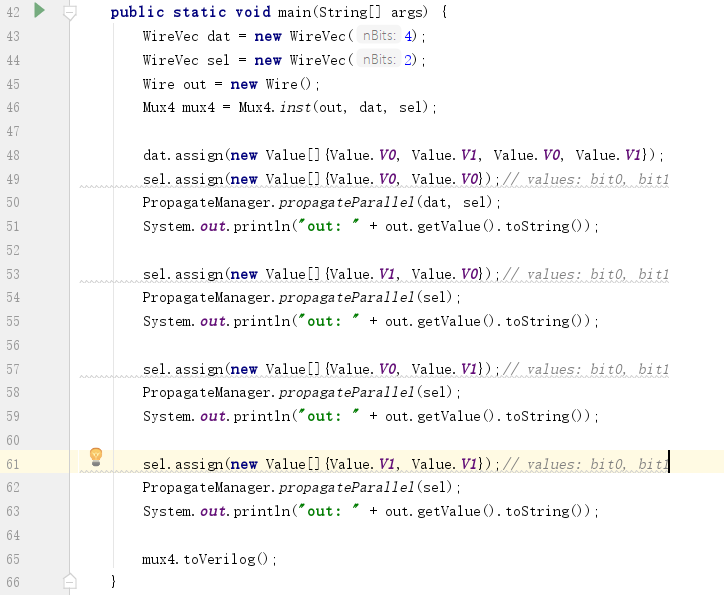

6. 创建main方法执行验证

? ?

?

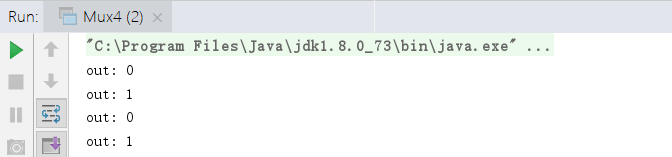

运行结果为:

? ?

?

四种组合逐个选择i0~i3中的值。

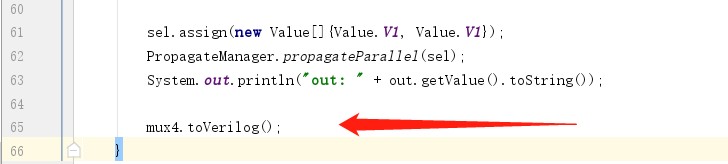

7. 生成Verilog

? ?

?

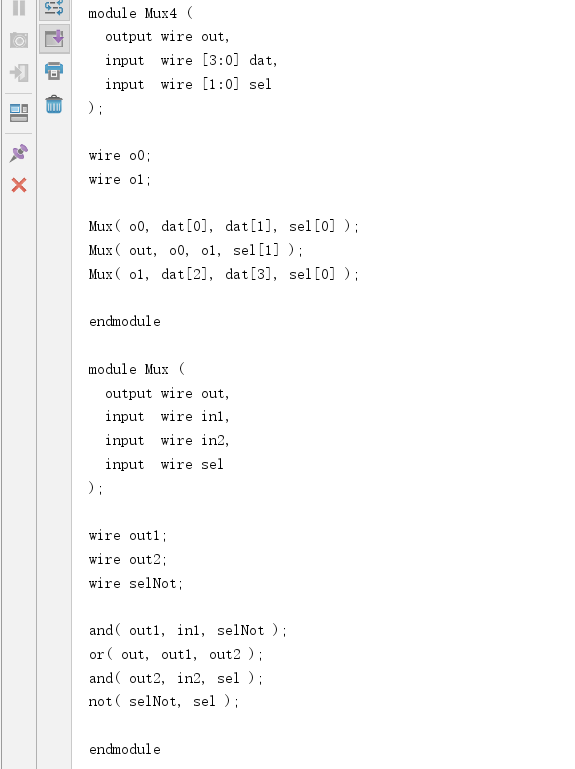

执行结果如下:

? ?

?

package vec;

import org.jchdl.model.gsl.core.datatype.helper.WireVec;

import org.jchdl.model.gsl.core.datatype.net.Wire;

import org.jchdl.model.gsl.core.meta.Node;

import org.jchdl.model.gsl.core.meta.PropagateManager;

import org.jchdl.model.gsl.core.value.Value;

import org.jchdl.model.gsl.operator.conditional.Mux;

public class Mux4 extends Node {

private int nDatBits = 0;

private WireVec dat;

private WireVec sel;

private Wire out;

private Wire o0 = new Wire();

private Wire o1 = new Wire();

public Mux4(Wire out, WireVec dat, WireVec sel) {

nDatBits = dat.nBits();

in(dat.wires());

in(sel.wires());

out(out);

construct();

}

@Override

public void logic() {

dat = new WireVec(inputs(0, nDatBits));

sel = new WireVec(inputs(nDatBits));

out = new Wire(out(0));

Mux.inst(o0, dat.wire(0), dat.wire(1), sel.wire(0));

Mux.inst(o1, dat.wire(2), dat.wire(3), sel.wire(0));

Mux.inst(out, o0, o1, sel.wire(1));

}

public static Mux4 inst(Wire out, WireVec dat, WireVec sel) {

return new Mux4(out, dat, sel);

}

public static void main(String[] args) {

WireVec dat = new WireVec(4);

WireVec sel = new WireVec(2);

Wire out = new Wire();

Mux4 mux4 = Mux4.inst(out, dat, sel);

dat.assign(new Value[]{Value.V0, Value.V1, Value.V0, Value.V1});

sel.assign(new Value[]{Value.V0, Value.V0});

PropagateManager.propagateParallel(dat, sel);

System.out.println("out: " + out.getValue().toString());

sel.assign(new Value[]{Value.V1, Value.V0});

PropagateManager.propagateParallel(sel);

System.out.println("out: " + out.getValue().toString());

sel.assign(new Value[]{Value.V0, Value.V1});

PropagateManager.propagateParallel(sel);

System.out.println("out: " + out.getValue().toString());

sel.assign(new Value[]{Value.V1, Value.V1});

PropagateManager.propagateParallel(sel);

System.out.println("out: " + out.getValue().toString());

mux4.toVerilog();

}

}

jchdl - GSL实例 - Mux4(使用WireVec简化输入线声明)

标签:sys stat tac tput lock 四种 统一 aci display

原文地址:https://www.cnblogs.com/wjcdx/p/9678762.html