标签:cache 有一个 标识 page inf 适用于 多路径 col 关联

刚开始接触NVMe,对此理解不深,如有错误敬请指出

NVM ExpressTM(NVMeTM)接口允许主机软件与非易失性存储器子系统通信。 此接口针对企业和客户端固态驱动器进行了优化,通常作为寄存器级接口连接到PCI Express接口。

注意:在开发期间,此规范称为Enterprise NVMHCI。 但是,在完成之前,该名称已修改为NVM Express基本规范。 此接口适用于客户端和企业系统。

有关从修订版1.2.1到修订版1.3的更改的概述,请参阅http://nvmexpress.org/changes以获取描述新功能的文档,包括控制器遵守修订版1.3的强制性要求。

该规范定义了用于与非易失性存储器子系统通信的寄存器接口。 它还定义了一个与NVM子系统一起使用的标准命令集。

寄存器接口和命令集是与任何使用NVM的模型分开指定的,这里仅指定与NVM子系统的通信接口。 因此,该规范没有规定非易失性存储器系统是用作固态驱动器,主存储器,高速缓冲存储器,备份存储器,冗余存储器等。具体的使用模型在范围之外,是可选的, 并且没有许可。

此接口在任何非易失性存储器管理之上指定,如损耗均衡。 擦除和其他针对NVM技术的操作进行了抽象。

此规范不包含有关缓存算法或技术的任何信息。

即使符合规范要求,本说明书中提及的其他已发布规范的实现或使用也不在本规范的范围内(例如,PCI,PCI Express和PCI-X)。

NVM Express可扩展主机控制器接口旨在满足使用基于PCI Express的固态驱动器的企业和客户端系统的需求。 该接口提供优化的命令提交和完成路径。 它支持并行操作,支持多达65,535个IO队列,每个IO队列具有高达64K的未完成命令。 此外,还增加了对端到端数据保护(兼容SCSI保护信息,通常称为T10 DIF和SNIA DIX标准),增强的错误报告和虚拟化等许多企业功能的支持。 该接口具有以下关键属性:

该规范定义了一组简化的寄存器,其功能包括:

•指示控制器功能;

•控制器故障状态(命令状态通过CQ直接处理);

•管理队列配置(通过Admin命令处理I / O队列配置);

• Doorbell registers可扩展数量的提交和完成队列。

NVM Express控制器与单个PCI功能相关联。适用于整个控制器的功能和设置在控制器Capabilities (CAP)寄存器和识别控制器数据结构中指示。

命名空间是一系列的非易失性存储器,可以格式化为逻辑块。 NVM Express控制器可以支持使用相同的命名空间ID引用的多个命名空间。可以使用命名空间管理和命名空间附加命令创建和删除命名空间。 Identify Namespace数据结构指示具体的命名空间的功能和设置。功能和设置对所有名称空间通用,由名称空间ID为FFFFFFFFh的Identify Namespace数据结构报告。

NVM Express基于配对的提交和完成队列机制。命令由主机软件放入提交队列。完成由控制器放入相关的完成队列中。多个提交队列可以使用相同的完成队列。提交和完成队列在内存中分配。

一个管理员提交关联一个已存在的完成队列以用于控制器管理和控制(例如,IO提交和完成队列的创建和删除,中止命令等)。 只有属于Admin命令集的命令才可以提交给Admin Submission Queue。

IO命令集与IO队列对一起使用。 该规范定义了一个名为NVM命令集的IO命令集。 主机选择一个用于所有IO队列对的IO命令集。

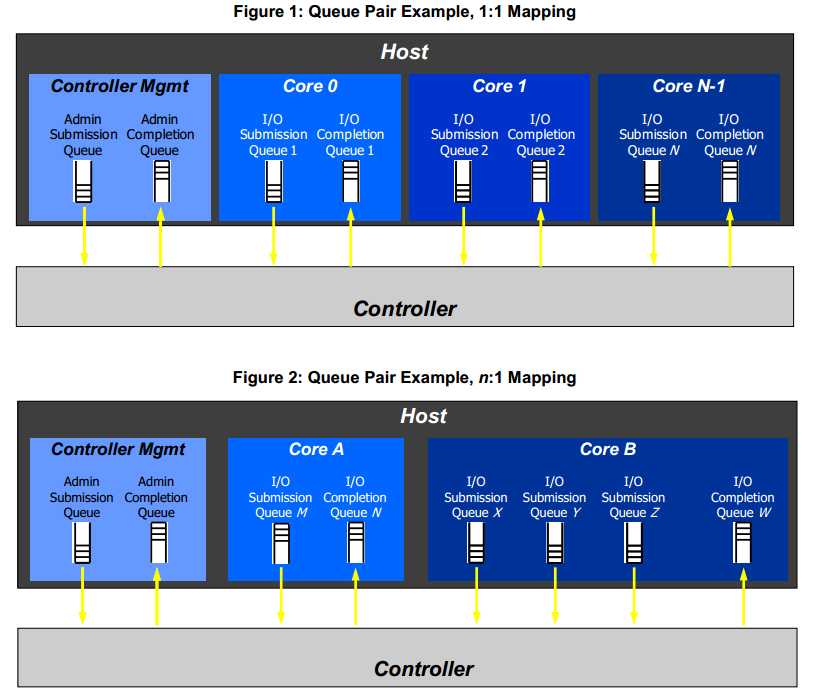

主机软件创建队列,最高可达控制器支持的最大值。 通常,创建的命令队列数基于系统配置和预期工作负载。 例如,在基于四核处理器的系统上,每个核心可能有一个队列对以避免锁定并确保在适当的处理器核心缓存中创建数据结构。 图1提供了队列对机制的图形表示,显示了提交队列和完成队列之间的1:1映射。 图2显示了一个示例,其中多个IO提交队列在Core B上使用相同的IO完成队列。图1和图2显示Admin Adminmission Queue和Admin Completion Queue之间始终存在1:1映射。

提交队列(SQ)是具有固定大小的循环缓冲区,主机软件使用该缓冲区提交命令以供控制器执行。当有一到n个新命令要执行时,主机软件会更新相应的SQ Tail doorbell寄存器。当有新的doorbell寄存器值写入时,控制器中会覆盖先前的SQ Tail值。控制器按顺序从提交队列中提取SQ条目,然后,它可以按任何顺序执行这些命令。

每个Submission Queue条目都是一个命令。命令大小为64字节。用于数据传输的内存中的物理内存位置使用Physical Region Page (PRP)条目或Scatter Gather Lists 指定。每个命令可以包括两个PRP条目或一个Scatter Gather List(SGL)段。如果需要两个以上的PRP条目来描述数据缓冲区,则提供指向描述PRP条目列表的PRP列表的指针。如果需要多个SGL段来描述数据缓冲区,则SGL段提供指向下一个SGL段的指针。

完成队列(CQ)是一个循环缓冲区,具有固定大小,用于发布已完成命令的状态。完成的命令由关联的SQ标识符和由主机软件分配的命令标识符的组合唯一地标识。多个提交队列可以与单个完成队列相关联。这表示即使这些命令源自多个提交队列也可以使用此功能通过一个完成队列处理所有完成的命令。 CQ头指针在处理完成指示最后一个完成队列条目之后由主机软件更新。完成队列条目中定义了相位标记(P)位,以表示在未咨询寄存器的情况下加入了新条目。这使主机软件能够确定新条目是否作为上一轮或当前完成通知的一部分发布。控制器完成命令后反转相位标记位。

标签:cache 有一个 标识 page inf 适用于 多路径 col 关联

原文地址:https://www.cnblogs.com/luxiaodai/p/9714256.html