标签:bsp 技术分享 amp inf 并行执行 ima ilog alt NPU

1.线与、线或功能

wor

1 module WO(A, B, C, D, WireOR) 2 input A,B,C,D; 3 output WireOr; 4 wor WireOr; 5 assign WireOr = A^B; 6 assign WireOr = C&D; 7 endmodule

2.三态门

assign WireTri = (En) ? 1‘bZ : (A^V)

3.assign 和 deassign : 在过程语块中对寄存器变量强制赋值和放开;

force 和 release : 在过程语块中对寄存器和线网强制赋值和放开;

module DEF(D, Clr, Clk, Q) input D, Clr, Clk; output Q; reg Q; always @ (Clr) begin if (!Clr) assign Q = 0; else deassign Q; end always @ (negedge Clk) Q <= D; endmodule

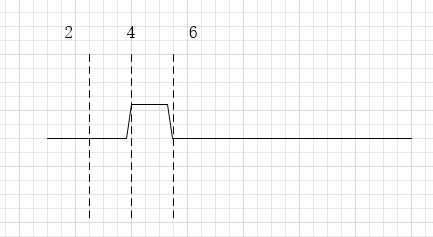

4.fork..join...

并行语句,内部并行执行

initial fork DataBin = 0; # 6 DataBin = 0; # 4 DataBin = 1; # 2 DataBin = 0; join

标签:bsp 技术分享 amp inf 并行执行 ima ilog alt NPU

原文地址:https://www.cnblogs.com/GenXGSS/p/9719603.html