标签:转换 启动 ble 线性 概述 cto hang tables 状态

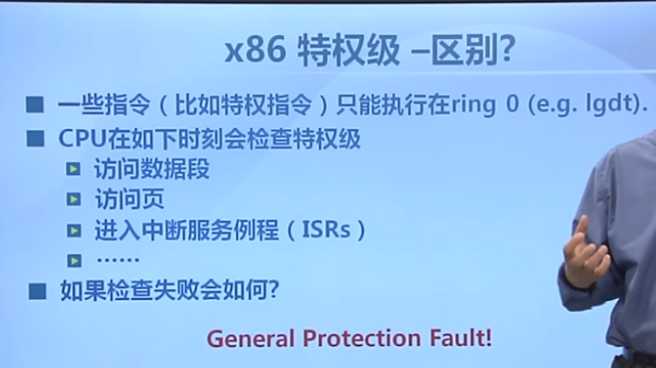

常见的操作系统 只使用了 0 和3

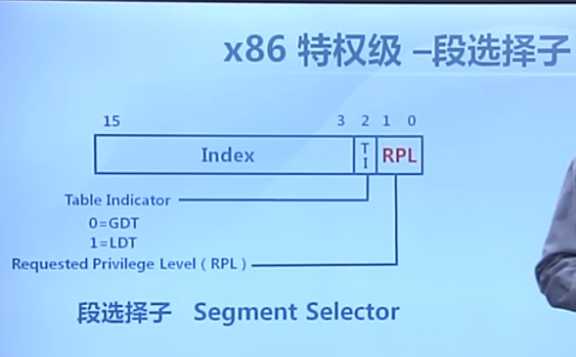

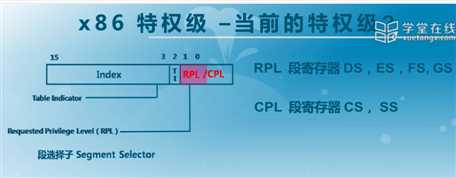

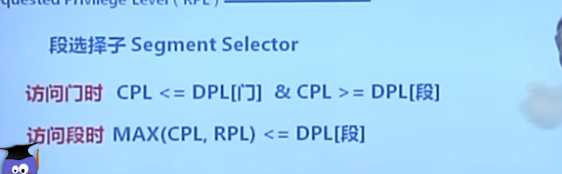

段选择子

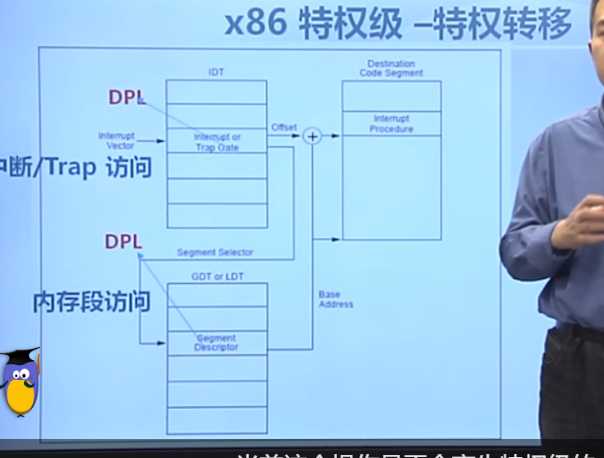

DPL 是段描述符的内容 段的信息

中断和陷入的 大致特权级的展现

RPL 当前要访问数据段对饮给的特权级

CPL 当前代码段的特权级

DPL 全局的

通过门区访问特权级更高的段

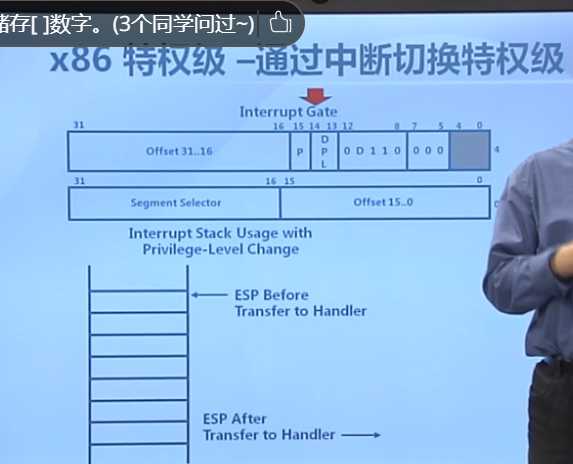

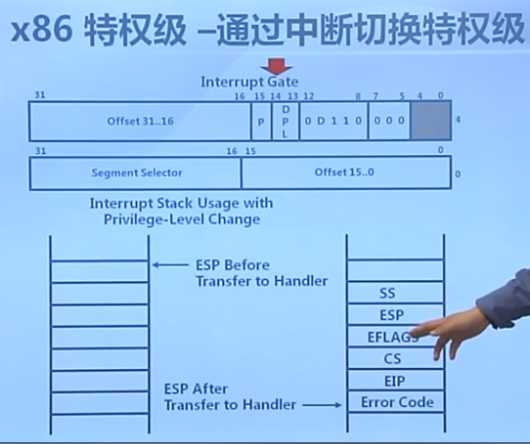

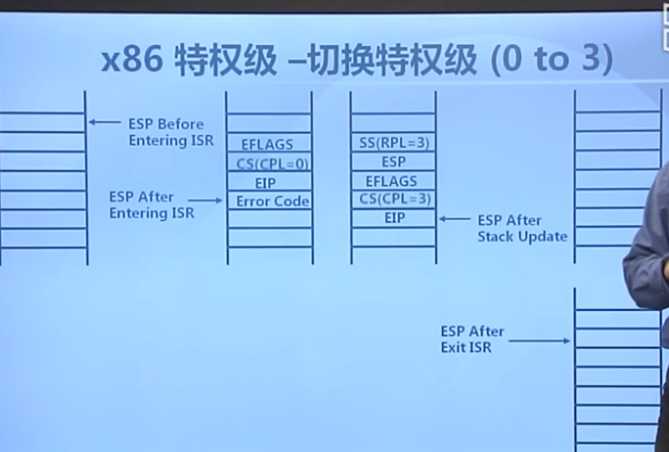

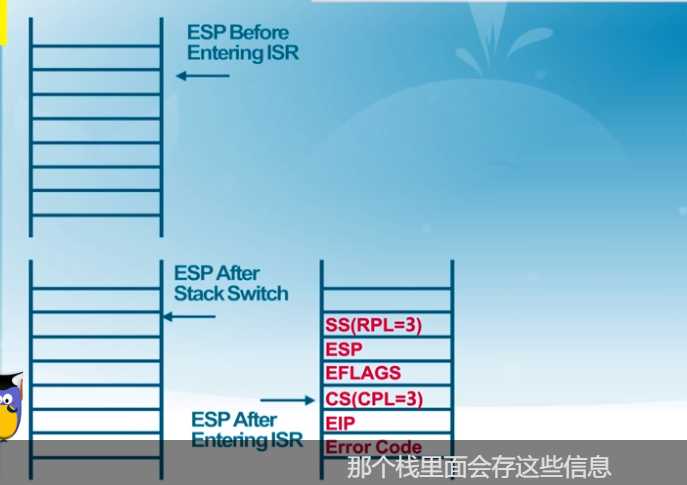

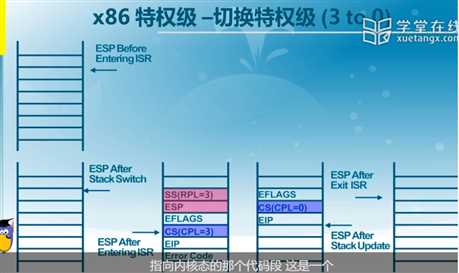

通过中断切换特权级

基于中断的特权级的转换

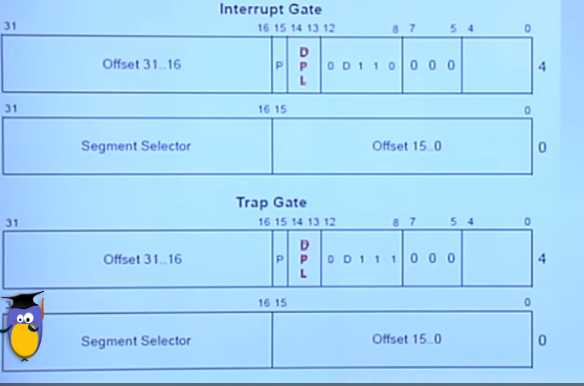

中断门

压栈信息

ring(0 to 3)

特权级的切换

内核态 跳转到 用户态

构造一个特殊的栈

内核栈中产生压栈 step1

模仿ring3 产生中断时的现场

要切换

会多存两个信息。

修改一下CPL 特权级

使用iret 指令把信息弹出栈 将信息付给其他的寄存器

然后就已经到用户态了

从ring3 调到 ring0

中断描述符 中断服务历程

在被打断的那一刻 所保存下来的信息

处理完 ISR IRET就返回了ring3

但是我们可以修改堆栈信息 ,执行完ISR 后留在 ring0就ok 了

LAb1 的changellage 的方式

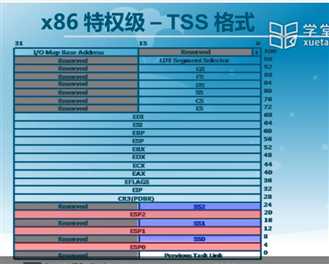

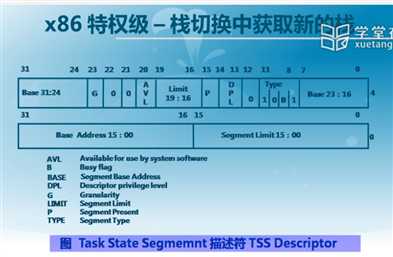

task state segment

保存了不同特权级所用到的信息

我们关注 不同特权级的堆栈信息

cpu 根据TSS 中的信息 设置新的堆栈 根据IDT表跳到新的地址

操作系统要设置好TSS

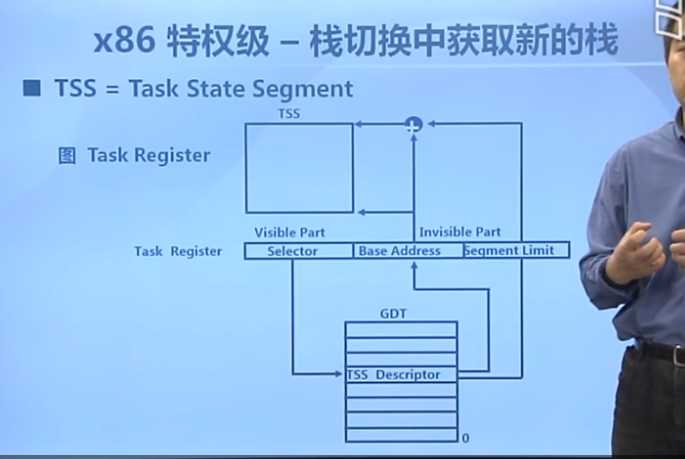

TSS 特殊的一个段 Task State Segment 任务状态段

有一个 TSS 的段

优化 专门有一个 Task Register 保存Tss 的位置 、

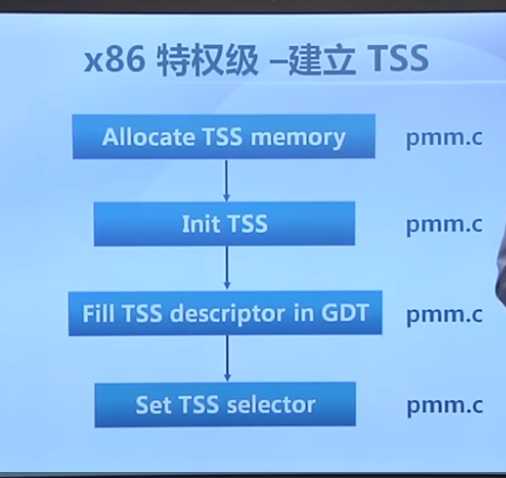

初始化的任务

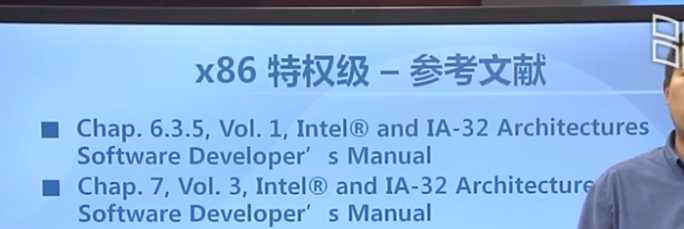

特权级信息的 参考文档

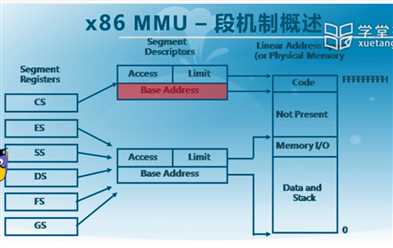

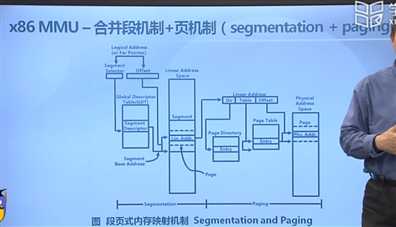

x86 内存管理单元 mmu

段机制概述

x86 mmu -段选择子(segment selector )中的隐藏部分

扩展的段选择子

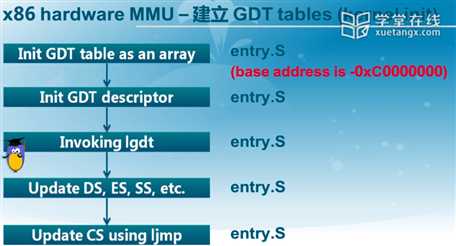

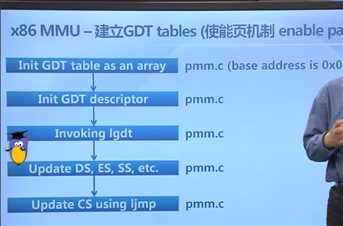

x86 hardward mmu -GDT tables (kernel init)

Lab1 中的映射关系

选择页机制 更有效一些 主流的cpu 都采用的 页机制

不是很懂?

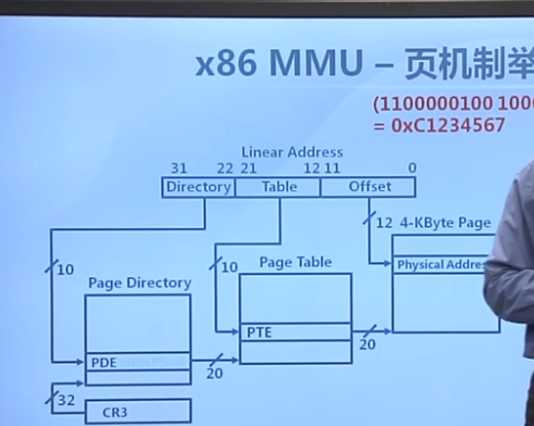

页机制概述

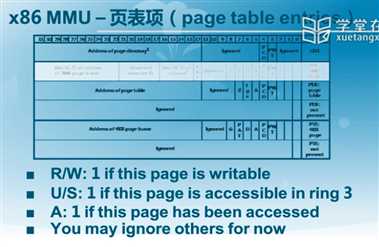

PDE PTE

CR3 里面是页表首地址

页表项里面村的地址是线性地址

页表项: page table entries

高20位是基址 低12位是一些属性

页表就两级

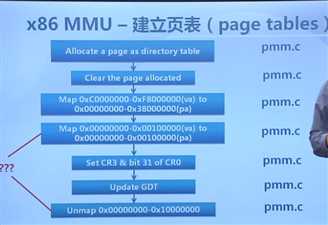

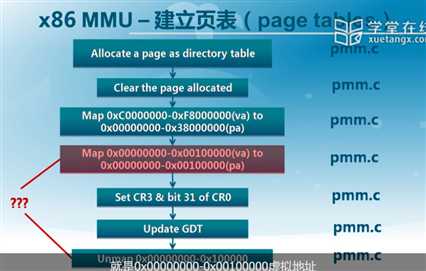

使能 页机制 (enable paging )

cro 第一位保护机制使能

cr0 最高位31 位 启动页机制

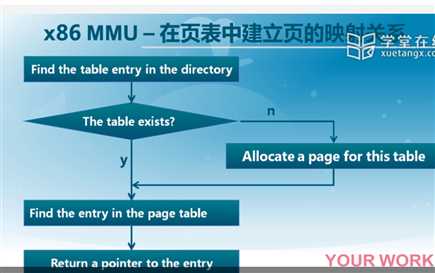

问题:练习 pmm.c 里面实现的

给一个 虚地址一映射到 物理地址

x86 里面非常的全面 段页机制

intel 对应的章节

标签:转换 启动 ble 线性 概述 cto hang tables 状态

原文地址:https://www.cnblogs.com/sfzyk/p/8992870.html