标签:bit sign 常识 说明 systemv out its 大于 精度

截位(rnd/prnd/floor):都是去掉低位数据的操作(去掉低位低精度的数据,或者说小数位,降低数据的精度)

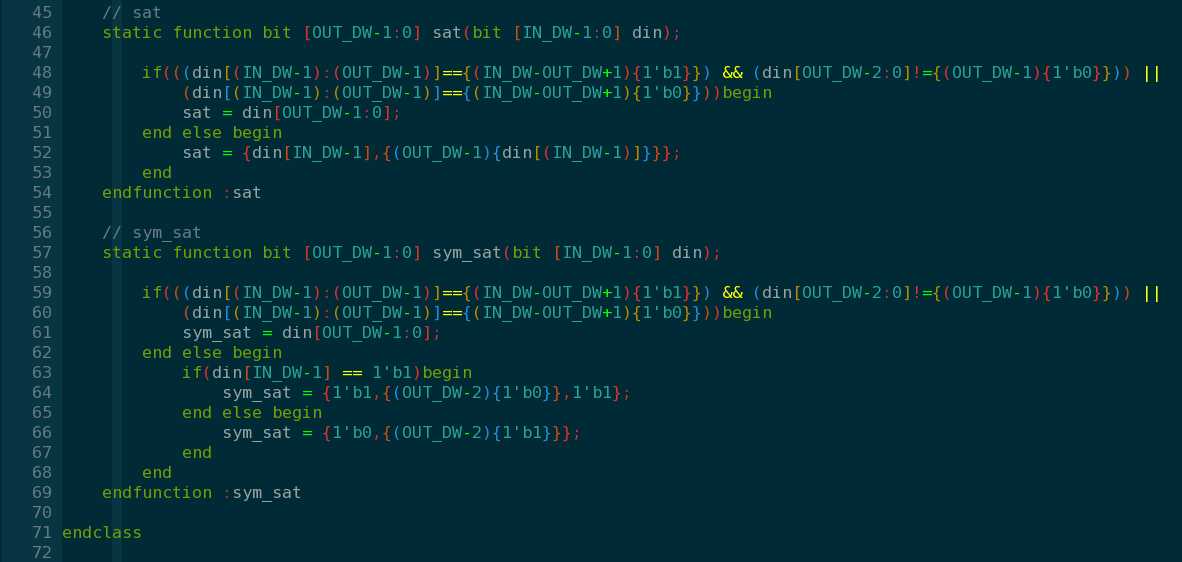

饱和(sat/sym_sat):都是去掉高位数据的操作,(去掉无符号数高位的0,或者有符号数高位多余的符号位)

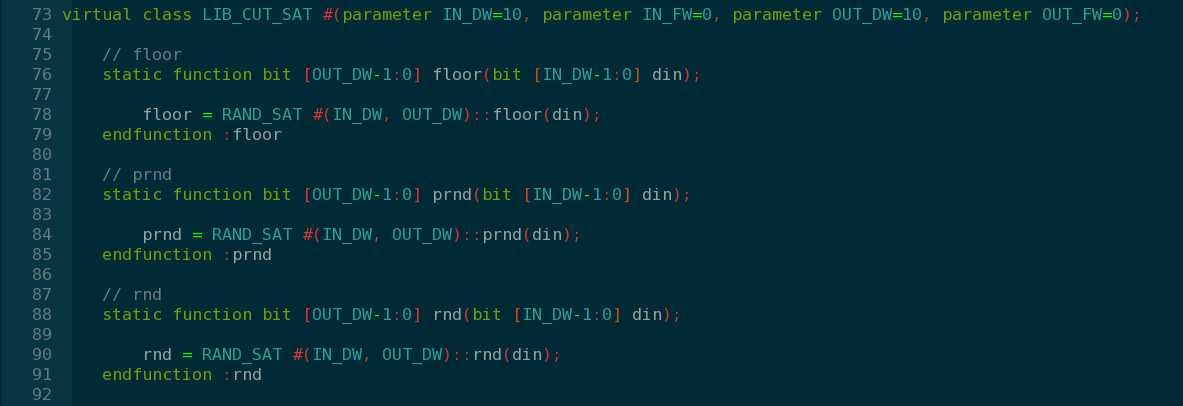

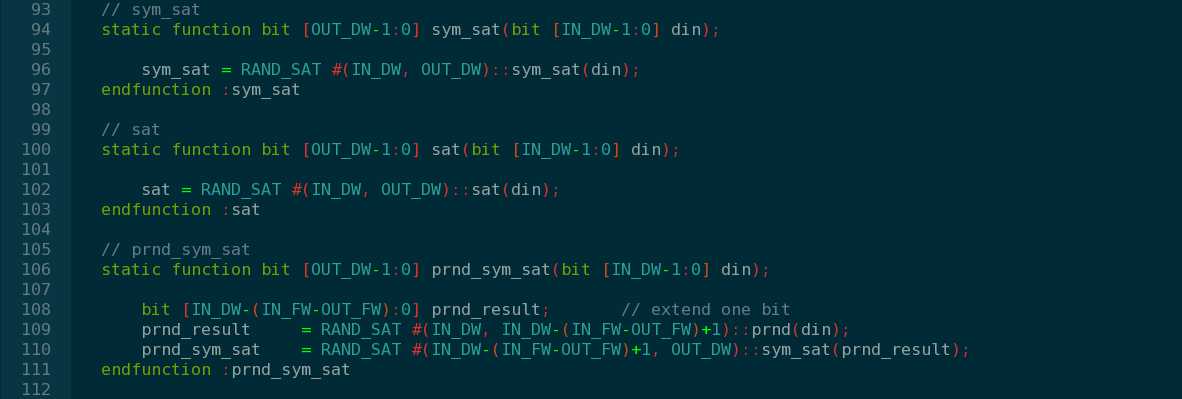

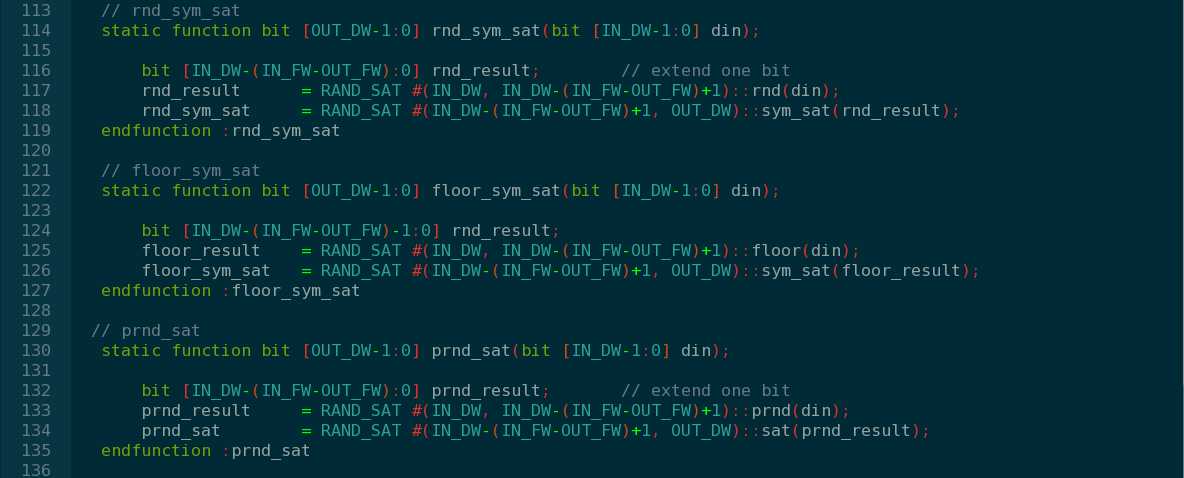

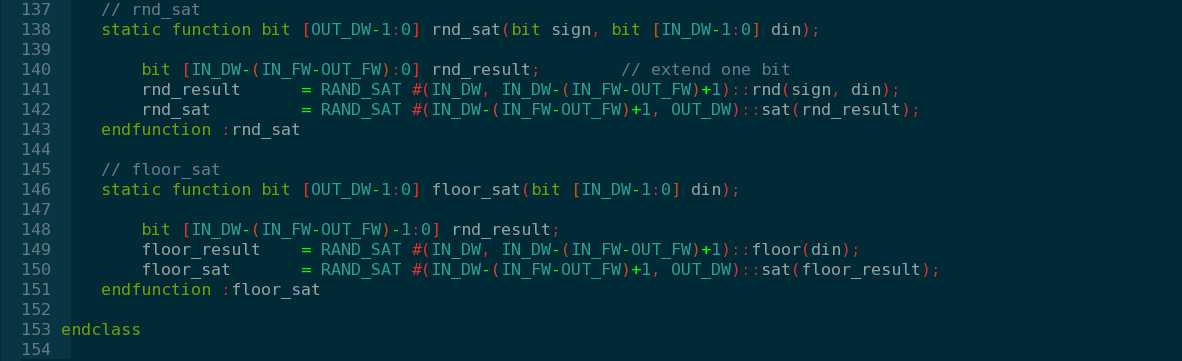

函数说明:

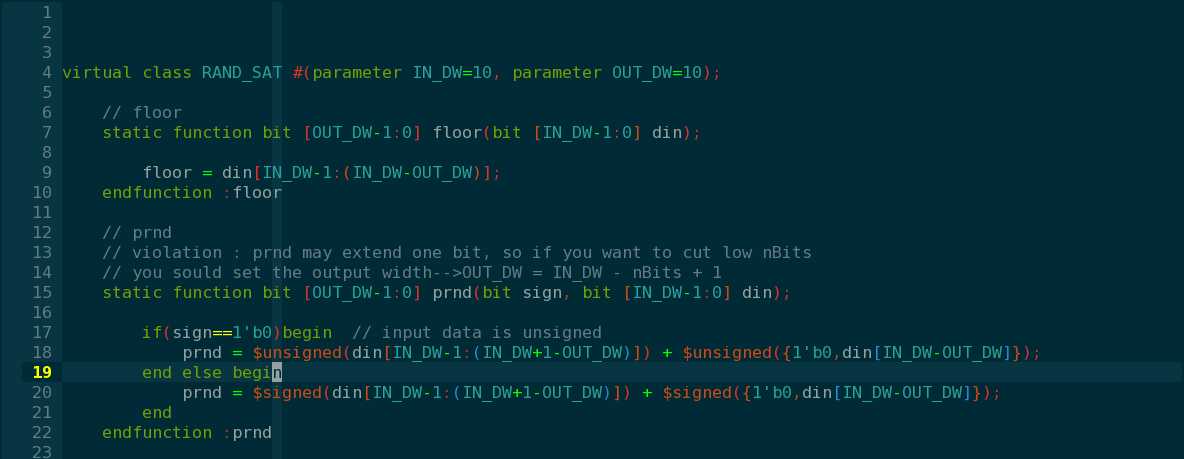

floor:

这个操作很简单,就是把低位直接截掉,精度损失大。有符号和无符号数据都适用用于这个函数,且不需要指示输入的数据是有符号还是无符号。

prnd:

1.假的四舍五入处理,与真正的四舍五入唯一的区别在于,当输入的数据是负数的时候,且要截掉的数据为1xx1xx的时候(要截掉的数据最高位为1,且低位还有1的存在),prnd处理的结果是有误差的。

2.prnd可以处理无符号和有符号数据,输入要指示数据的类型,sign=0表示无符号,sign=1表示有符号数据。

3.prnd处理有加法操作,会扩宽数据位宽,比如一个6bit的数据,你想截掉低3位数据,那么输出的数据位宽应该是4bit,OUT_DW = IN_DW - nBits + 1,4 = 6 - 3 + 1.

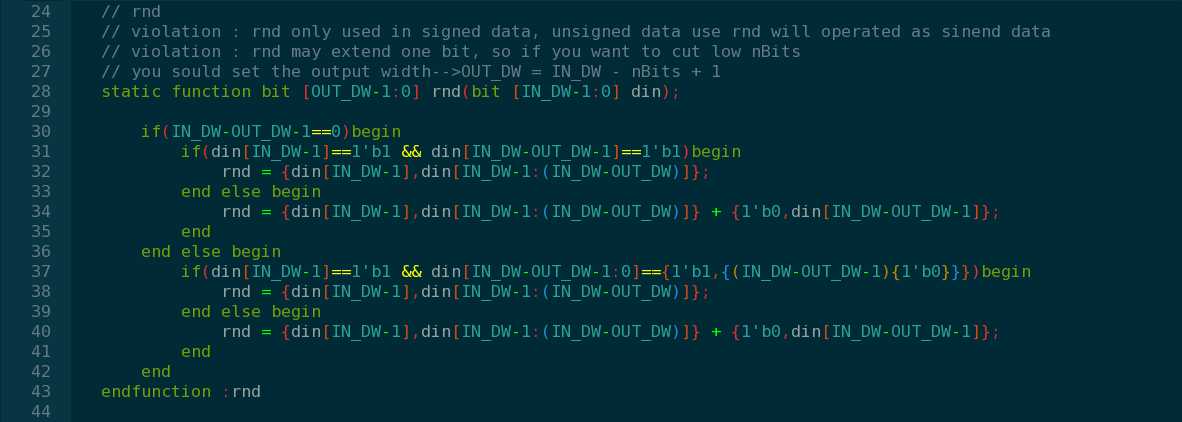

rnd:

1.常规的四舍五入,比prnd精确,但是资源要大些。

2.rnd是对prnd在负数时候出现误差的一个优化处理,所以输入的数据必须是有符号数,输入无符号输出会导致错误。

3.把数据分为保留部分preserve_part和截去部分cut_part,preserve_part=din[IN_DW-1:IN_DW-OUT_DW+1],cut_part=din[IN_DW-OUT_DW]

4.为了好理解rnd中的处理,先普及3个常识,常识1:有符号数中,把一个正数的一位0替换成1会使数据远离原点(使数据增大,替换最高的符号位除外),;把一个负数的一位0替换成1但却是使数据靠近原点(同样会使负数变大)。nbit负数A=n‘b1xxxx的绝对值 ABS = (2^n-1) - unsigned(A) ;也就是说,A作为一个无符号数越大,那么A作为一个负数的绝对值越小。表面越大,实际越小。

5.常识2,四舍五入是对小数小于0.5的往靠近原点方向拉,大于0.5的往远离原点方向拉,0.5-->1,0.4-->0,-0.5-->-1,-0.4-->0

6.常识3,二进制数据中,第一位小数的权重为0.5,那么正数二进制数的 .1表示十进制的0.5,而负数二进制数 .0 表示的是-0.5

5.有了(4,5)中的常识,我们可以很快就知道6bit有符号数A=6‘b111000要比B=6‘b111100更靠近原点。假如6bit数据有3bit整数位,3bit小数位,那么A=-1.5,B=-1.25,若要把小数点截掉,那么A应该截位-2,B应该截位-1

标签:bit sign 常识 说明 systemv out its 大于 精度

原文地址:https://www.cnblogs.com/yuandonghua/p/asic.html