标签:配置文件 手册 观察 init 信号完整性 连接 版权 led wap

FPGA低温不能启动分析

现象描述:在给medium板光端机做低温试验时,分别给发送版、接收板断电重新启动,发现有的板子在-40°可以启动,而有些板子在-20°都不能启动,需要升高温度到0°以上才能启动,此时观察到的现象是指示状态的4个led灯都点亮,表现为FPGA一直处于复位模式。

针对这一问题,作如下分析:

FPGA在上电前是一片空白的芯片,既使断电前FPGA已经配置为一个正常工作的系统了,但只要断电,它又恢复了空白。也就是说FPGA内部的电路逻辑要落实到一个具体的结构需要有电的维持。

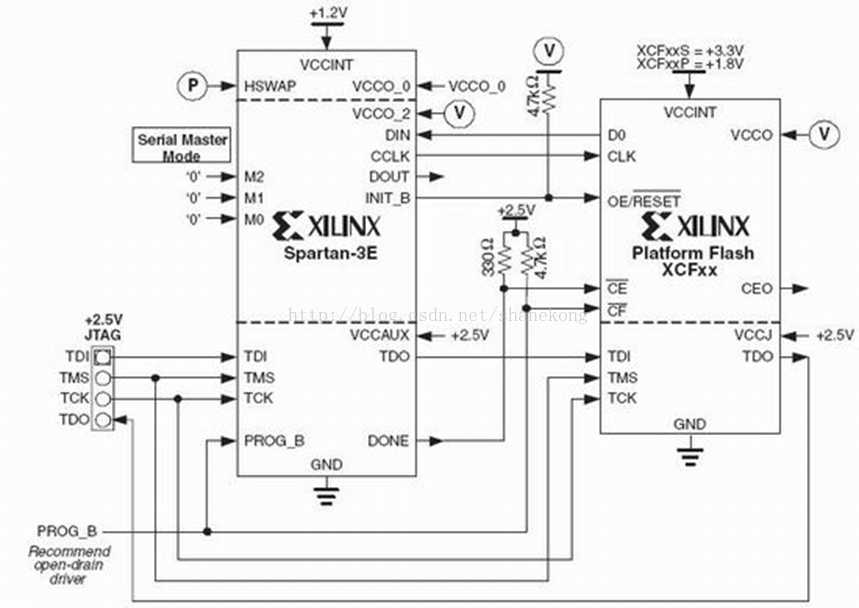

FPGA内部逻辑结构是由配置文件决定的,这个配置文件来自哪儿取决于FPGA使用哪种配置模式。Medium光端机FPGA采用的是主串模式,这是FPGA最常用的配置模式,主串配置模式电路图如下。

Medium光端机使用的FPGA芯片是Spartan3E,PlatformFlash是XCF04S。

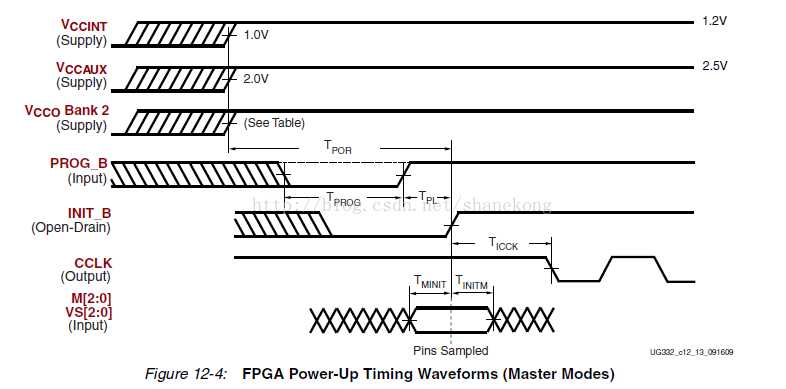

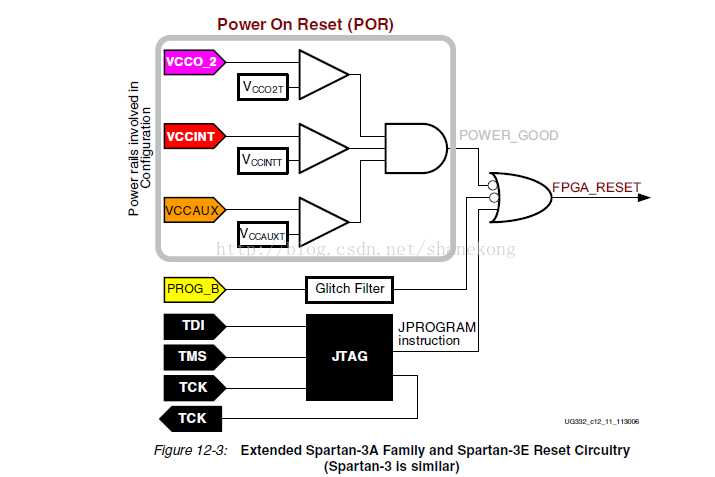

FPGA芯片有两个配置触发事件:上电复位(POR, power on reset),软件复位。低温试验中,我们采用断电重启的方式来检测FPGA是否在低温下可以重新启动,这里主要对上电复位触发重新配置的过程进行如下描述:

(1)FPGA上电后,只有在内核电压、参考电压、IO口电压都正常的情况下,才进入配置模式;

(2)下拉PROG_B,FPGA复位,同时对配置存储空间进行初始化;

(3)将INIT_B,DONE管脚信号拉低,DONE信号与PROM芯片的CE管脚信号相连,从而使PROM片选信号有效;INIT_B为低,指示电源供压正常,FPGA正处于配置存储空间初始化中;

(4)FPGA在PROG_B管脚信号变为高电平时,开始配置过程;

(5)FPGA在INIT_B上升沿中读取配置管脚M[2:0]的值,从而确定FPGA的配置模式;

(6)PROM通过Do管脚将配置数据以CCLK时钟信号的速率传给FPGA

(7)配置完成后,将DONE管脚信号置为低电平,指示配置已经完成。

以下将针对FPGA主串模式配置过程中几个关键的因素进行分析:

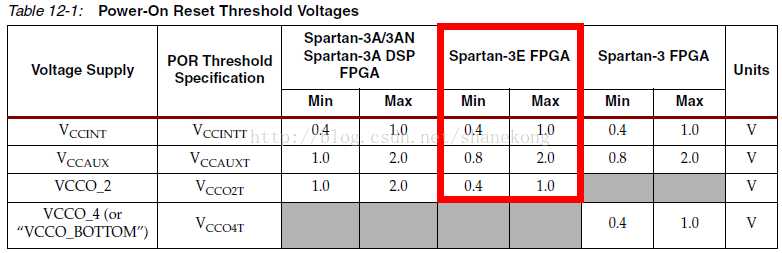

1、POR电压要求

上电复位过程中,如果配置电源电压没有到达门限值,POR电路将保持复位状态。配置电源有三个:

VCCIINT,给FPGA内核逻辑供压;

VCCAUX,给专用配置管脚供压;

VOCC_2,给外部连接的配置数据源(如PROM)接口管脚供压

FPGA检测这三个电压值,一旦所有的三个电压值超出了特定的电压门限值要求,POR上电复位电路会释放对RESET控制,FPGA就可以在PROG_B出现低电平时,启动重新配置。

POR复位电压门限值表

2、配置模式选择:主串模式(Master Serial)

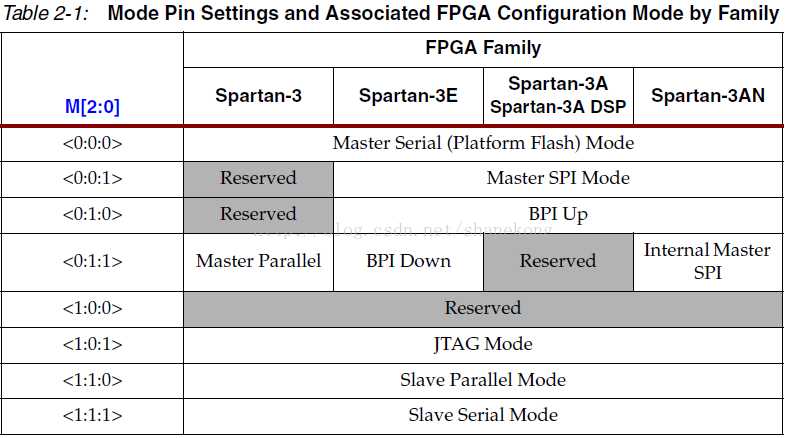

M[2:0]= <0:0:0>,FPGA配置模式选择管脚M[2:0]都应为低电平。在FPGA完成了内部配置存储空间初始化后,FPGAT_B在INIT_B上升沿的时候读取配置模式管脚的电平值,从而确定FPGA的配置模式。

==>查一下M0 M1 M2上的下拉电阻,这些脚FPGA内置的上拉很强,如果外接下拉电阻太大的话有可能下拉电平不够低,加上温度变化造成输入门限电压的变化就可能造成低温的时候不去用SPI Flash 初始化。推荐阻值470欧以下,如果不复用引脚的话,建议直接接地。

3、配置时钟CCLK

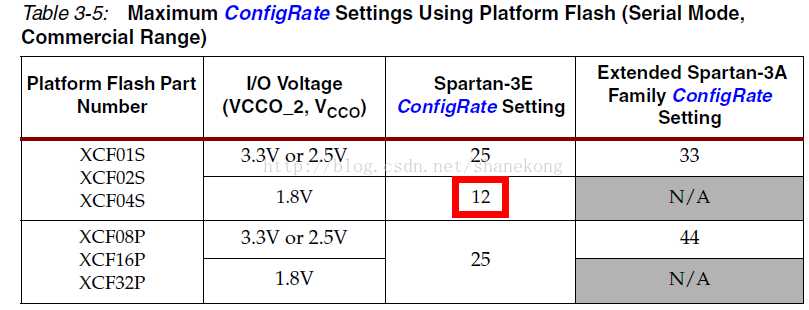

CCLK信号是JATG配置数据传输的时钟信号,其信号完整性非常关键。CCLK是由FPGA内部振荡器产生的,传给Platform Flash PROM的CLK管脚。相应的,PlatformFlash PROM通过DO以CCLK的速率将配置数据送给FPGA。如果CCLK信号没有,重点检查内核供压是否为1.2v。FPGA配置电路刚开始以最低的频率工作,如果没有特别指定,将逐渐提高频率。对于不同芯片和电平,CCLK最大值如下。

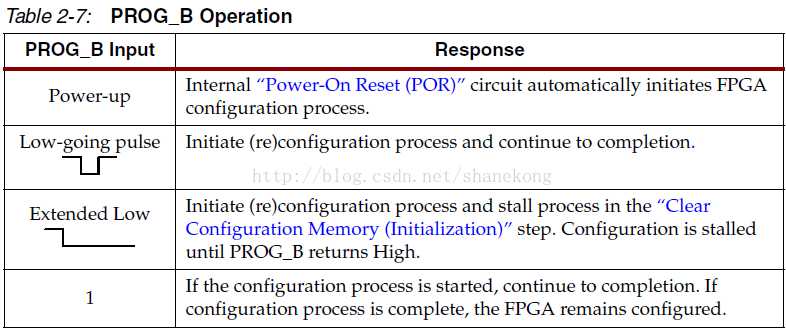

4、PROG_B—FPGA复位或者重新配置

PROG_B对FPGA 来说是一个异步控制输入信号,当PROG_B为低时,FPGA复位,同时对配置存储空间进行初始化;当PROG_B由低变为高时,FPGA开始重新配置过程;重新配置完成后,PROG_B保持高电平,一旦PROG_B出现下降沿,并且低电平持续时间大于500ns时,FPGA将开始重新配置过程。

PROG_B为低期间,IO管脚将表现为何种状态呢。在HSWAP为低电平的情况下,使能上拉电阻,一旦检测到PROG_B出现下降沿时,FPGA的IO管脚将无效,被上拉为高电平。如果HSWAP为高电平,上拉电阻无效,FPGA的IO管脚的状态是不确定的。

==>Medium光端机中,HSWAP通过一个510欧姆的电阻接地,因此HSWAP为低电平,当PROG_B为低电平时,FPGA的IO管脚将被上拉为高电平,此时指示状态的四个LED灯点亮正好说明了这一现象。

5、INIT_B—FPGA配置存储空间初始化指示信号

当电源供压达到电压门限值后,FGPA将INIT_B置为低电平,指示正在对配置存储空间进行初始化。在INIT_B信号由低变为高电平时,FPGA读取配置模式管脚M[2:0]的电平值,从而确定FPGA的配置模式。

在配置过程中,FPGA通过将INIT_B置为低电平来指示配置数据错误,比如CRC出错。

DONE—FPGA配置状态指示信号

当FPGA处于配置过程中时,DONE为低电平;配置完成后变为高电平。可以用来指示FPGA的配置状态。

==>Medium光端机中FPGA的DONE管脚外接240欧姆电阻(推荐值为330欧姆)与 相连,并且另一端外连接一个LED,然后接地。当LED点亮时,表示FPGA已经完成了配置。

6、小结:

通过以上的分析,当FPGA不能正常配置时,可以从以下几个方面进行排查:

1. DONE指示信号LED灯是否亮,亮表示配置完成;

2. 测量电压是否正常,分别有内核电压(1.2v)、参考电压(2.5v)、IO口电压(3.3v);

3. 检查配置模式M[2:0]是否正确,(M[2:0]=<0:0:0>);

4. 使用示波器采集配置时钟信号,看是否正常,低于12M(Spartan 3e + XCF04S)

5. 查PROM的数据手册,PROM--XCF04S可以工作在-40°到+85°的环境下。

7、参考文档:

1.DS312-Spartan-3E FPGA Family Data Sheet.pdf

2.UG332-Spartan-3 Generation Configuration User Guide.pdf

---------------------

作者:shanekong

来源:CSDN

原文:https://blog.csdn.net/shanekong/article/details/29923925?utm_source=copy

版权声明:本文为博主原创文章,转载请附上博文链接!

标签:配置文件 手册 观察 init 信号完整性 连接 版权 led wap

原文地址:https://www.cnblogs.com/limanjihe/p/9782100.html