标签:direct 出现 ons tween evel stream led屏幕 复制 tst

Zedboard OLED Display Controller IP v1

介绍

Author:zhangxianhe

本文档提供了快速添加,连接和使用ZedboardOLED v1.0 IP内核的说明。运行在ARM处理器系统上的测试应用程序用于通过其驱动程序的功能与IP进行通信。 Vivado设计套件被用作开发环境。硬件验证是在Zedboard上完成的,然而,这个IP可以很容易地应用于其他主板或嵌入式系统。

平台

硬件:Zedboard xc7z020clg484-1

软件:Vivado 2016.3(适用于Vivado 2015.4及以上)

过程

A- Creating a project in Vivado to target the Zedboard

1. 双击Vivado2016.3 启动Vivado;

2. 双击Create New Project来新建一个工程,点击Next;

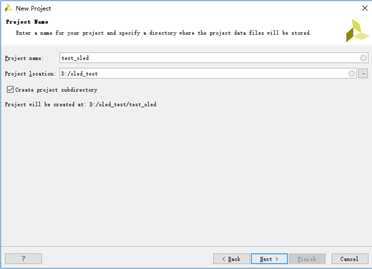

3. 在下一个窗口中输入“test_oled”作为项目名称,项目文件指定存储在 “D:/oled_test”的目录下,勾选Create project subdirectory,点击Next;

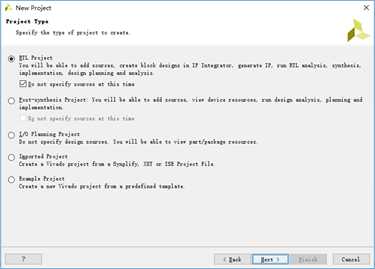

4. 接下来,指定项目类型,使用默认选择的RTL Project,并勾选Do not specify sources at this time。RTL代表寄存器传送语言(Register Transfer Language),通过选择这个选项,我们可以在以后灵活地添加/修改源文件,点击Next;

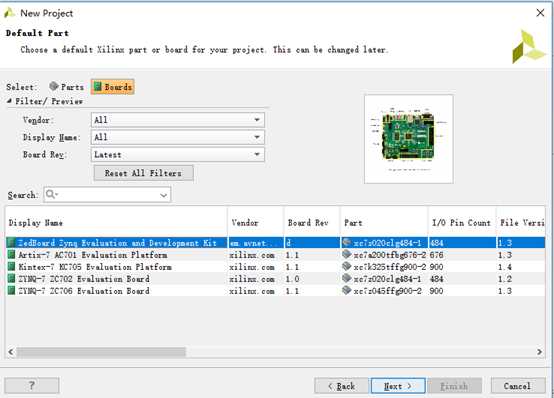

5. 接下来,指定要测试项目的电路板,选择Zedboard Zynq Evaluation and Development Kit,点击Next然后Finish完成;

“新建项目”向导将关闭,刚刚创建的项目将在Vivado中打开。

B- Creating the ARM processor system using the IP Integrator.

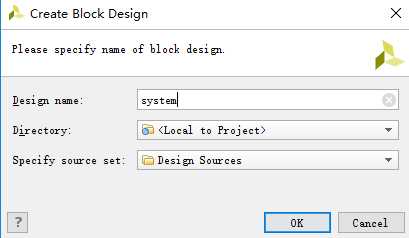

1. 单击Vivado左上方的Project Manager中的Create Block Design;

2. 输入模块的名称,然后单击OK,对于这个例子,使用名称:system;

3. 点击OK后,将会在Vivado中显示一个空白框图视图图形用户界面。在图中,我们将添加所需的硬件块系统。

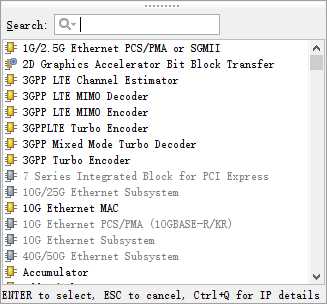

4. 现在,我们将添加包含ARM处理器的ZYNQ7 Processing System块通过启动Add IP 向导来完成,或者可以在程序框图空白处右击选择Add IP..,IP目录窗口将会出现,显示在这个设计中添加所有可能的IP;

向导来完成,或者可以在程序框图空白处右击选择Add IP..,IP目录窗口将会出现,显示在这个设计中添加所有可能的IP;

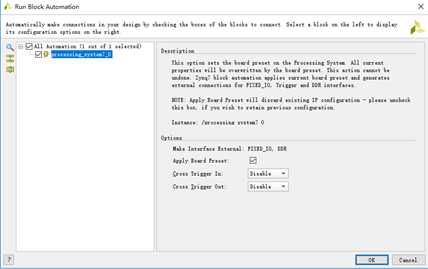

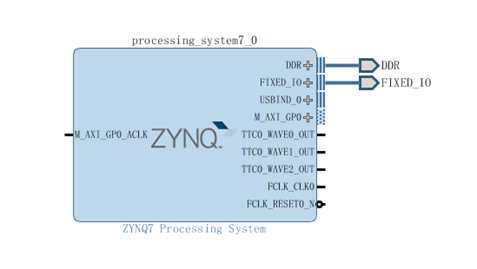

向下滚动到底部或使用关键字zynq进行搜索,双击ZYNQ7 Processing System。 ZYNQ7处理系统块已被放置在框图视图中。程序框图中显示的端口由目标开发板指定的该块的默认设置定义。在绿色信息栏中单击 Run Block Automation。确认processing_system7_0并确保选中Apply Board Preset,然后单击OK。

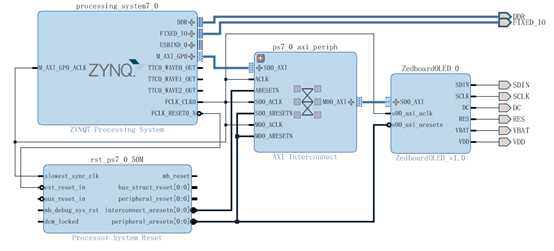

这将为处理系统创建外部端口,并对这些端口应用物理约束,如下图所示

C- Adding the ZedboardOLED IP to the IP repository

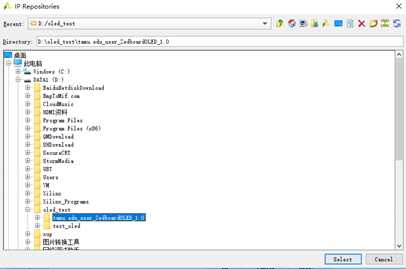

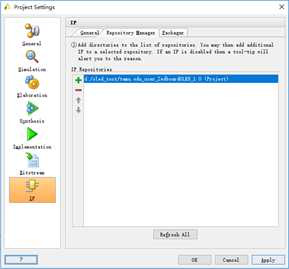

在进程导航窗格中,单击Project Setting选项,选择IP,然后单击Add Repository  按钮。浏览窗口打开,浏览到IP核的位置(D:\oled_test\tamu.edu_user_ZedboardOLED_1.0),然后单击“Select”。

按钮。浏览窗口打开,浏览到IP核的位置(D:\oled_test\tamu.edu_user_ZedboardOLED_1.0),然后单击“Select”。

注意工具如何在目录中检测到新的IP,点击Apply,然后OK。

这样做后,就可以将ZedboardOLED_v1.0添加到当前项目的IP库中,下一步是将其添加到块设计中,并将其从一侧连接到Zynq处理系统,并从另一侧通过使用外部端口连接到OLED板块。

D- Connecting the ZedboardOLED IP core

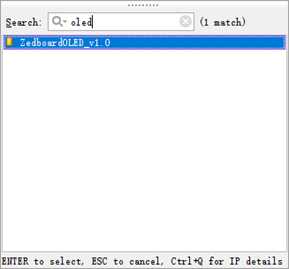

1.在程序框图空白处右击选择Add IP..然后输入“oled”,ZedboardOLED_V1.0将显示出来,双击IP将其添加到块设计中。

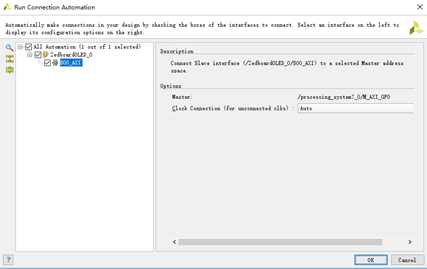

2.看到Designer Assistance现在可以在绿色的信息栏中找到,它将帮助把IP核连接到处理系统的AXI子系统,配置时钟和复位,为IP分配基地址(0x43C00000),并为互连和同步添加必要的硬件;

点击Run Connection Automation并选择/ZedboardOLED_0/S00_AXI。保留Clock Connection设置为Auto,然后单击OK。(默认选择)。

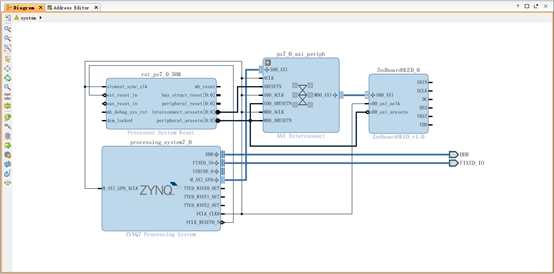

单击 (Regenerate Layout)重新生成布局,程序框图应该看起来类似于这个:

(Regenerate Layout)重新生成布局,程序框图应该看起来类似于这个:

注意到Designer Assistance将AXI Interconnect和Processor System Reset自动添加进来了.将鼠标悬停在ZedboardOLED SDIN端口上,直到它变成铅笔形状,然后右击并选择Make External。(SCLK,DC,RES,VBAT,VDD)端口重复相同的过程。

3.右键单击程序框图上的任意位置,然后选择Regenerate Layout(重新生成布局),这将整齐地组织设计中的块。

最终的布局和如下所示的相似:

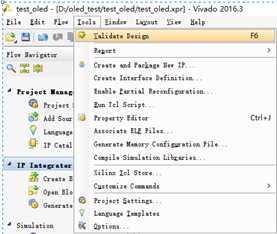

单击Tools,选择单击Validate Design,检查程序框图是否有误,结果直接点击Ok。

4.在源窗格中,选择系统框图“system.bd”,右击并选择Generate Output Products,默认设置,直接点generate,运行结束后,点击OK。

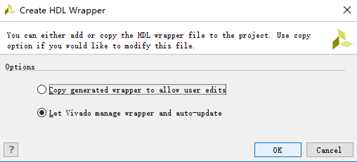

在源窗格中,选择系统框图“system.bd”,右击并选择Create HDL Wrapper,选择第二项 Let Vivado manage Wrapper and auto-update,点击OK,

现在我们通过AXI接口将IP连接到处理系统,下一步是将IP核的外部端口连接到OLED模块的实际Zynq引脚。

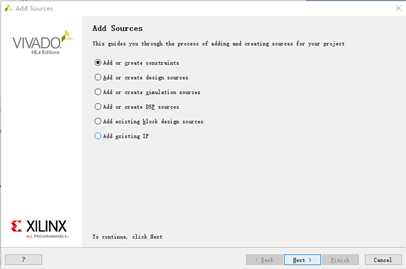

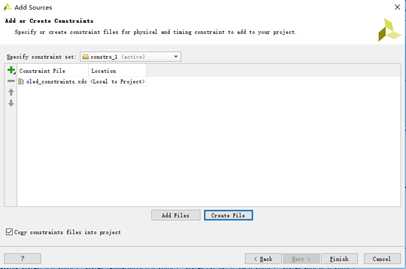

5. 在Flow Navigator窗口中,从Project Manager部分选择Add Sources。Add Sources对话框将打开。选择 Add or Create Constraints。进行管脚约束。

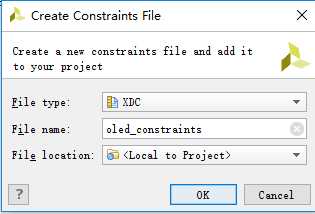

点击 Next,然后点击 Create File, 选择 XDC 作为文件类型然后输入oled_constraints作为文件的名字。

点击OK,点击Finish创建文件并关闭对话框。

在Sources窗口中, 展开Constraints 文件夹并通过双击oled_constraints.xdc来打开新创建的XDC文件。

将下列行添加到约束文件中,或者可以从源文件复制它们文件包oled_constraints.xdc。

1 set_property PACKAGE_PIN U10 [get_ports DC] 2 set_property PACKAGE_PIN U9 [get_ports RES] 3 set_property PACKAGE_PIN AB12 [get_ports SCLK] 4 set_property PACKAGE_PIN AA12 [get_ports SDIN] 5 set_property PACKAGE_PIN U11 [get_ports VBAT] 6 set_property PACKAGE_PIN U12 [get_ports VDD] 7 set_property IOSTANDARD LVCMOS33 [get_ports DC] 8 set_property IOSTANDARD LVCMOS33 [get_ports RES] 9 set_property IOSTANDARD LVCMOS33 [get_ports SCLK] 10 set_property IOSTANDARD LVCMOS33 [get_ports SDIN] 11 set_property IOSTANDARD LVCMOS33 [get_ports VBAT] 12 set_property IOSTANDARD LVCMOS33 [get_ports VDD]

这将ZedboardOLED IP内核的外部端口连接到Zynq器件的特定引脚。特定引脚连接到Zedboard上的OLED模块。按(Ctrl + S)保存约束文件。

E- Generating Bitstream

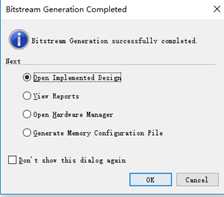

在 Flow Navigator窗口中的Program and Debug部分,单击Generate Bitstream,将出现一个对话框,要求保存所做的修改,单击Save保存;也可能会出现一个对话框,显示“No Implementation Result Available”,单击Yes运行综合和实现。 生成比特流可能会在综合后执行整个实现过程,单击是以在出现提示时运行实现。 实现可能需要一段时间才能完成,具体取决于计算机的性能。

执行Generate Bitstream这个过程时首先会自动进行分析综合和实现。(这里也可以直接先点击Run Synthesis进行综合,然后点击Run Implementation进行实现,然后再点击Generate Bitstream生成比特流) 。完成后,可直接点Cancel.

F- Exporting hardware design to SDK

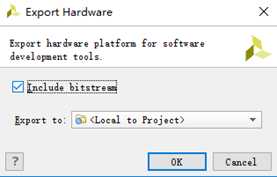

1.点击 File > Export > Export Hardware, 确保勾选Include bitstream 选项

2.选择File>Launch SDK,打开SDK,注意所有与设计相关的文件(包括IP)已经在上一步导出到SDK中,导出的资源中包括ZedboardOLED_v1_0 IP核的驱动。

G- Working with SDK

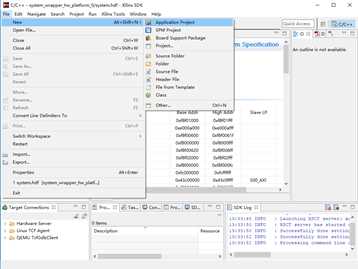

1.在SDK中, 选择File > New > Application Project.

2. 在下一个窗口中, 输入文件名以及默认如下参数:

点击Next,在下一个窗口中,从可用模板中选择Empty Application,然后单击Finish。这将编译BSD和相关的驱动程序。

3. 展开oled_test_bsp>ps7_cortexa9_v2_0>libsrc>zedboardoled_v1_0>src, 然后检查ZedboardOLED.c和ZedboardOLED.h以实现与OLED屏幕一起使用的功能。

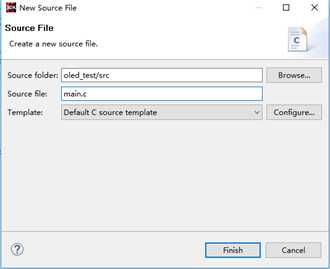

4.现在我们将编写一个使用这些函数的简单应用程序,扩展oled_test目录,右击src目录,选择New-> Source File,在下一个窗口中显示出来,在源文件中输入“mian.c”,然后点击Finish。

复制并粘贴下面的C代码到“main.c”中,点击保存或点击(Ctrl + S),这样oled_test应用程序和它的BSP都会被自动编译,生成可执行文件.elf文件。

1 int main(void){ 2 clear(); 3 print_message("OLED_Test_zhang",0); 4 print_message("NJUPT__xian_he_",1); 5 print_message("PS_And_ARM_PL_S",2); 6 print_message("Anniversary1229",3); 7 return (1); 8 }

Cick Project-> clean (in case you get any errors with the BSD).

H- Downloading the bitstream and running the application (Hardware verifications)

硬件准备:两条USB线,一条连接 micro-usb cable between the PC and the PROG port of the board;另外一条 micro-usb cable between the PC and the UART port of the board,.打开Zedboard板的电源,打开电源之后POWER灯会亮;

1.选择Xilinx Tools-> Program FPGA来下载Bitstream ( this will take few seconds ).

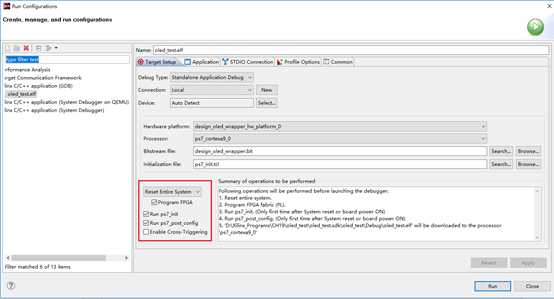

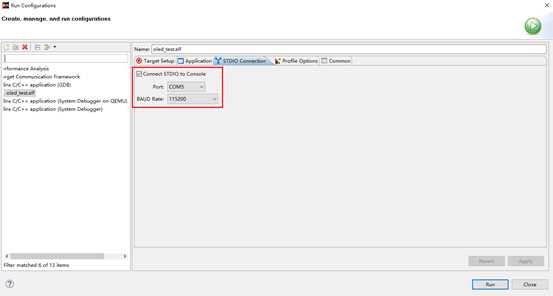

2.右击oled_test 文件夹选择Run As->Run Configurations, 按如下图示配置,(注意STIDIO connection配置时端口号根据自己的电脑进行配置)。单击Apply,然后点击Run。即在ARM processor上运行oled_test application。

运行结果,在OLED屏幕上看到以下消息:

至此,此实验完成。

尝试不同的排版写文档。

如果有同学想要OLED IP核就评论我吧

Xilinx Vivado的使用详细介绍(5):调用用户自定义封装的IP核

标签:direct 出现 ons tween evel stream led屏幕 复制 tst

原文地址:https://www.cnblogs.com/zhangxianhe/p/9800915.html