标签:stm32 准备 发送 col 单片机 简单 address debug模式 receive

在实际应用中,会碰到上位机往单片机发送数据的情况,这时候需要配置单片机为从设备,准备接受数据

使用硬件I2C时,开启事件和缓存中断

I2C_ITConfig(SLAVER_I2C, I2C_IT_EVT | I2C_IT_BUF, ENABLE);

然后在中断服务函数中接受数据

void SLAVER_I2C_EV_IRQ_HANDLER(void) { switch(I2C_GetLastEvent(SLAVER_I2C)) { // EV1: ADDR=1, cleared by reading SR1 followed by reading SR2 case I2C_EVENT_SLAVE_RECEIVER_ADDRESS_MATCHED: { is_data = 0; break; } // EV2: RxNE=1, cleared by reading DR register case I2C_EVENT_SLAVE_BYTE_RECEIVED: { if(is_data == 0) { is_data = 1; reg_addr = I2C_ReceiveData(SLAVER_I2C); } else { is_data = 0; reg_data = I2C_ReceiveData(SLAVER_I2C); } break; } // EV4: STOPF=1, cleared by reading SR1 register followed by writing to the CR1 register case I2C_EVENT_SLAVE_STOP_DETECTED: { I2C_Cmd(SLAVER_I2C, ENABLE); if((reg_addr == 0x22) && (reg_data == 0x47)) LED_D4_TOGGLE; break; } } }

这段代码十分简单,处理EV1, EV2和EV4即可

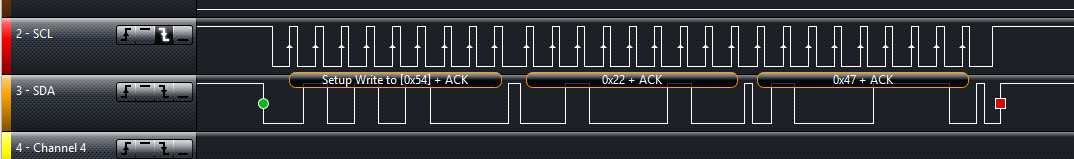

逻辑分析仪截图如下

这次实验是这系列STM32 I2C实验的目的,因为工作项目需要我去移植优化以前的工程,工程中需要配置I2C从设备。但是原来做工程的工程师已经离职,公司又无其他同职位工程师可问,只好自己一步一步调试。最开始,我在开发板上做验证得到的是如下的波形

在我写这篇博客时,BUG已经解掉,还原的BUG是通过修改I2C中断配置

I2C_ITConfig(SLAVER_I2C, I2C_IT_EVT, ENABLE);

即去掉I2C_IT_BUG

现在反过头看这个错误十分愚蠢,但整个解BUG的过程却令人十分痛苦

1、我写代码都力求最精简,去掉无用冗余的代码,在开始对STM32 I2C不甚了解时,我简单地认为I2C中断分为事件中断和错误中断,BUF中断不知道时做什么的,就没用

2、上面的实验时仿照实际使用传输寄存器地址和数据来做,但在之前一直是以写一个数据,即最简单的方式来测试,该测试下,第一次收数据的波形正常,第二次就会出现上面的锁死,且如果开启DEBUG模式,则接受数据一直正常。不知道这是什么原因造成,导致调试十分困难

3、我手头还有一块NUCLEO64的开发板,但单片机型号为STM32F303RE,而它的标准库提供的示例工程代码使用的是CPAL,导致无法用它去验证是否为F1系列硬核I2C本身的BUG,网上有流传STM32硬核I2C有BUG,许多工程师都喜欢使用软核I2C,恰好野火开发板例程也是软核实现

标签:stm32 准备 发送 col 单片机 简单 address debug模式 receive

原文地址:https://www.cnblogs.com/qingkai/p/9822582.html