标签:基本 测试 硬件 了解 目标 处理 编译器 when 计算机

以2选一多路选择器VHDL文件为例:

1 library IEEE; 2 use IEEE.STD_LOGIC_1164.ALL; 3 ENTITY mux21 IS 4 PORT ( a,b : IN STD_LOGIC; 5 s : IN STD_LOGIC; 6 y : OUT STD_LOGIC ); 7 END ENTITY mux21; 8 9 ARCHITECTURE one OF mux21 IS 10 BEGIN 11 y <= a WHEN s = ‘0‘ ELSE 12 b WHEN s = ‘1‘; 13 END ARCHITECTURE one;

VHDL文件的仿真和硬件测试:

VHDL编译器和综合器可以独立地对VHDl文件进行编译和综合,对于编译后得到的标准格式网表文件,如EDIF文件,可用于通过针对特定的目标芯片,如ALTERA公司的某一器件EPM7128S进行适配,如此可获得对应的仿真文件和编程下载文件,前者可用于对程序的设计进行仿真测试,以便了解其逻辑功能是否满足原设计的要求,而后者是对器件EPM7128S的编程文件,可用于实现硬件功能和完成硬件测试。

硬件仿真:

可利用某个EDA平台,例如MUX+PLUSII,将VHDL文件进行编译、综合等处理,然后将mux21的4个引脚信号a,b,s,y锁定于某个具体的目标芯片引脚上,再进行映射适配,即利用计算机,在MUX+PLUSII的帮助下,将程序文件综合后得到的网表文件,配置进该选定的FPGA或CPLD器件中,最后将所得到的配置文件编程下载进这一芯片中,这时芯片就有了如程序所描述的2选1逻辑器件mux21功能。如果对这篇赋予了2选1逻辑功能的器件进行实际的测试,即为硬件仿真。

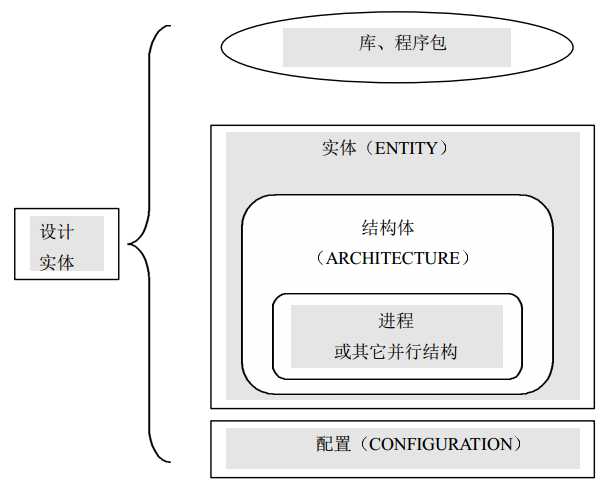

VHDL语言描述器件最基本不可缺少的三个层次chen:

1.库(LIBRARY)说明

1 library IEEE; 2 use IEEE.STD_LOGIC_1164.ALL;

2.实体(ENTITY)说明

1 ENTITY mux21 IS 2 PORT ( a,b : IN STD_LOGIC; 3 s : IN STD_LOGIC; 4 y : OUT STD_LOGIC ); 5 END ENTITY mux21;

3.结构体(ARCHITACTURE)说明

1 ARCHITECTURE one OF mux21 IS 2 BEGIN 3 y <= a WHEN s = ‘0‘ ELSE 4 b WHEN s = ‘1‘; 5 END ARCHITECTURE one;

程序结构说明:

标签:基本 测试 硬件 了解 目标 处理 编译器 when 计算机

原文地址:https://www.cnblogs.com/BIT-taozhen/p/9858526.html