标签:存在 style href mic always 图片 lambda表达式 data long

https://mp.weixin.qq.com/s/OmQRQU2mU2I5d-qtV4PAwg

二选一输出。

参考链接

1.创建Mux.java, 并生成构造方法和logic()方法

略

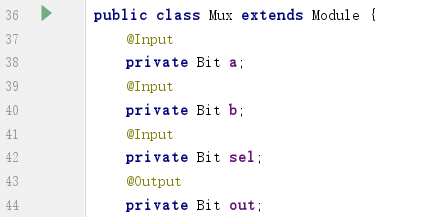

2. 根据逻辑原理,添加输入输出接口

? ?

?

输入输出线作为类成员存在。使用注解标明是input port还是output port。

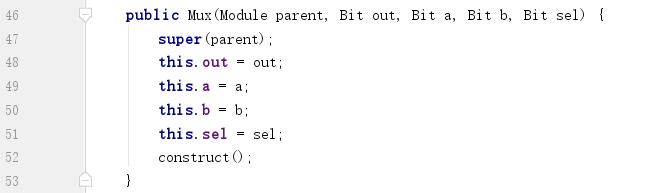

3. 在构造方法中搜集输入输出线并调用construct()方法

? ?

?

首先调用父类即Module类的构造方法,以构建模块hierarchy。

然后逐个把输入输出参数与input/output port对应上。

然后调用construct()方法构造模块(调用一次logic()方法,搜集模块的assign/always代码块、子模块)。

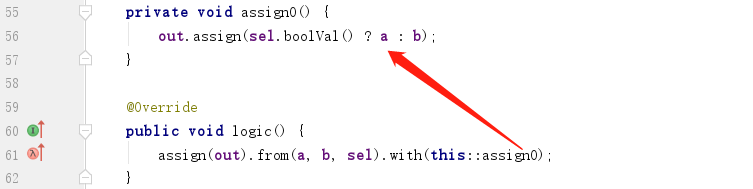

4. 在logic()方法中创建assign/always代码块,以及子模块

? ?

?

这里包含一个assign代码块:当发生a, b,sel的变化事件时,执行lambda表达式的方法,以更新out的值。

5. 创建inst静态方法方便后续使用

略

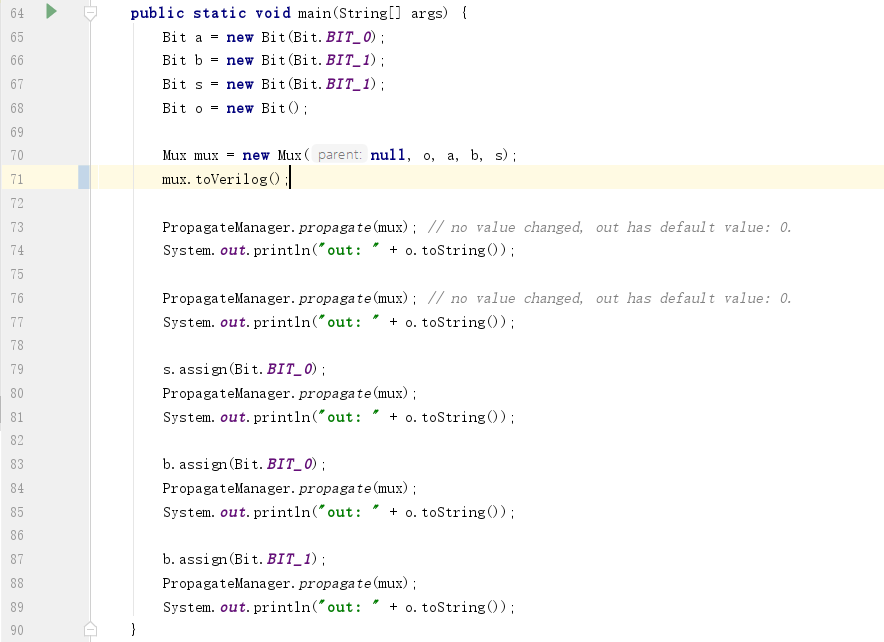

6. 创建main方法执行验证

? ?

?

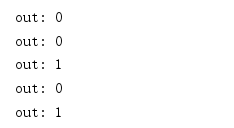

运行结果为:

? ?

?

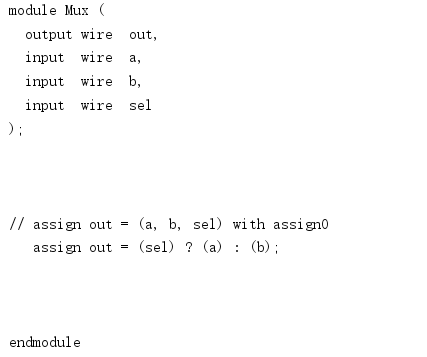

7. 生成Verilog

生成定制化模块名:

略

调用toVerilog()方法生成Verilog实现。

略

执行结果如下:

? ?

?

jchdl - RTL实例 - Mux

标签:存在 style href mic always 图片 lambda表达式 data long

原文地址:https://www.cnblogs.com/wjcdx/p/9934532.html