标签:表达 http 逻辑 计算机 加法 最简 write family res

处理器的设计步骤

具体设计步骤

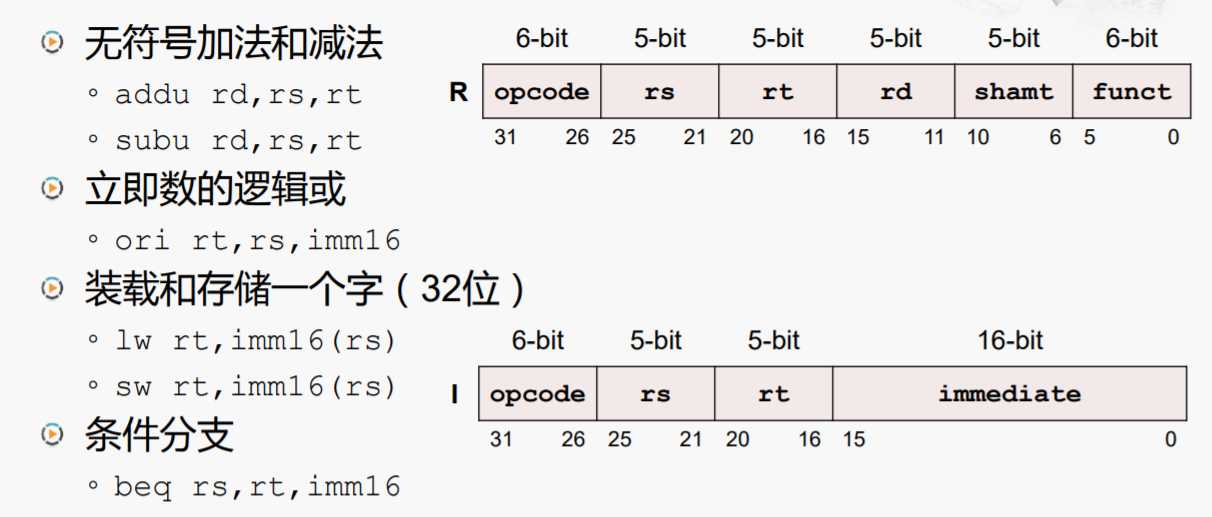

MIPS的所有指令是非常多的,我们只实现其简化版,包含如下6种:

需求分析,需要存放指令地址的32位寄存器(PC),需要存放指令的存储器,可读,数据和指令均为32位(MEM[PC])。还需要一个寄存器堆,用来保存源操作数和目的操作数,一个ALU进行运算。

所以我们需要如下组件:

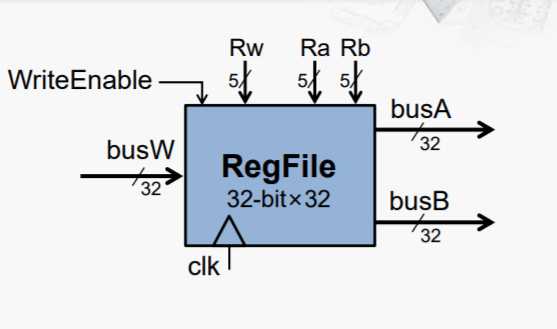

寄存器堆

内部构成是3个32位寄存器。Ra(5位):寄存器编号,将该编号寄存器的内容放到busA。Rb(5位):寄存器编号,将该编号寄存器的内容放到busB。Rw(5位):寄存器编号,在时钟上升沿,如果写使能信号有效,将busW的内容存入该寄存器。

busA和busB:两组32位的数据输出,busW:一组32位的数据输入

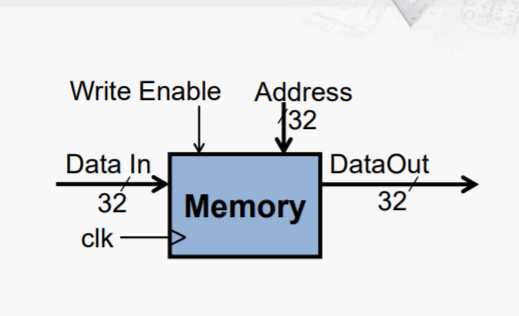

存储器

Address:32位的地址信号,该信号指定一个存储单元,将其内容送到数据输出信号。Write Enable:写使能信号,在时钟上升沿,如果写使能信号有效(为1),将数据输入信号的内容存入地址信号指定的存储单元。

Date In:32位的数据输入信号。Date Out:32位的数据输出信号。

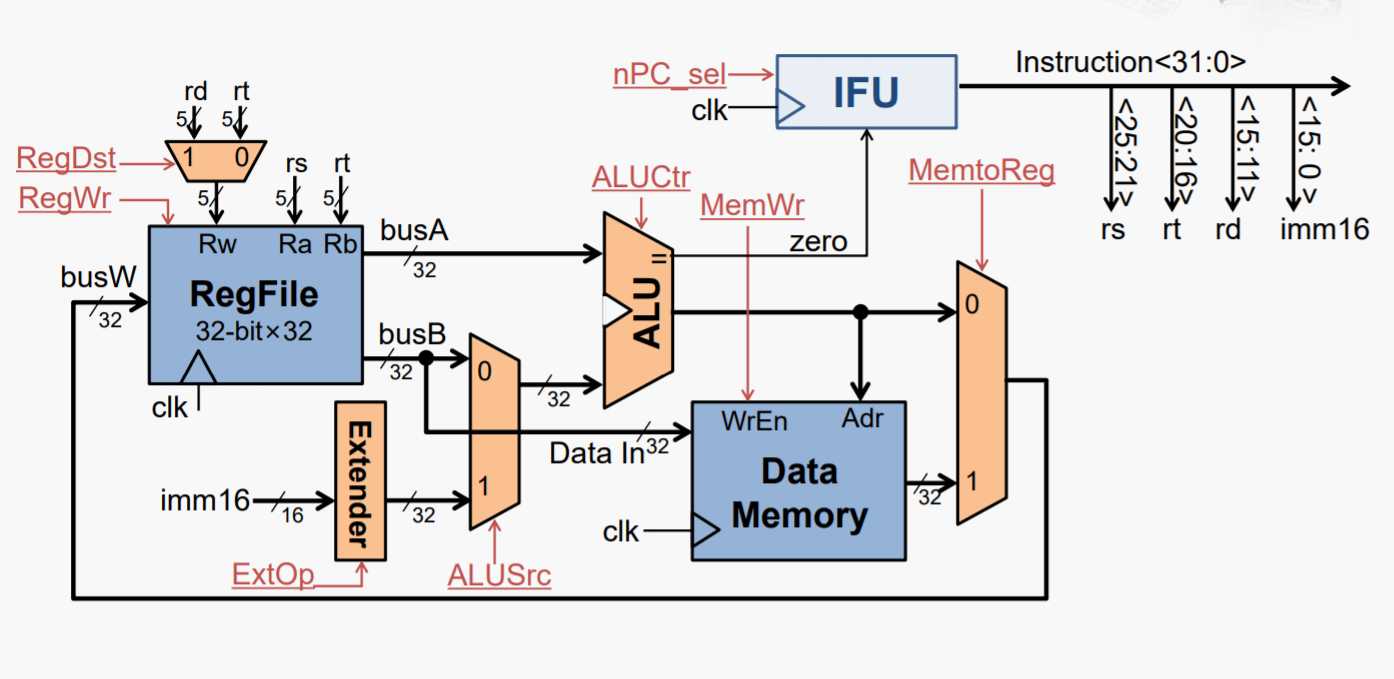

建立数据通路,即根据指令的需求连接组件。指令的需求包括所有指令的共同需求、不同指令的不同需求。

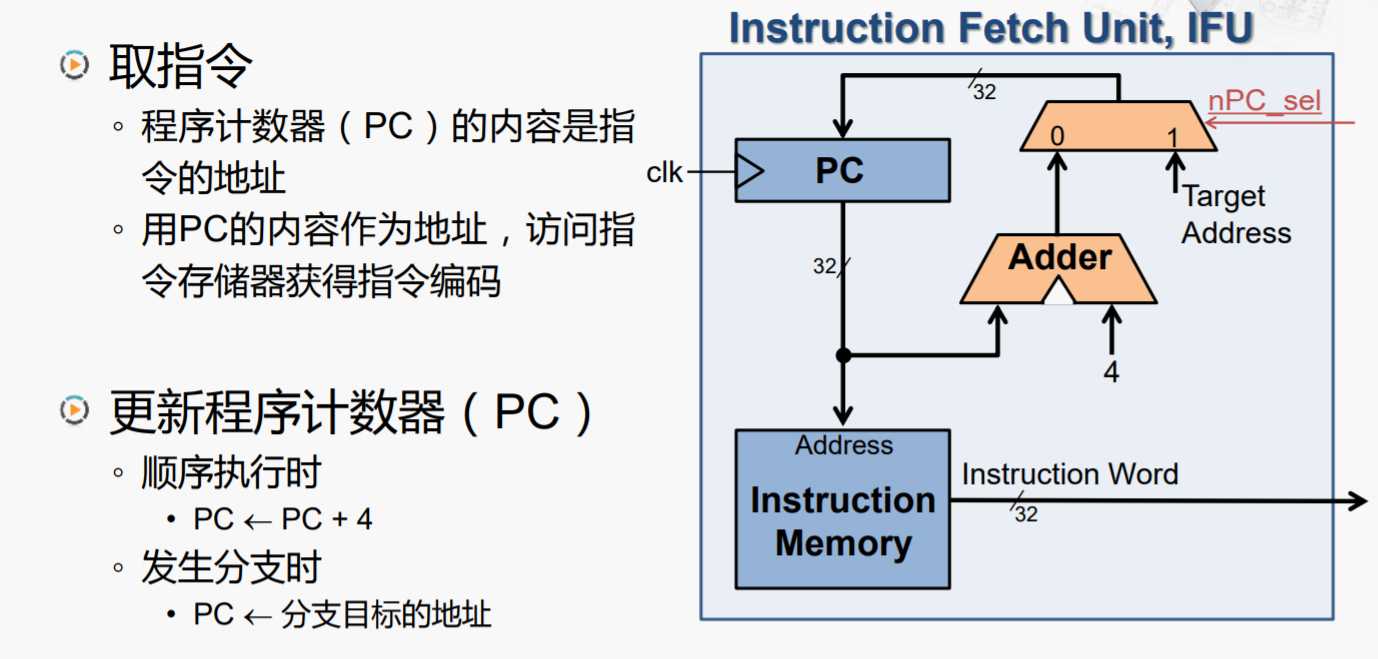

所有指令的共同需求

主要包括取指令和更新PC

不同指令的不同需求

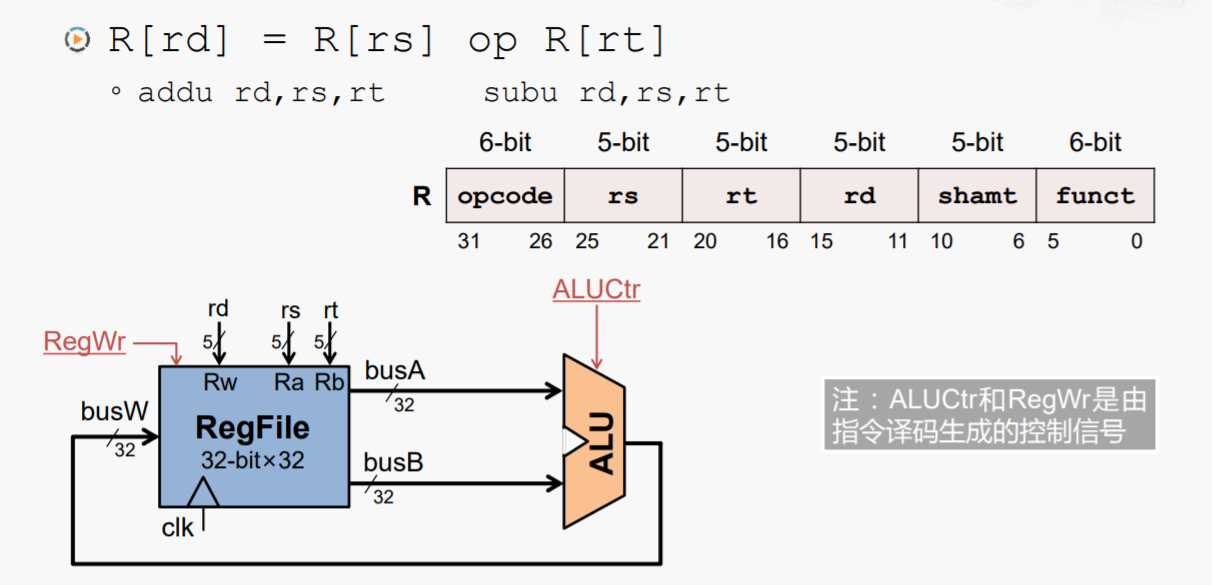

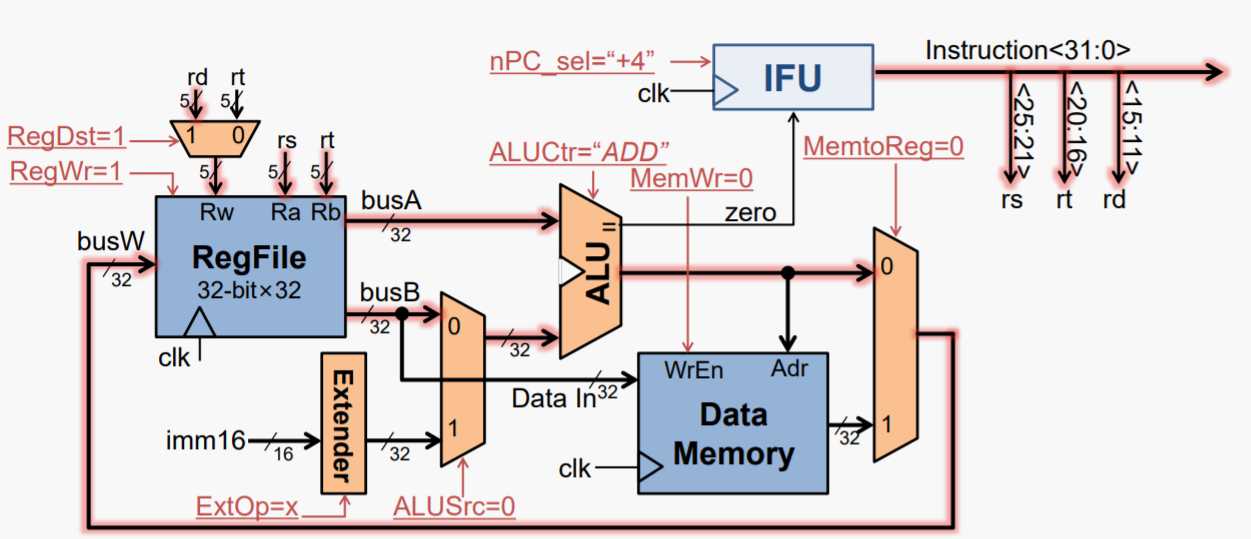

加法和减法指令的需求是最简单的

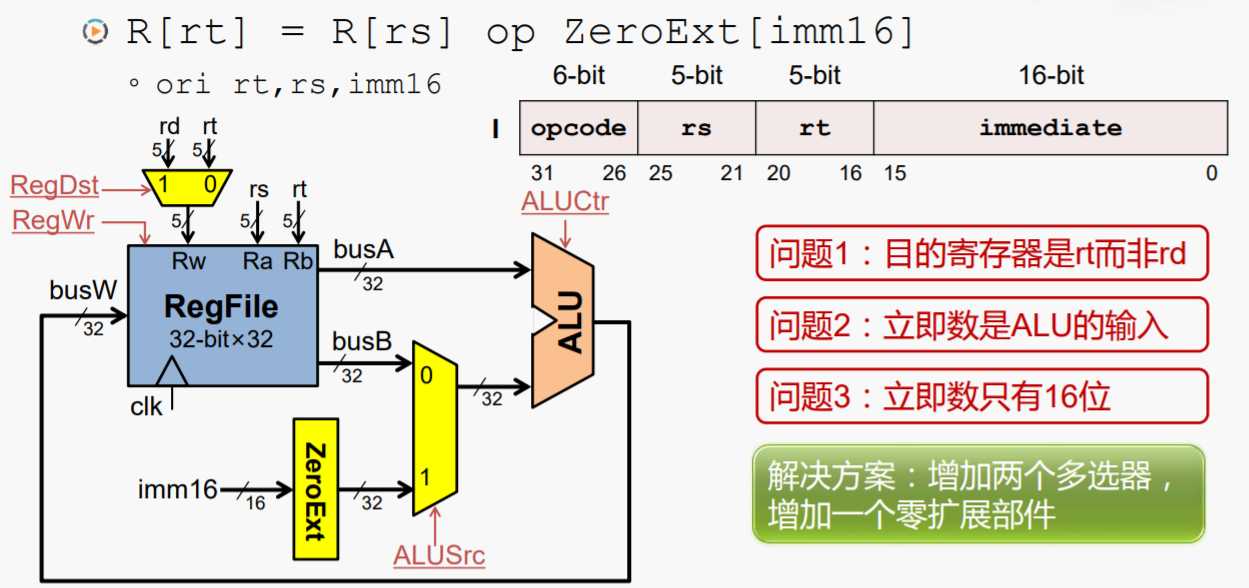

逻辑运算指令有立即数参与,需要增加两个二路选择器,一个选择数据输入来自寄存器还是立即数,另一个选择目的寄存器是rd还是rs

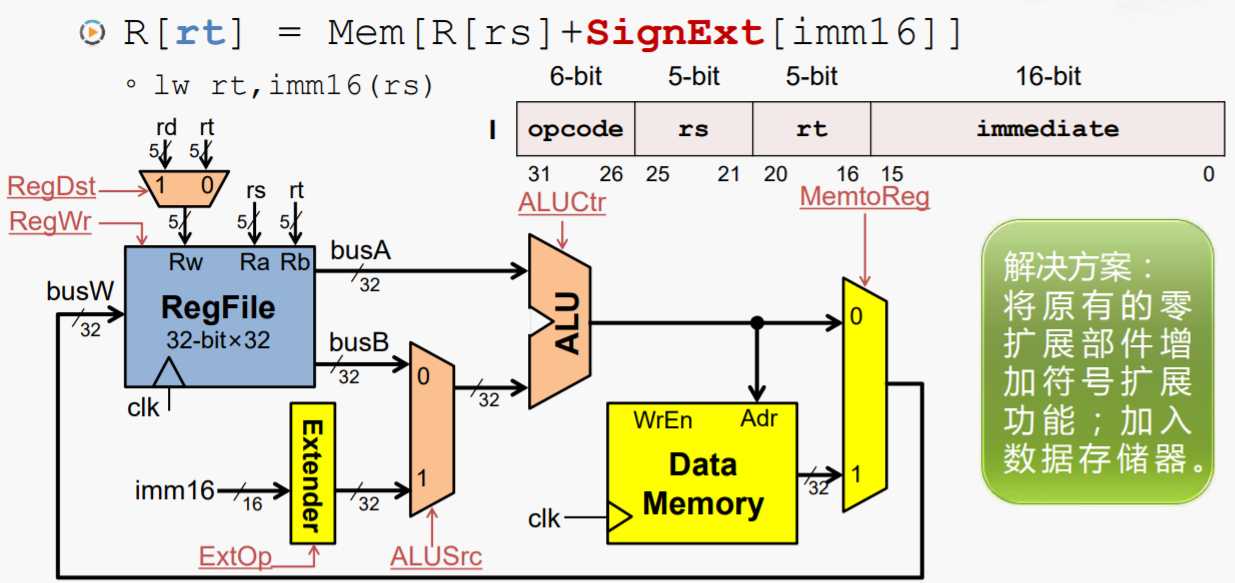

访存指令需要对立即数进行符号扩展,同时需要一个数据存储器用来读取和写入数据

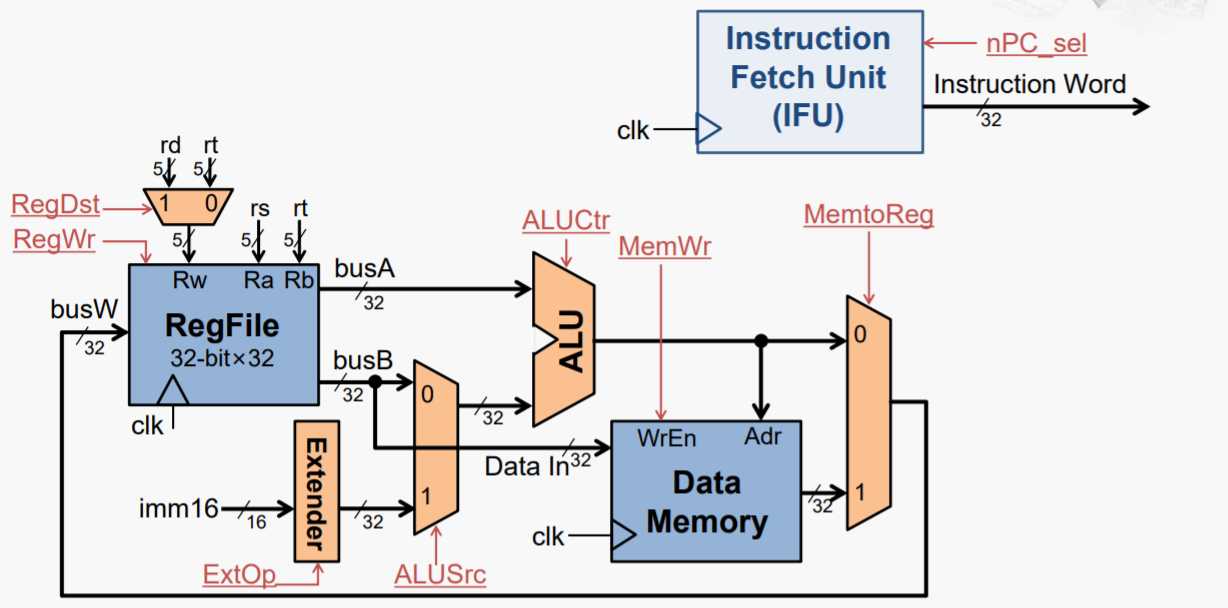

数据通路初步完成

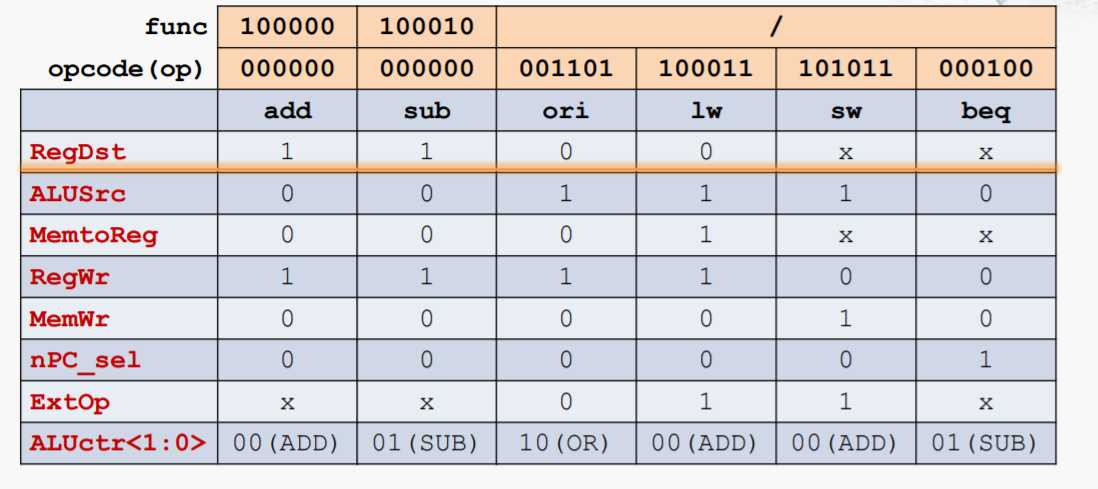

现有指令所需的控制信号

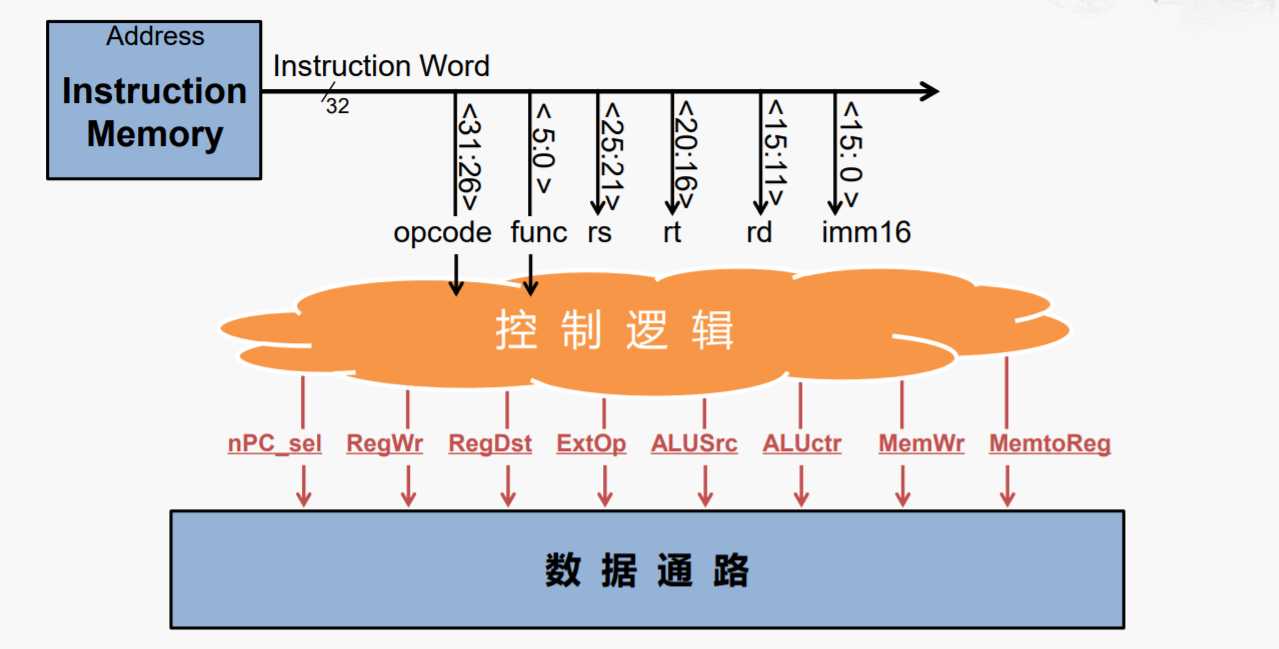

控制信号哪来的呢?肯定来自指令。我们说opcode和func决定了指定功能,理所当然,控制信号也由它们决定。

opcode和func决定了8个信号

以add指令(add rd,rs,rt;PC = PC + 4)为例,看需要将哪些信号设为有效,哪些设为无效,哪些任意。如图所示

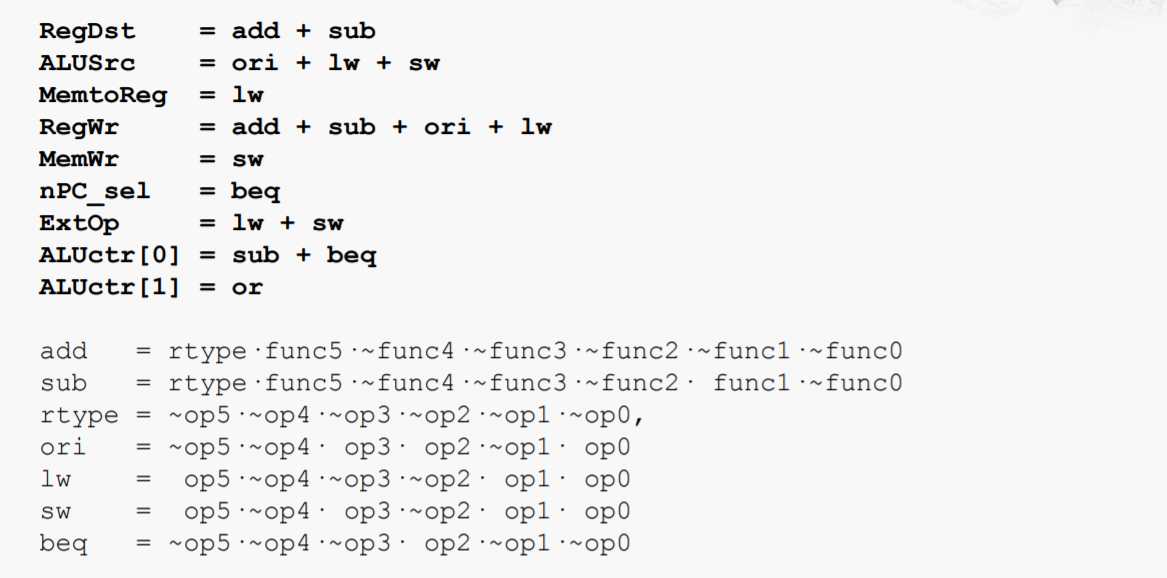

用同样的分析方法,我们可以得到其它的指令的信号设置,它们的逻辑表达式如下:

根据数字逻辑的知识,我们很容易求出每个控制信号关于opcode和func的逻辑表达式

例如,求$RegDest$,按行观察

$RegDest = add + sub$

$add = rtype · func5 · ~func4·~func3·~func2·~func1·~func0$

$sub = rtype · func5 · ~func4·~func3·~func2·func1·~func0$

$rtype = ~op5·~op4·~op3·~op2·~op1·~op0$

同理可得到其它表达式的逻辑表达式

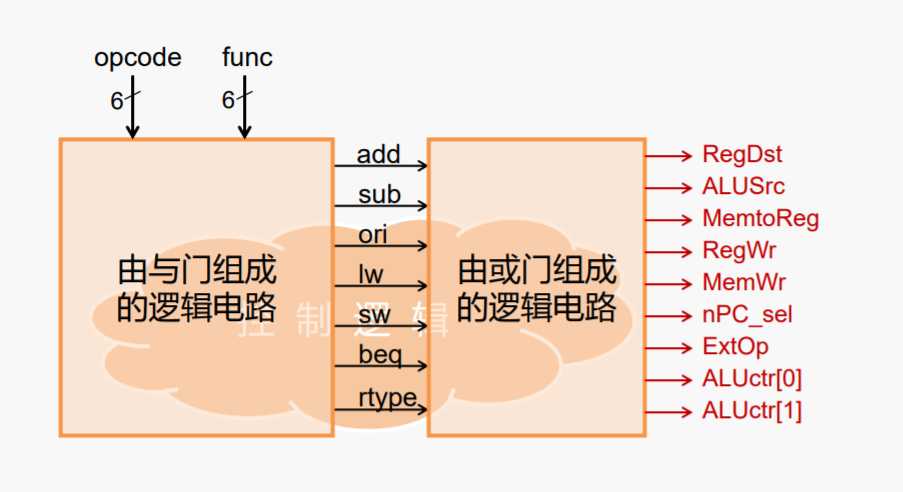

观察发现,这些表达式都是先相与、再相或,所以可用如下的电路来实现

参考链接:https://www.coursera.org/learn/jisuanji-zucheng/lecture/kRJer/506-kong-zhi-xin-hao-de-ji-cheng

标签:表达 http 逻辑 计算机 加法 最简 write family res

原文地址:https://www.cnblogs.com/lfri/p/10050089.html