标签:更新 取出 image ref 分享图片 应用 分解 编码 存储器

流水线的基本原理

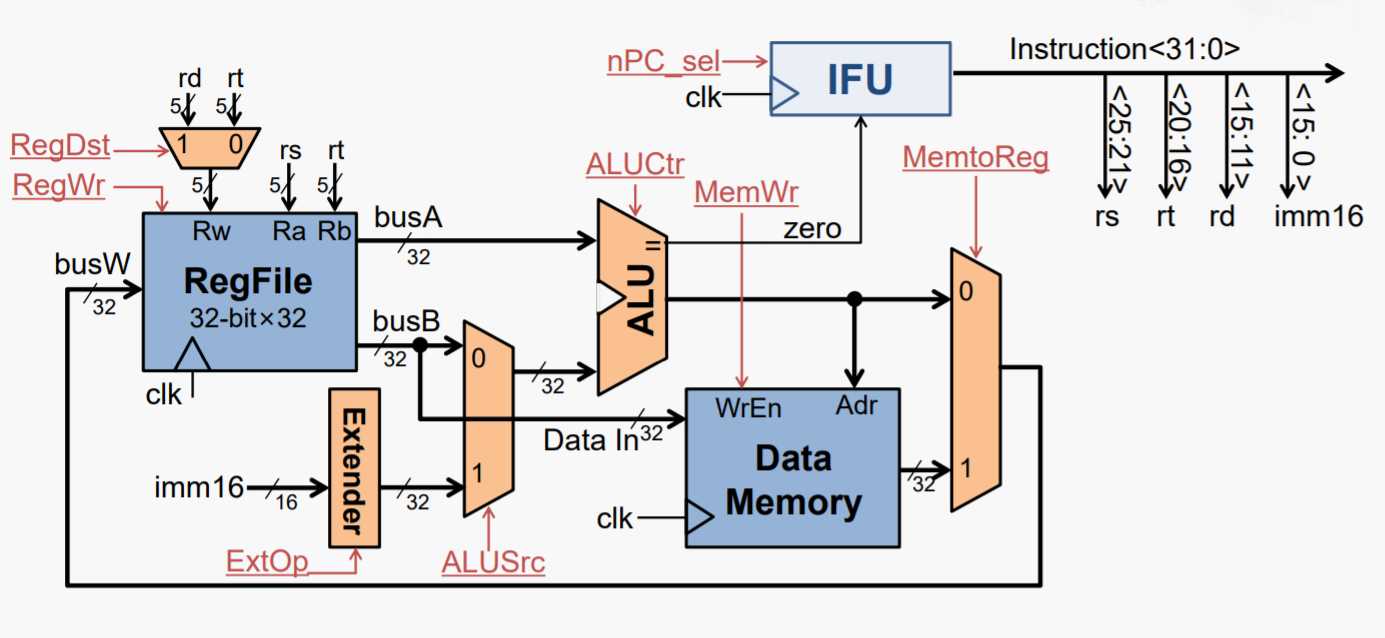

这个是之前设计的单周期寄存器,它已经能正确的执行MIPS指令。

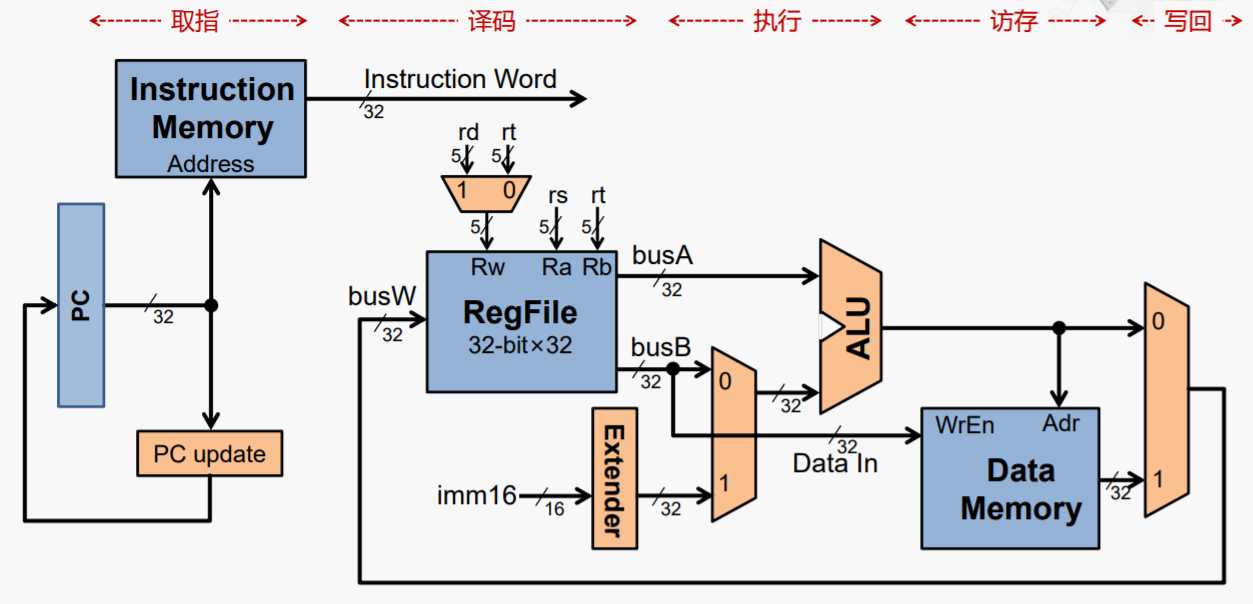

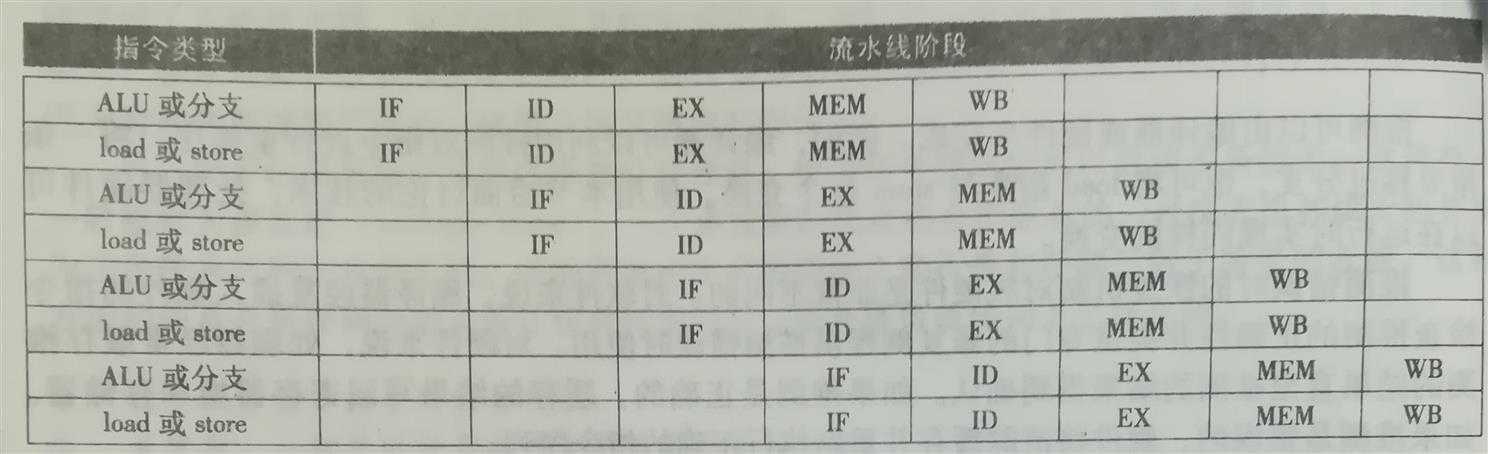

而MIPS的指令可以分成如下5个阶段:

与示意图结合如下:

全在这个图里:

实际上,流水线并不会缩短单条指令的执行时间(甚至会增加时间),而是提高指令的吞吐率(单位时间进多少指令,有多少指令完成)。

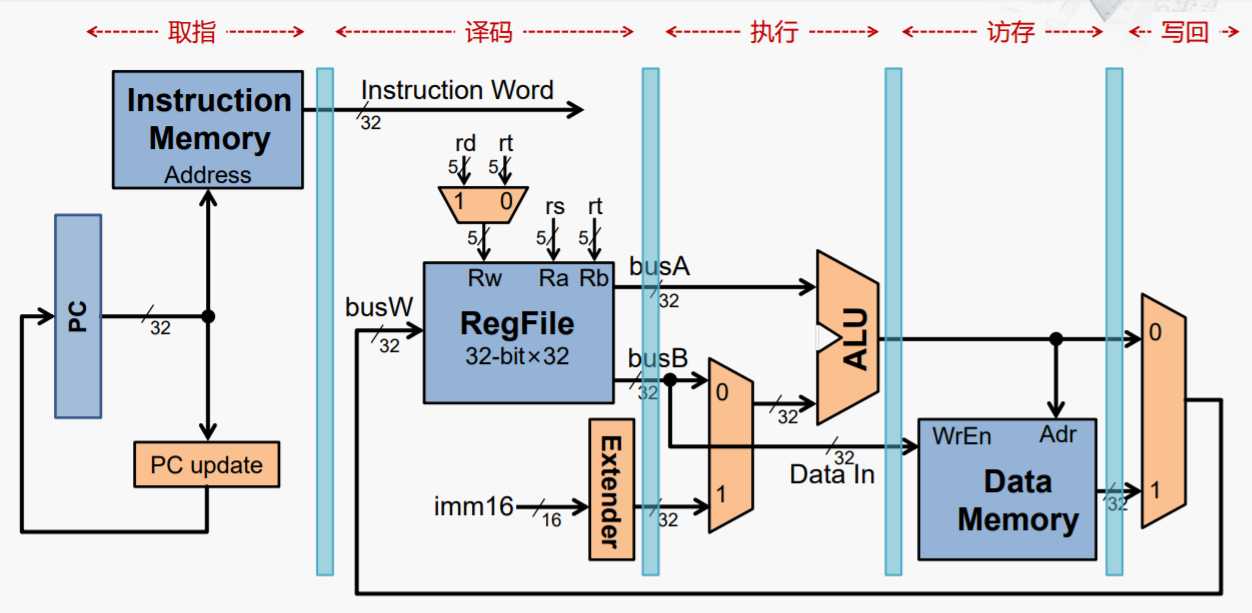

我们要改造成流水线寄存器的话,我们发现每个阶段所需的硬件资源基本是独立的,如果我们能把指令存储器输出的指令编码事先保存下来,那我们就可以提前更新PC寄存器的值,并用这新的值去指令存储器当中取出一个新的指令,而在取新指令的同时,刚才取出的那条指令的编码就会被分解成不同位域,而寄存器堆也会根据输入送出对应寄存器的内容。所以需要添加流水线寄存器。

流水线寄存器:保存了前一个阶段要向后一个阶段传递的所有信息。

所以每过一个时钟周期,都可以更新寄存器的值,而不会影响当前的执行过程,当前执行所需要的全部信息都保存好在流水线寄存器中。

在两个阶段之间添加流水线寄存器后,如图:

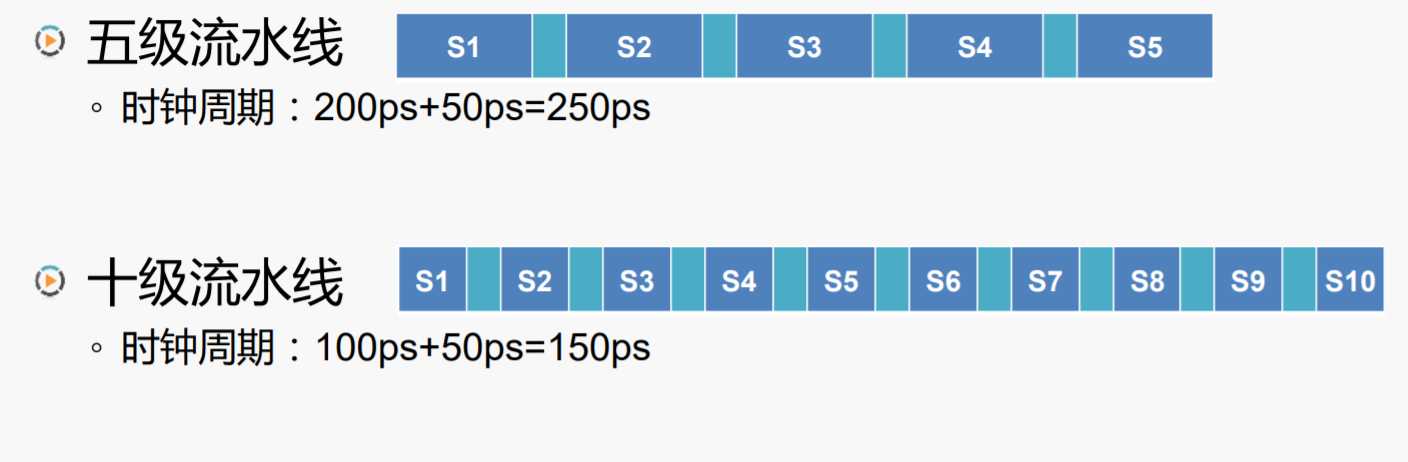

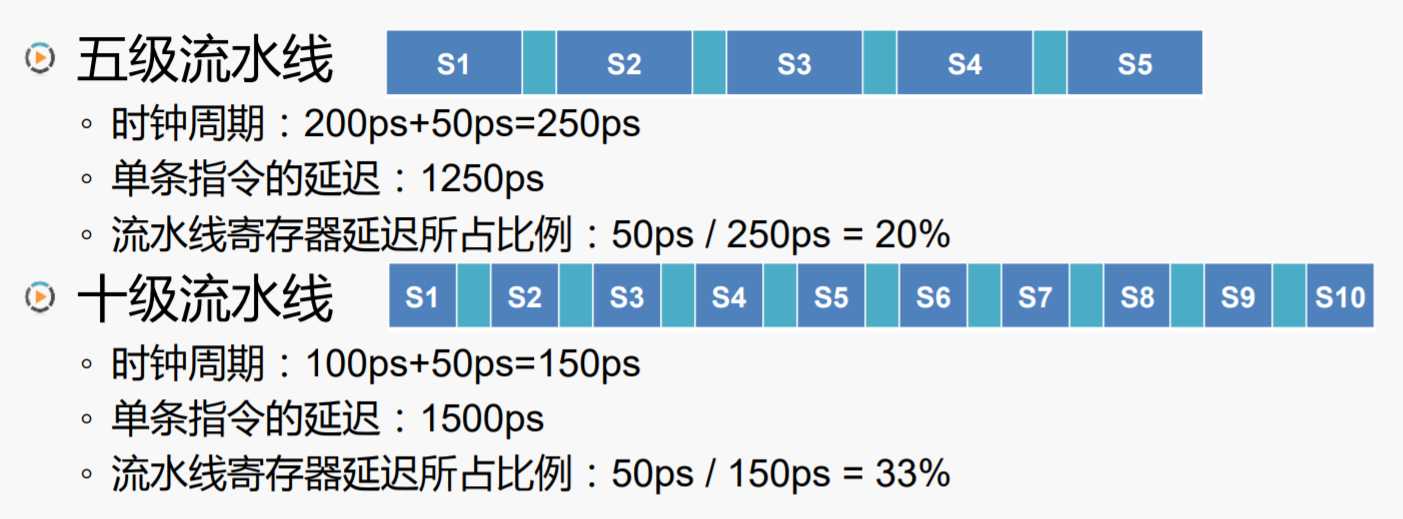

性能分析,与之前的流水线相比,多了流水线寄存器的延迟,周期200到250ps。

流水线的优化

“超级流水线”技术:将五级流水线细分为更多的阶段,增加流水线的深度。

这样缩短了周期,从而提升了时钟频率,从而提高了指令吞吐率。

流水线的级数是越大越好吗?肯定不是。级数越大,所用的流水线寄存器相应增加,单条指令的延迟增加,流水线寄存器延迟比例增加;填满流水线的指令条数更多,指令之间的关系更加复杂。

超标量流水线

超标量结构:通常,将具有两条或两条以上的并行工作的流水线结构称为超标量结构,亦称为“超标量流水线”或超标量。

如图,我们对每个阶段扩大一倍,那么可以同时对两个指令进行操作。第一、二条指令同时进入阶段一,经过一个时钟周期,第一、二条指令进入阶段二,同时第三、四条指令进入阶段一......这样每个阶段两条指令并行前行,到第五个周期就有两条指令同时被完成。

像这样两者并行的结构叫作双发射的结构。按这种方式扩大,就能得到三发射、四发射,这就是超变量流水线寄存器的原理。

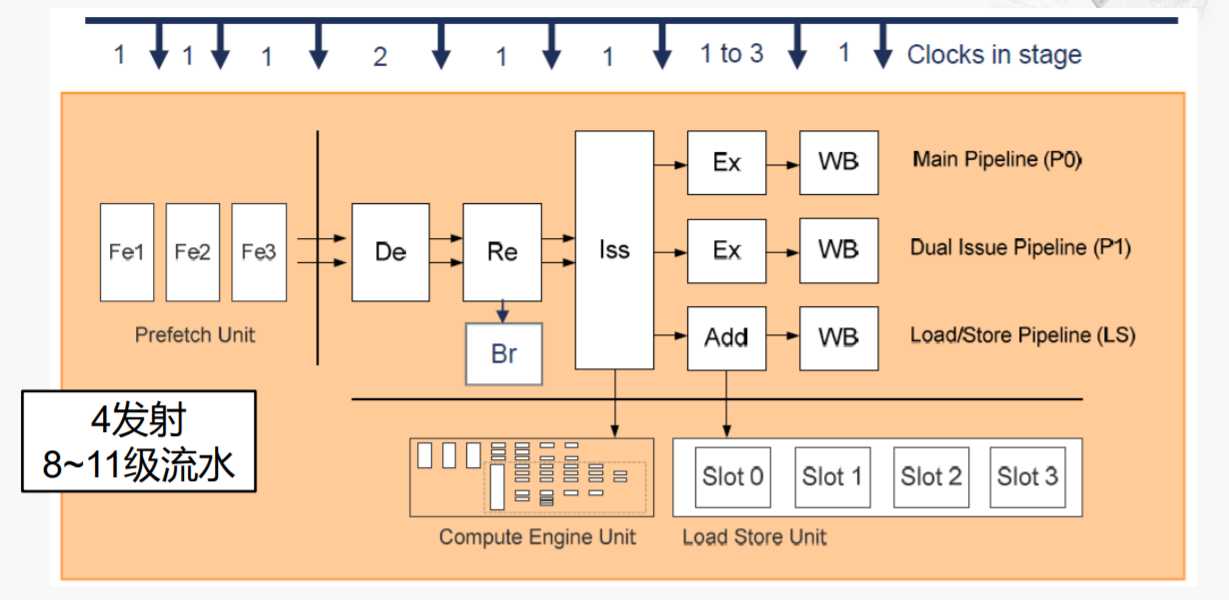

ARM Cortex-A9的超标量流水线

它每个时钟周期可以发射4条指令,根据指令的不同,总共会经过8~11级流水线。在流水线的前端比如说 取指,译码并没有分成多条流水线而是采用统一的部件。当然我们要知道这些部件虽然看上去是一个,但它实际上比标量流水线要大得多,比如说取指部件至少一次要能取来四条指令甚至更多,而译码部件一次也至少应该完成四条指令的译码,而到了流水线的后端, 才会从结构表示上体现出多条并行流水线的形态。

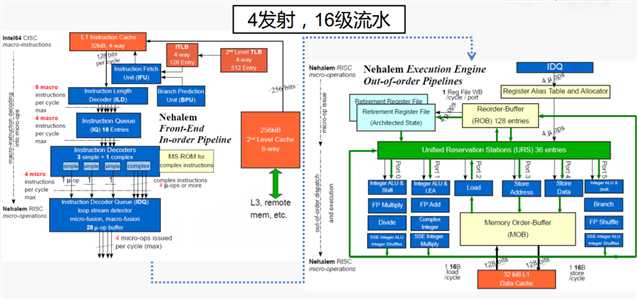

Core i7的超标量流水线

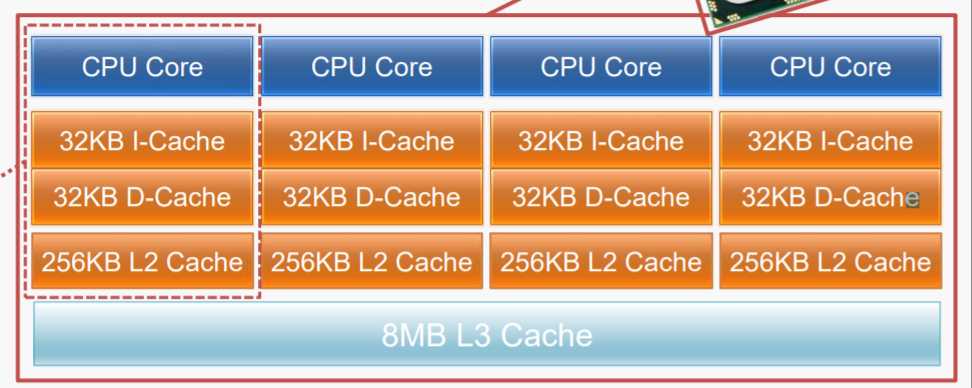

现在的多核CPU通常是在一个CPU芯片中集成了多个超标量处理器核。同时包含指令高速缓存和数据高速缓存,对应了我们原理结构当中的指令存储器和数据存储器。为了提高性能现在的处理器当中一般还配备了二级的高速缓存。 这些部件的关系非常紧密,我们通常也就把这一部分称为一个处理器核。

那么刚才看到那个四发射十六级流水线的结构图就是在只这么一个处理器核内部的结构,那么可以说这一个处理器核就是一个超标量流水线的处理器核。

参考链接:https://www.coursera.org/learn/jisuanji-zucheng/lecture/dL6g2/604-liu-shui-xian-de-mou-xian

标签:更新 取出 image ref 分享图片 应用 分解 编码 存储器

原文地址:https://www.cnblogs.com/lfri/p/10051910.html