标签:仿真 img image == inf color http code jpg

一、占空比50%的奇数分频

1、实现思路

实现奇数(N)分频,分别用上升沿计数到(N-1)/2,再计数到N-1;用下降沿计数到(N-1)/2,再计数到N-1,得到两个波形,然后把它们相或即可得到N分频。

2、代码

1 module fp_odd(clk_in,rst_n,cnt_p,cnt_n,clk_p,clk_n,clk_out); 2 parameter N=5; 3 input clk_in; 4 input rst_n; 5 output[2:0] cnt_p; 6 output[2:0] cnt_n; 7 output clk_p; 8 output clk_n; 9 output clk_out; 10 11 reg[2:0] cnt_p; 12 reg[2:0] cnt_n; 13 reg clk_p; 14 reg clk_n; 15 16 always @(posedge clk_in or negedge rst_n) 17 begin 18 if(!rst_n) cnt_p <= 0; 19 else 20 begin 21 if(cnt_p == N-1) cnt_p <= 0; 22 else cnt_p <= cnt_p + 1‘b1; 23 end 24 end 25 26 always @(posedge clk_in or negedge rst_n) 27 begin 28 if(!rst_n) clk_p <= 0; 29 else 30 begin 31 if(cnt_p == (N-1)/2) clk_p <= !clk_p; 32 else if(cnt_p == N-1) clk_p <= !clk_p; 33 else clk_p <= clk_p; 34 end 35 end 36 37 always @(negedge clk_in or negedge rst_n) 38 begin 39 if(!rst_n) cnt_n <= 0; 40 else 41 begin 42 if(cnt_n == N-1) cnt_n <= 0; 43 else cnt_n <= cnt_n + 1‘b1; 44 end 45 end 46 47 always @(negedge clk_in or negedge rst_n) 48 begin 49 if(!rst_n) clk_n <= 0; 50 else 51 begin 52 if(cnt_n == (N-1)/2) clk_n <= !clk_n; 53 else if(cnt_n == N-1) clk_n <= !clk_n; 54 else clk_n <= clk_n; 55 end 56 end 57 58 assign clk_out = clk_p | clk_n; 59 60 endmodule

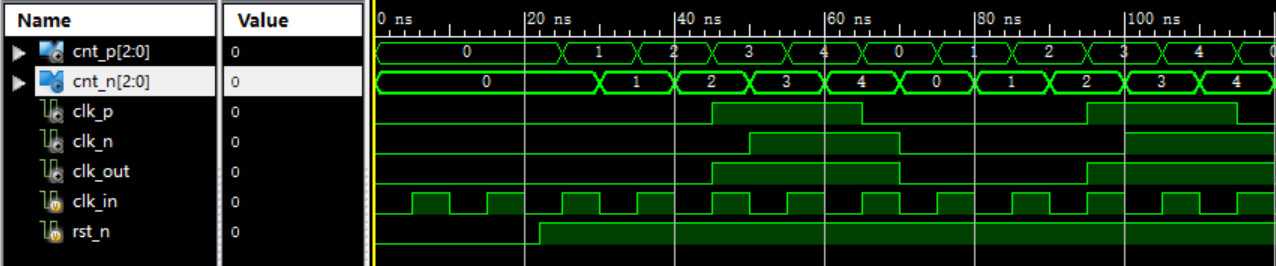

3、仿真波形

标签:仿真 img image == inf color http code jpg

原文地址:https://www.cnblogs.com/wt-seu/p/10052354.html