标签:strong 网易 span clock 物理 sig get tle bcb

本文转自:自己的微信公众号《集成电路设计及EDA教程》

《忆往昔--集成门控时钟技术的前世--分离门控时钟技术》

多种门控时钟实现方案:

Design Compiler中已经集成了可以进行低功耗设计的Power Compiler,它有多种门控时钟实现方案(分离门控时钟、集成门控时钟、多级门控时钟、层次化门控时钟)。

如何选择?

首先需要看自己所用的标准单元库中是否有集成门控时钟(Integrated Clock Gating, ICG)单元,如果有的话最好选择使用ICG而不用分离门控时钟单元,因为它性能不如ICG,且在后端实现中需要一些人为的干预(需要通过设置net weight将Latch和与非门/或非门靠近放置),较麻烦。无论是分离门控时钟单元还是ICG,他们都可以被用来实现多级以及层次化门控时钟。

如果标准单元库中没有ICG,那么我们只能采用分离门控时钟技术。

在逻辑综合阶段,我们可以通过set_clock_gating_style命令来设置选择采用哪种方案,下面将对几种方式分别做以介绍。

1. 分离门控时钟(Discrete Clock Gating)

Power Compiler在实现CG时,一般会默认采用分离门控时钟技术。

我们采用分离门控时钟技术应该只有一种情况,那就是采用的工艺比较特殊(如BiCMOS)或者工艺比较老,标准单元库中没有ICG,但是又想降低动态功耗,那只能使用分离门控时钟技术了。

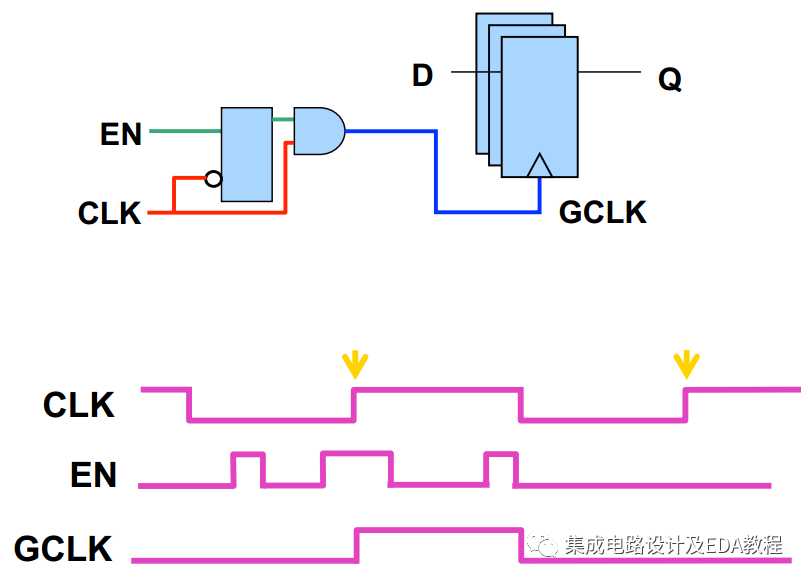

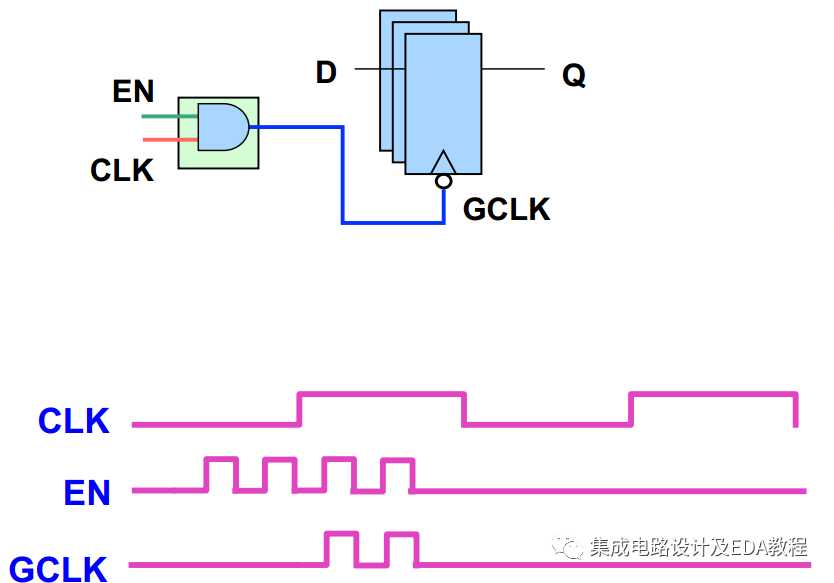

它有两种实现方式,即基于锁存器的CG和不用锁存器的CG,一般默认情况下软件会选择前者。基于锁存器的CG单元的结构及波形如图1所示,它由一个锁存器和一个与门(或者或门、与非门、或非门)构成。不用锁存器的CG单元的结构如图2所示,它由一个简单的与门(或者或门、与非门、或非门)构成。在性能上,前者与后者相比有很大的优势,这可以在它们相应的波形图中看出。因为当EN信号不稳定时,不用锁存器的CG单元会在CG单元的输出端形成毛刺,从而影响其后的寄存器组,而基于锁存器的CG单元利用锁存器来采样EN信号,达到与CLK同步的效果,所以输出结果会非常稳定。

图1 基于锁存器的CG单元的结构及波形

图2 不用锁存器的CG单元的结构及波形

分离门控时钟的逻辑综合实现:

如果要在设计中实现基于锁存器的分离门控时钟,则需要在Design(Power) Compiler进行逻辑综合前先选择门控时钟单元的类型:

采用基于锁存器的CG单元:

set_clock_gating_style -sequential_cell latch

而不用锁存器的CG的命令为:

set_clock_gating_style -sequential_cell none

同时我们还需要对CG的对象最低位宽和最大扇出进行控制(具体原因见前篇推文),因为分离门控时钟单元里面含有锁存器和与门等单元,不像集成门控时钟单元,它的时序要求信息写在了lib库里面,所以还得手动指定setup和hold。

set_clock_gating_style -sequential_cell latch \

-max_fanout 32 \

-minimum_bitwidth 4 \

-setup 3 \

-hold 0.3

老版的DC用insert_clock_gating命令插入门控时钟单元,之后用compile进行编译;

新版的DC直接用compile -gate_clcok或者compile_ultra -gate_clock直接在编译过程中就能实现,更加简单。

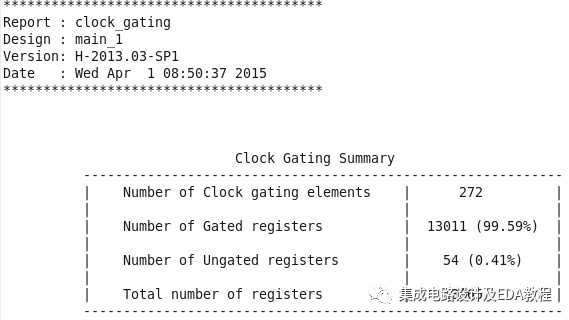

编译完成后报告实现的效果:

report_clock_gating > ./log/clock_gating.ckgt

生成的报告如图3所示:

图3 生成的门控时钟报告

分离门控时钟技术的优点:

上篇推文:

妇孺皆知的低功耗技术 | 门控时钟(Clock Gating, CG)技术

介绍过了,这里就不说了,着重说下它的缺点。

分离门控时钟技术的缺点:

一般插入分离门控时钟单元可能会引起时钟偏斜(Clock Skew)问题,进而会导致输出的时钟信号中有毛刺。

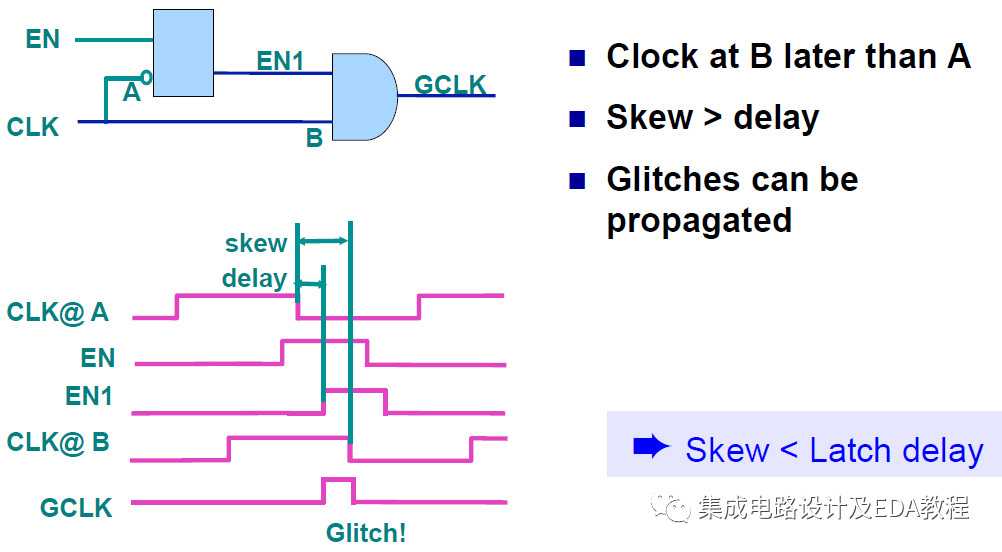

如图4所示,时钟CLK分两路:

图4 分离门控时钟的Skew问题

一路送到比较近的锁存器时钟输入端CLK@A,它去采集使能信号EN,锁存器在CLK@A为0时透明,为1时锁存。经过一个锁存器的延迟(CLK to Q latch delay)到EN1。

另一路时钟送到较远的与门一个输入端B,其时钟相比于CLK@A而言,有一段延迟,即CLK@B与CLK@A之间有Skew,Skew小于latch的delay。该Skew很可能会产生一些毛刺(毛刺的宽度大约为Skew-Delay)。

解决方法有两种:

1、采用后边将要介绍的集成门控时钟技术(ICG);

2、在布局阶段设置net weight将与门和锁存器尽量靠近放置(推文后边有介绍)。

分离门控时钟后端物理实现要点:

在后端设计中除了前面的布局布线流程之外,还要注意以下几点:

(注:由于本笔记是本科毕设阶段基于Astro工具来做的,因此下面的讲解都基于Astro工具,ICC的话应该类似。)

1.布局前的准备

在布局阶段,需要将插入的CG单元中的锁存器和与门(或者与非门)尽量靠近放置,这需要完成布局前的准备工作。

首先根据CG Cell的信息编写gatedclock.nets文件,增大锁存器和与门之间的连线的netWeight。然后在Astro中加载完.sdc时序约束文件并进行时序分析后、布局阶段前,以导入tdf文件的形式导入该gatedclock.nets文件来实现对锁存器和与门之间间距的约束,后面的布局便会自动按照此文件来将两者尽量靠近放置。

根据其中一个CG Cell的信息编写的命令如下:

netWeight "ENL" 255 255

netWeight "dan/clk_gate_dout_reg/net456"255 255

以导入tdf文件的形式导入gatedclock.nets文件后,开始布局操作后边给出Astro中的布局结果。

2.分离门控时钟单元布局结果

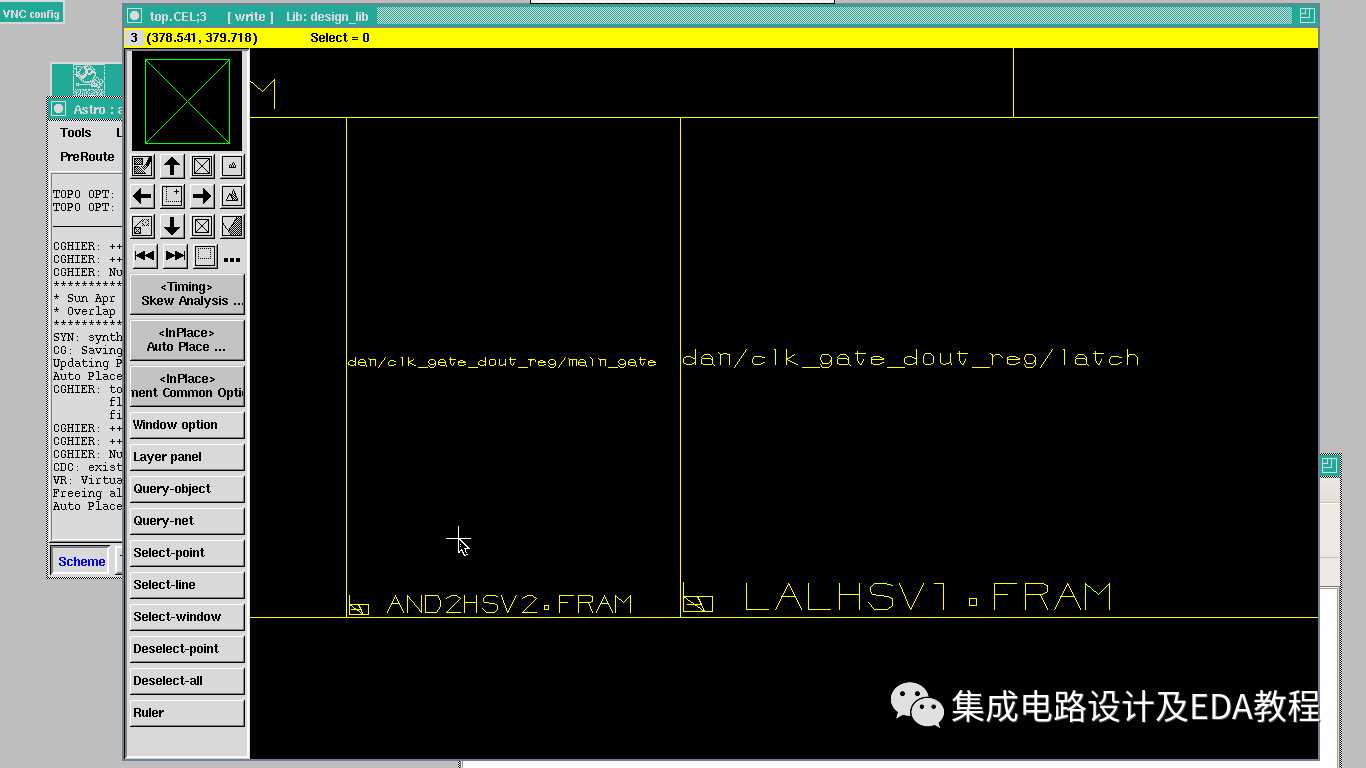

如图5所示为Astro中布局完毕后的效果。

图5 Astro中与门和锁存器靠近放置

从图中两个单元的FRAM View的位置关系可以看出,Cell名为"dan/clk_gate_dout_reg/main_gate"的AND2HSV2.FRAM的与门和名为"dan/clk_gate_dout_reg/latch"的LALHSV1.FRAM的锁存器是靠近放置的,成功达到了预期的效果。

3. 时钟树综合(CTS)之前的相关设置:

CTS之前,需要让时钟clk穿过锁存器,而不能让软件将锁存器的clk端视为一个sync pin(时序单元的时钟端口,这些Pin上的Latency工具都会自动进行Balance)。因为Astro默认会将所有时序单元(如锁存器和触发器)和宏单元的时钟端口视为sync pin,所以需要在CTS之前去除CG单元中latch时钟端的stop属性,否则时钟树综合的时候会插入倒向器和缓冲器来平衡电路中的Skew,这会严重影响门控时钟的功能,导致到达CG中与门两输入端的信号不满足建立时间或保持时间的要求,从而会导致输出端产生毛刺。

这可以用astSetClockNonSop命令来实现。现仍以前面图中显示的锁存器为例讲解其相应的设置命令:

astSetClockNonStop "dan/clk_gate_dout_reg/latch"#t

当设计中插入的CG Cell非常多时,可以将这些命令编写成一个脚本文件,然后以命令load加载进来。

4. 后续操作:

后续的操作就是常规的NDR绕时钟线和non-NDR绕普通信号线,没什么特殊的,可以参照ICC的流程。

结束语:

希望通过分离门控时钟技术大家能对CTS中门控时钟单元的stop pin和nonstop有清楚的认识。在最新的集成门控时钟实现方案中,所有这些问题都变得更加简单了,基本上不需要任何特殊的设置,EDA软件都能自动处理。在后续的推文中会介绍。

门控时钟相关推文:

妇孺皆知的低功耗技术 | 门控时钟(Clock Gating, CG)技术

Memory门控时钟低功耗 --在Floorplan和Placement阶段有何考虑?

效果贼棒 | 门控时钟低功耗--Auto Bound 与Physical Aware Clock Gating

低功耗相关推文:

轻松的低功耗策略 | Transistor Sizing with Longer Channel Length

千呼万唤始出来--QQ交流群 | 多种低功耗技术及其在IC后端布局中的应用

润物细无声--却鲜为人知的低功耗设计技术--Stack Effect

与状态相关的Leakage power(State-dependent leakage power)

网易云课堂视频课程

链接:https://study.163.com/course/introduction/1005909004.htm

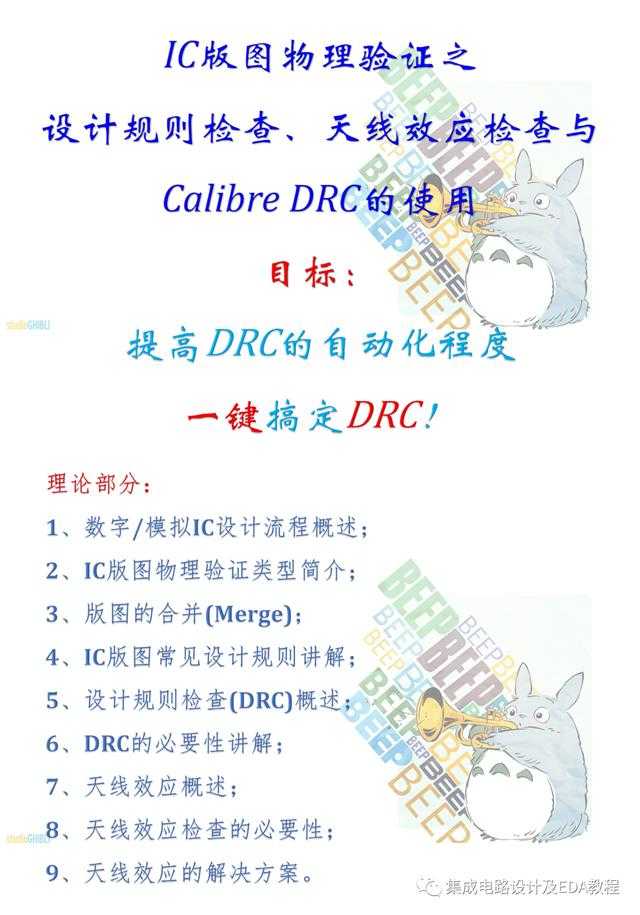

《Calibre DRC教程-一键搞定DRC》

《Calibredrv教程-提高流程自动化》

《搭建IC设计的EDA虚拟机/服务器》

标签:strong 网易 span clock 物理 sig get tle bcb

原文地址:https://www.cnblogs.com/ASIC-Horizon/p/10105470.html