标签:组合 ESS process img 采样 lock com 功能设计 数字电路

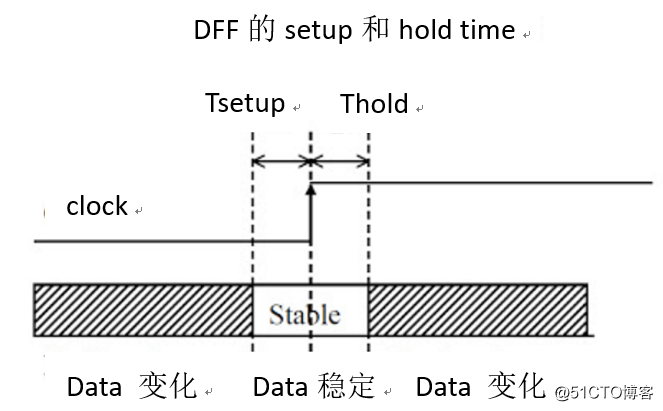

1、 什么是建立时间、保持时间,如果setup time violation或者hold time violation 应该怎么做?(10分)

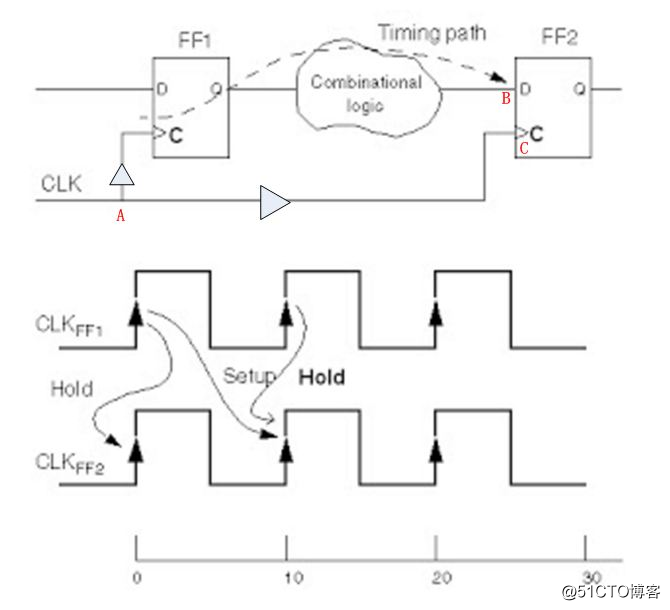

Timing path 时序路径分析方法:

分析时序路径时常见的变量:

Tclk = 时钟周期,是可变的,比如1KHz ~ 5.0GHz

Tcq = 触发器的时钟端C到输出端Q的延时,是器件属性,是固定不变的

Tcomb = 两个触发器之间组合电路的延时,是可变的,可以通过设计进行优化逻辑

Tsetup = 建立时间是触发器的固有属性,是定值

Thold = 保持时间是触发器的固有属性,是定值

Tskew = 相邻两个触发器之间的时钟的偏移,是可变的

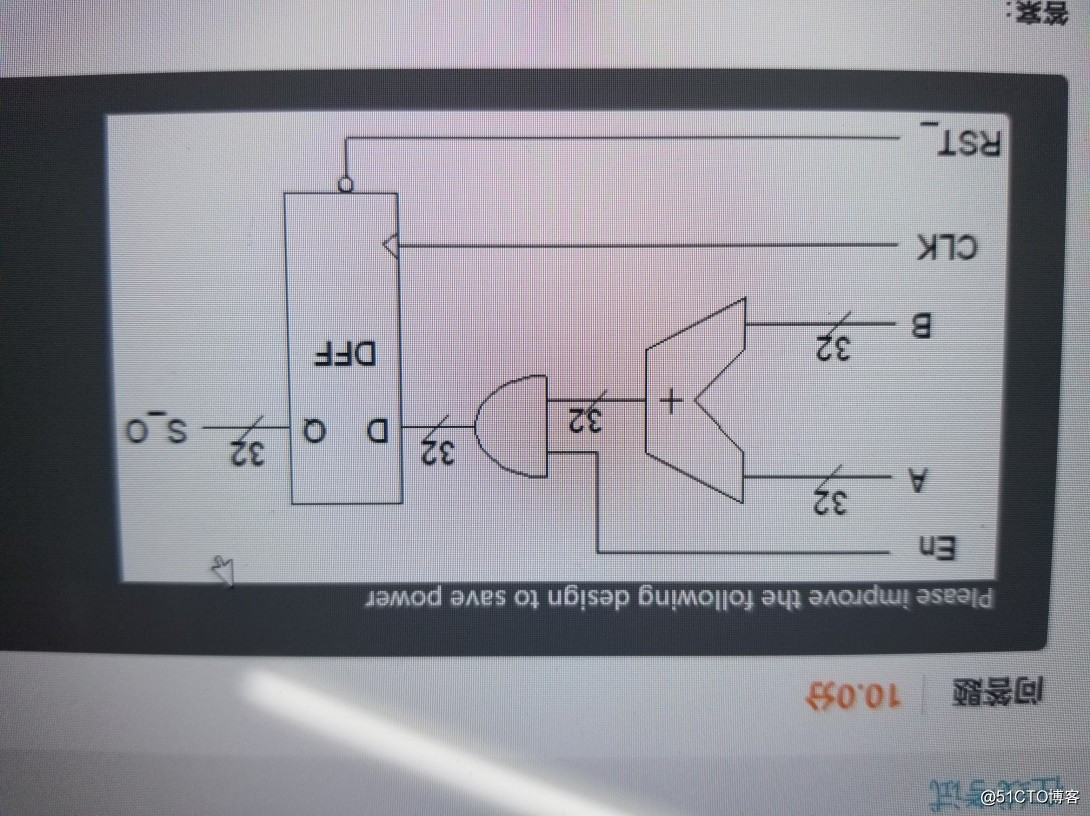

图二 setup和hold timing path的分析

Setup time violation:

建立时间在静态时序分析时必须满足以下条件:

Tclk > Tcq + Tcomb + Tsetup - Tskew

如果setup time violation, 则上述公式不成立。

Setup time violation solution:调整上述公式中的变量:Tclk, Tcomb,Tskew

? 增大Tclk

? 就是降低数字系统的工作频率 (很多产品分等级,是根据频率来分的;品质好的芯片,频率高,价格贵;品质差的芯片,降频,贱卖)

? 减少Tcomb:

? 从数字电路逻辑功能设计的角度看

? 在组合电路之间插入寄存器,增加流水线(pipeline);

? 在不改变逻辑功能的前提下,对组合逻辑电路进行优化;

? 减少扇出或者负载;

? 从数字物理版图实现的角度看

? 更换速度更快的标准单元(HVT – High Voltage Threshold, SVT – Standard Voltage Threshold, LVT- Low Voltage Threshold)

? 更换驱动能力更强的标准单元(X2, X4)

? 跟换阻值更低的金属层以减少标准单元电路的负载和金属线网的延迟

? 增加Tskew

? 在时钟路径上,插入buffer,增加时钟路径的延迟,但是不能影响hold timing。

Hold time violation:

保持时间在静态时序分析时必须满足以下条件:

Thold < Tcq + Tcomb - Tskew

如果hold time violation, 则上述公式不成立。

Hold time violation solution:

? 增大Tcomb

? 在组合电路的数据传输路径上,插入延迟单元(buffer),增加组合逻辑延迟;但是当组合逻辑延时增加时,setup time可能会出现违例。这时候就需要做平衡(balance)。由此可以看出setup和hold time是相互制约的。

? 减小Tskew

? 时钟树调整,做好clock tree balance,hold就容易收敛。因为hold time与时钟周期没有关系。

总结:setup和hold是相互制约的。修复hold之后,setup的裕量就会变小或者变成负值。因此时钟频率越高,setup和hold相互制约越严重,甚至会出现修复setup之后,hold就会违例,或者修复hold之后,setup就会违例的现象。

思考题1:为什么触发器会存在setup和hold time的要求?

提示:研究触发器的结构。数字电路基本结构。

思考题2:当setup和hold time violation发生时,会导致什么后果?

提示:亚稳态

思考题3: 什么是亚稳态?如何在异步电路设计中解决亚稳态的问题?

提示:跨时钟域时,一个信号如何处理,多根信号如何处理,大量数据传输如何处理等常见的异步电路设计方法

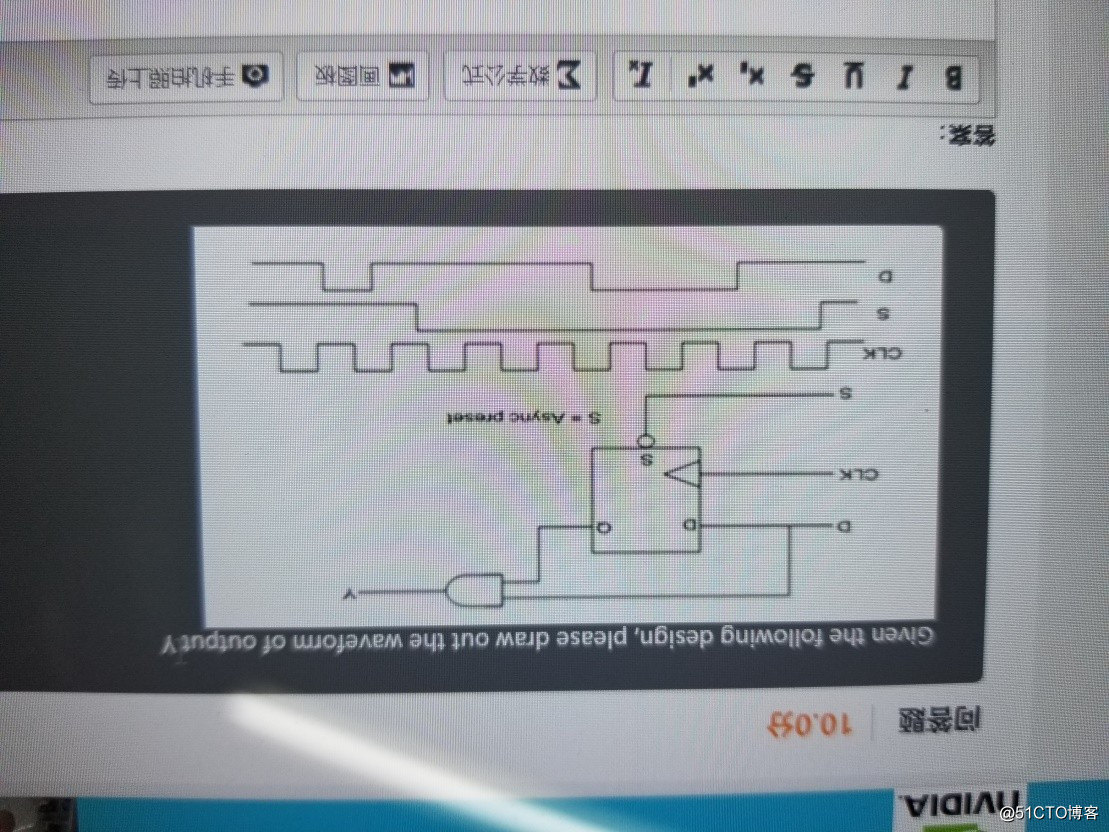

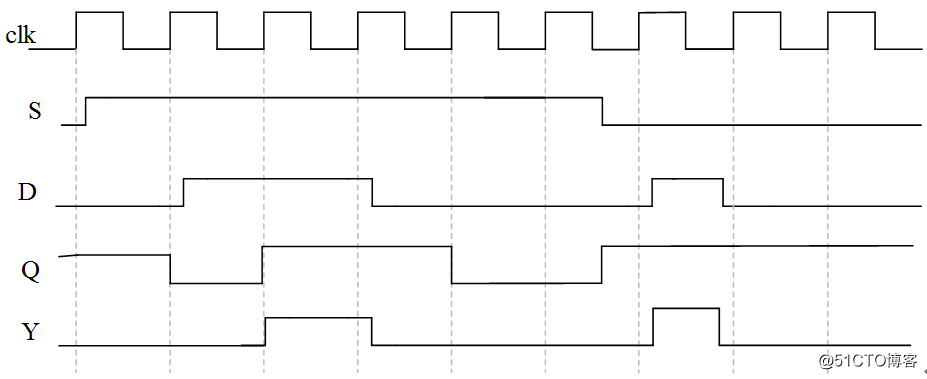

2、

答案:

题目分析:这道题目主要考察的是带有异步置位的触发器和逻辑与的布尔逻辑,然后通过绘制时序波形图的方式显示布尔逻辑。

思考题:如果把异步置位的触发器,替换成异步复位的触发器后,时序图应该是怎样的?

3、

答案:

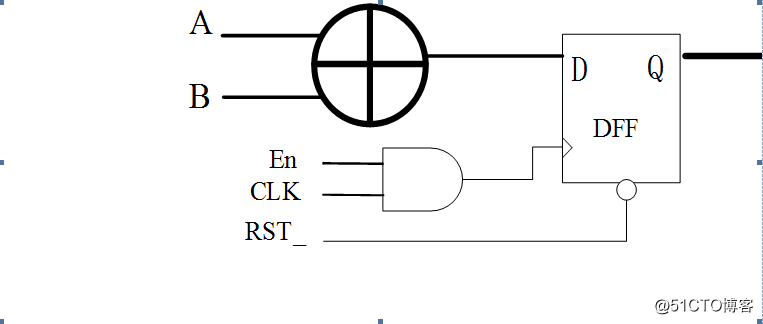

题目分析:这道题目,主要考察数字电路中的低功耗设计中的clock gating。

思考题:save power的时候,需要关注那些power消耗:动态功耗、静态功耗等,降低功耗的常见方法有哪些?

IC攻城狮求职宝典 01 2018年IC设计企业 笔试题 01 英伟达(Nvidia)

标签:组合 ESS process img 采样 lock com 功能设计 数字电路

原文地址:http://blog.51cto.com/14075497/2333276