标签:设计 接收 延迟 准备 示意图 执行 电话 还原 字节

一、声音的基本概念

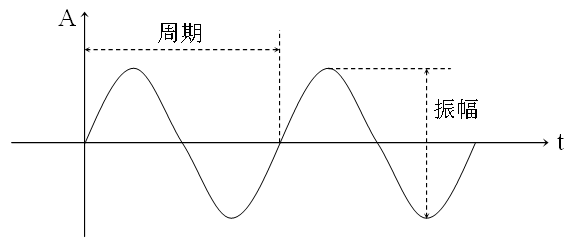

声音是通过一定介质传播的连续的波。

重要指标:

声音按频率分类:

声音的传播携带了信息,它是人类传播信息的一种主要媒体。 声音的三种类型:

|

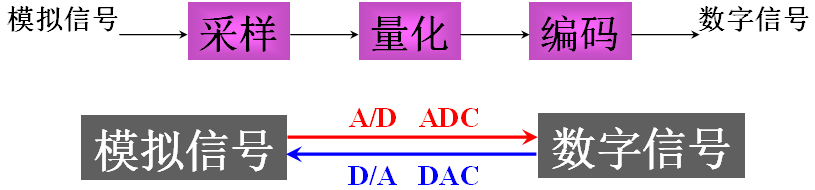

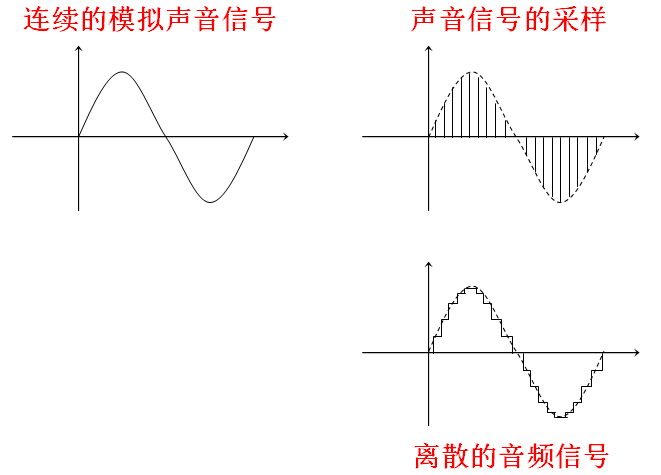

采样频率 |

量化位数 |

声道数 |

|

每秒钟抽取声波幅度样本的次数 |

每个采样点用多少二进制位表示数据范围 |

使用声音通道的个数 |

|

采样频率越高 声音质量越好 数据量也越大 |

量化位数越多 音质越好 数据量也越大 |

立体声比单声道的表现力丰富,但数据量翻倍 |

|

11.025kHz 22.05 kHz 44.1 kHz |

8位=256 16位=65536 |

单声道 立体声 |

音频数据量=采样频率×量化位数×声道数/8(字节/秒)

|

采样频率 (kHz) |

量化位数 (bit) |

数据量(KB/s) |

|

|

单声道 |

立体声 |

||

|

11.025 |

8 |

10.77 |

21.35 |

|

16 |

21.53 |

43.07 |

|

|

22.05 |

8 |

21.53 |

43.07 |

|

16 |

43.07 |

86.13 |

|

|

44.1 |

8 |

43.07 |

86.13 |

|

16 |

86.13 |

172.27 |

|

WAV是Microsoft/IBM共同开发的PC波形文件。因未经压缩,文件数据量很大。

特点:声音层次丰富,还原音质好

MP3(MPEG Audio layer3)是一种按MPEG标准的音频压缩技术制作的音频文件。

特点:高压缩比(11:1),优美音质

WMA(Windows Media Audio)是Windows Media格式中的一个子集(音频格式)。

特点:压缩到MP3一半

MIDI(乐器数字接口)是由一组声音或乐器符号的集合。

特点:数据量很小,缺乏重现自然音

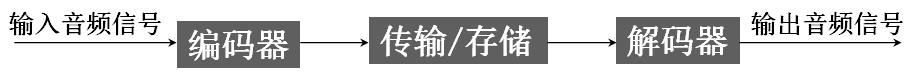

压缩编码技术是指用某种方法使数字化信息的编码率降低的技术

①声音信号中存在大量的冗余度;

②人的听觉具有强音能抑制同时存在的弱音现象。

①无损压缩(熵编码)

霍夫曼编码、算术编码、行程编码

②有损压缩

波形编码--PCM、DPCM、ADPCM 、子带编码、矢量量化

参数编码--LPC

混合编码--MPLPC、CELP

|

分类 |

标准 |

说明 |

|

电话语 音质量 |

G.711 |

采样8kHz,量化8bit,码率64kbps |

|

G.721 |

采用ADPCM编码,码率32kbps |

|

|

G.723 |

采用ADPCM有损压缩,码率24kbps |

|

|

G.728 |

采用LD-CELP压缩技术,码率16kbps |

|

|

调幅广 播质量 |

G.722 |

采样16kHz,量化14bit,码率224(64)kbps |

|

高保真 立体声 |

MPEG 音频 |

采样44.1kHz,量化16bit,码率705kbps (MPEG三个压缩层次,384-64kbps) |

声卡是负责录音、播音和声音合成的一种多媒体板卡。其功能包括:

①录制、编辑和回放数字音频文件

②控制和混合各声源的音量

③记录和回放时进行压缩和解压缩

④语音合成技术(朗读文本)

⑤具有MIDI接口(乐器数字接口)

输出电压:

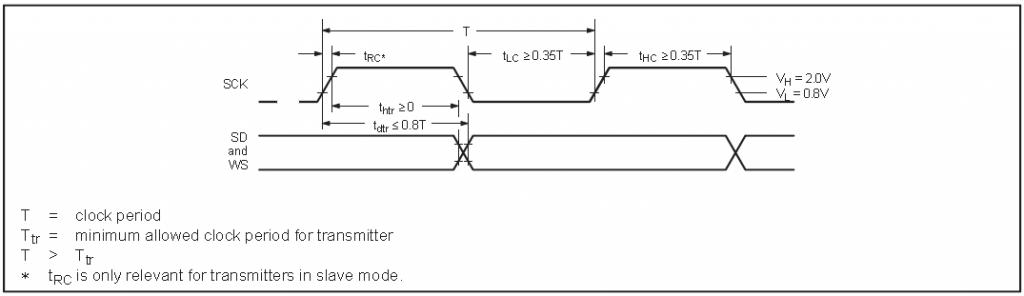

VL <0.4V输入电压

VIL=0.8V

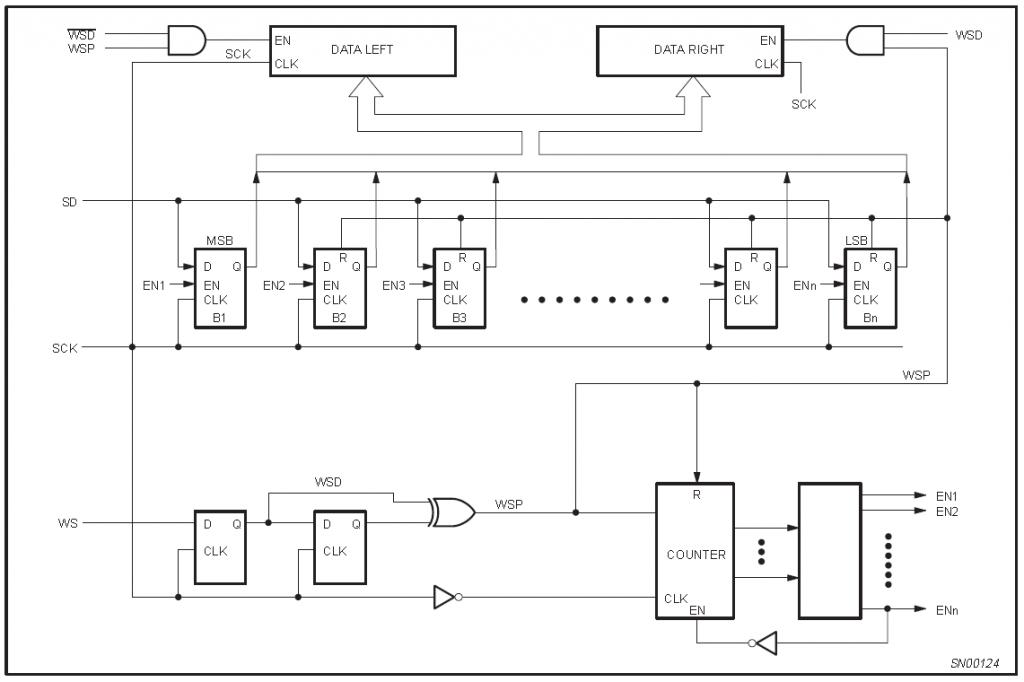

I2S相关的寄存器包括I2S控制寄存器I2SCON、I2S模式寄存器I2SMOD、I2S分频寄存器I2SPSR、I2SFCON寄存器和FIFO寄存器。

1)I2SCON控制寄存器

I2SCON控制寄存器物理地址为0x55000000,可读/写,复位后值为0x100。寄存器各个比特位意义如下:

[8] 左右声道标记,0=左声道,1=右声道;

[7] 发送FIFO就绪标记,取0时表示没有就绪,取1时表示FIFO就绪;

[6] 接收FIFO就绪标记,取0时表示没有就绪,取1时表示FIFO就绪;

[5] 发送DMA请求使能,取0时请求禁止,取1时请求使能;

[4] 接收DMA请求使能,取0时请求禁止,取1时请求使能;

[3] 发送通道空闲命令,在空闲状态(暂停传输)时,I2SLRCK是不激活的,0表示I2SLRCK产生,1表示不产生;

[2] 接收通道空闲命令,在空闲状态(暂停传输)时,I2SLRCK是不激活的,0表示I2SLRCK产生,1表示不产生;

[1] I2S预分频器使能,取0时预分频器禁止,取1时预分频器使能;

[0] I2S接口使能,取0时I2S禁止,取1时I2S使能。

标签:设计 接收 延迟 准备 示意图 执行 电话 还原 字节

原文地址:https://www.cnblogs.com/tianqiang/p/10187170.html