标签:9.png 也会 ima image http 组件 情况 匹配 这一

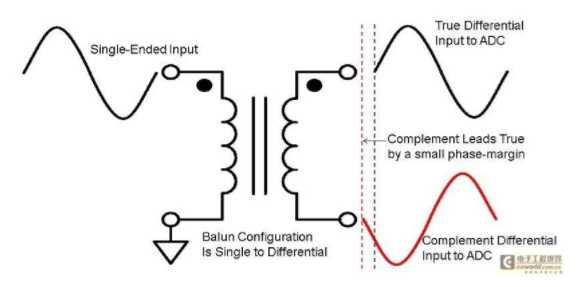

大多数高速ADC使用差分输入结构。 这样会具有良好的共模噪声抑制,但是常常需要在ADC输入端将单端信号转换为差分信号。 这一转换过程,主要选择无源巴伦或变压器及有源放大器来实现。

虽然有很多高性能的组件可用于系统的这一部分,但是即使最佳解决方案也会带来小的差分不平衡,使得信号失真并降低ADC的无杂散动态范围(SFDR)。

ADC前端的差分输入信号各端之间的相位失配会导致基波信号谐波功率增加。 当差分信号的一端在时间上先于另一端且提前量达到相对于其周期的一定相位量时,就可能发生这种情况。 其效应如下图所示,此时,差分对的一端比另一端提前较小的周期相位量。

这种情况下,巴伦输出与ADC差分输入之间存在几度的相位失配。 如果差分输入在相位上完全匹配,这可能导致第二谐波比其他情况下高,从而对SFDR造成影响。

差分信号采集系统前端的另一不平衡可能是幅度失配。 当差分信号一端的增益不同于其补码时,ADC输入就会把一端视为较大信号,另一端视为较小信号。 在其他情况下,这会减小基波信号的全功率,降低SFDR的dBc值。 差分输入端如果存在2 dB的幅度失配,结果会导致满量程输入信号功率下降1 dB。 这些前端信号的每个完整性方面问题都可能使ADC的SFDR性能以及整个系统的信号解码能力下降。

对于设计良好的单芯片ADC内核,SFDR一般主要由载波频率与目标基波频率的第二或第三谐波之间的动态范围构成。 具有高相位或幅值失配的巴伦可放大高性能ADC的FFT中的谐波。

标签:9.png 也会 ima image http 组件 情况 匹配 这一

原文地址:https://www.cnblogs.com/dzcql/p/10325370.html