标签:部分 block 结束 ima 相关 gravity 时钟频率 执行 就会

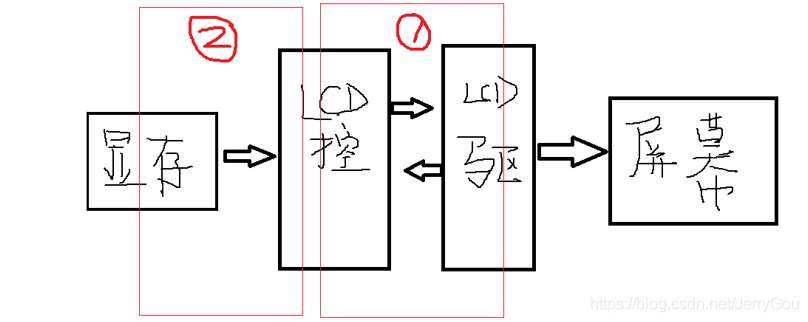

S5PV210处理器中自带LCD控制器,控制LCD的显示,把 LCD 图像数据从一个位于系统内存的 video buffer 传送到一个外部的 LCD 驱动器接口。

LCD驱动接口支持 3 种接口:

SoC如何控制LCD显示原理:

LCD驱动器:LCD驱动器一般与LCD面板集成在一起,面板需要一定的模拟电信号来控制液晶分子,LCD驱动器芯片负责给面板提供控制液晶分子的模拟电信号,驱动器的控制信号(数字信号)来自于LCD控制器的提供的接口。

LCD控制器:LCD控制器集成在SoC内部,它负责通过数字接口向外部的LCD驱动器提供要显示的像素数字信号。它必须按照一定的时序和LCD驱动器通信,LCD控制器受SoC控制,SoC会从内存中拿出像素数据给LCD控制器并最终传给LCD驱动器。

显存:SoC在内存中选一段内存,用来存放颜色数据,然后通过配置将LCD控制器和这一段内存连接起来,构成一个映射关系,一旦这个关系建立以后,LCD控制器就会自动从显存中读取像素数据传给LCD驱动器,LCD驱动器会自动的控制每个像素点的液晶分子,以形成最终的图像,建立这个映射以后就不需要SoC在来参与任何行为了。

总结一下:SoC控制LCD液晶显示的过程分为两个部分:

(1) SoC的LCD控制器引出一定的引脚与LCD驱动器连接,按照标准设置一定的时序;

(2) 把LCD要显示的像素信息放入内存中,在通过设置LCD控制器中的寄存器,与LCD控制器建立映射;之后过程就是LCD控制器芯片与驱动器芯片自动完成的事情了,整个LCD图像的显示过程就是这样。

S5PV210 的 LCD 控制器支持多种颜色格式,例如

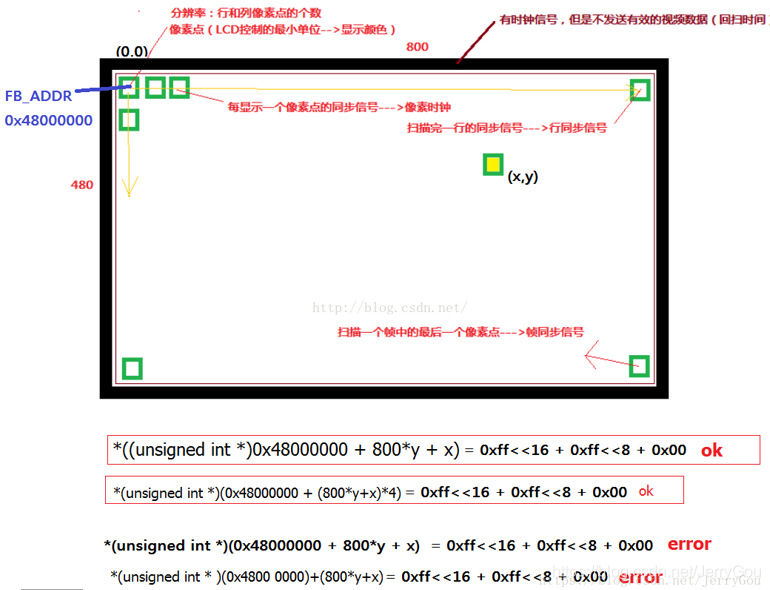

1:显示屏跟内存的关系。

我们都买过显卡,知道买独立显卡的好,那么为什么独显好?

独显跟集显的区别又在哪里?

独显的特点:有独立内存

集显的特点:跟主板共用内存

2:屏幕为什么能显示?(集显)

A DMA完成显示数据的传输,不需要CPU执行COPY函数

B LCD控制器向显示屏提供时序信号、视频数据、.....

如果需要显示一满屏的数据,则数据的大小:80048024bits

帧同步信号:液晶屏的刷新频率、垂直同步信号的频率、场频率

帧同步信号= 50Hz~70Hz,典型值:60Hz

行同步信号的频率:一帧中有多少行?

行同步信号的频率 = ( 480 +回扫的行数(45) )* 帧同步信号的频率

像素时钟频率 = (800+一行中回扫的像素点(256))*行同步信号的频率

注意:

计算:

在800*480的LCD中,VCLK的频率值:

VCLK = (800+256)(480+45) 60Hz = 33.264MHz

分辨率

行和列像素点的个数

尺寸

有效的显示区对角线的长度,单位英寸。

色位

一个像素点用多少位数据来描述----24bits

响应时间

刷新时间---->60Hz(16ms)

响应时间---->几ms

亮度????????cd/m**2

高亮屏:600

一般屏:250

对比度????

白色的亮度/黑色的亮度。

?

寿命????????

单位:小时 ?? 5万小时

当液晶屏的亮度降低到出厂亮度的一半的时候,认为寿命到了。

?

可视角度

四个方向的可视角度是不对称的,一般有一个方向是比较差的

看一下核心板原理图:LCD接线为24条VD数据输出线,用来传输RGB888 24位颜色数据,VCLK时钟线,HSYNC:水平同步信号线;VSYNC:垂直同步信号线,VDEN:数据使能线;

RGB接口信号:

LCD_HSYNC:

行同步信号,表示一行数据的开始,LCD控制器在整个水平线(整行)数据移入LCD驱动器后,

插入一个LCD_HSYNC信号;

LCD_VSYNC:

帧同步信号,表示一帧数据的开始,LCD控制器在一个完整帧显示完成后立即插入一个LCD_VSYNC信号,

开始新一帧的显示;VSYNC信号出现的频率表示一秒钟内能显示多少帧图像,称为“显示器的频率”

LCD_VCLK:

像素时钟信号,表示正在传输一个像素的数据;

LCD_VDEN: 数据使能信号;

LCD_VD[23:0]: LCD像素数据输出端口

0xffff

1-11位是功能 剩下的每八位 分别是蓝绿红

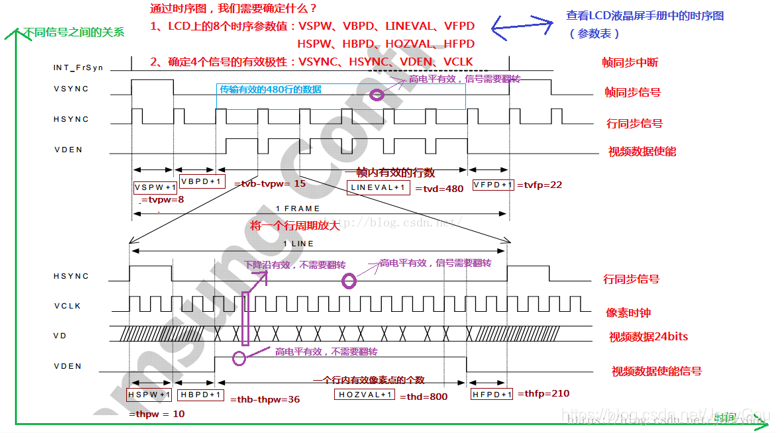

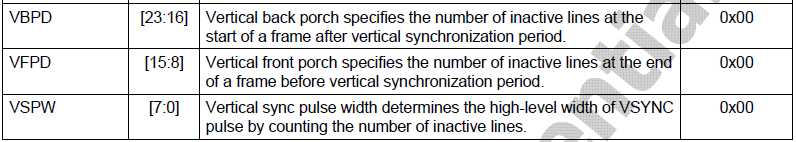

1)VSYNC信号有效时,表示一帧数据的开始, 信号宽度为 (VSPW + 1)个HSYNC信号周期,即(VSPW + 1)个无效行;

2)VSYNC信号脉冲之后,总共还要经过(VBPD + 1)个HSYNC信号周期,有效的行数据才出现; 所以,在VSYNC信号有效之后,还要经过(VSPW + 1 + VBPD + 1)个无效的行;

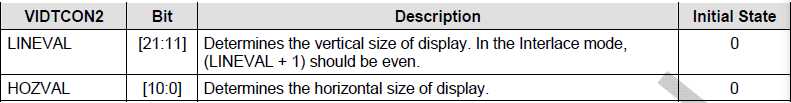

3)随即发出(LINEVAL + 1)行的有效数据;

4)最后是(VFPD + 1)个无效的行;

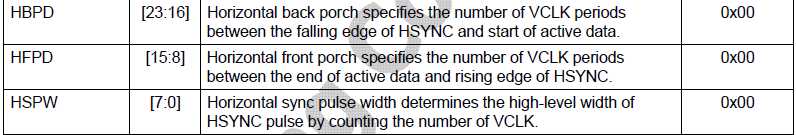

1)HSYNC信号有效时,表示一行数据的开始,信号宽度为(HSPW + 1)个VCLK信号周期,即(HSPW + 1)个无效像素;

2)HSYNC信号脉冲之后,还要经过(HBPD + 1)个VCLK信号周期,有效的像素数据才出现;

3)随后发出(HOZVAL + 1)个像素的有效数据;?????????

4)最后是(HFPD + 1)个无效的像素;

并将帧内存的地址告诉LCD控制器,它即可自动地发起DMA传输从帧内存中得到图像数据,最终在上述信号的控制下出现在数据总线VD[23:0]上。用户只需要把要显示的图像数据写入帧内存中。

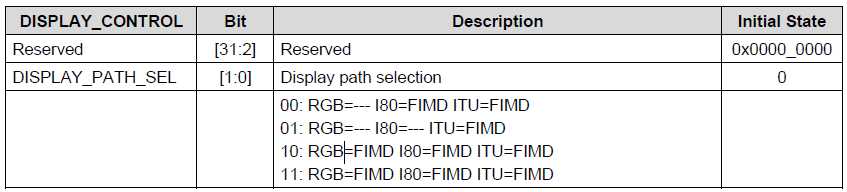

寄存器:DISPLAY_CONTROL 设置为10或11;RGB模式可行即可;

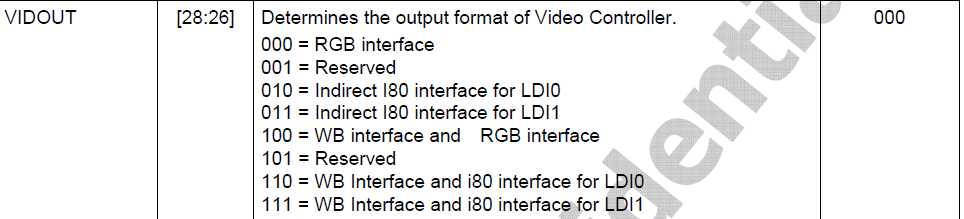

VIDCON0:Video Main Control 0 Register

bit28-26视频输出格式,设为RGB模式

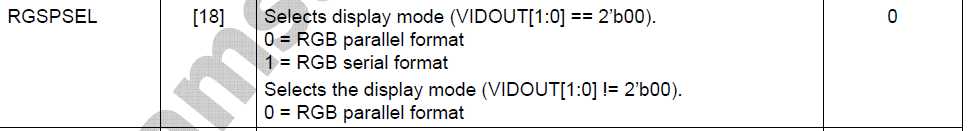

bit18:设置RGB数据传输方式为并行还是串行,因为有24根数据线所以为并行;

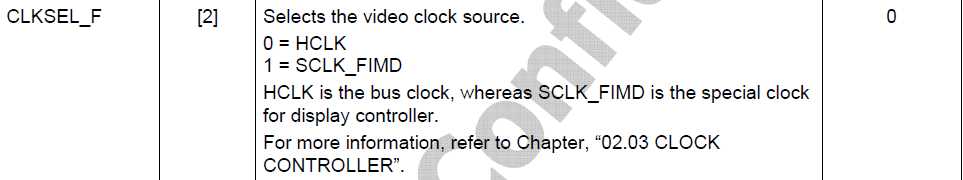

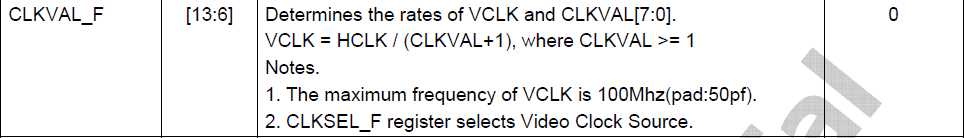

bit2选择时钟源,选HCLK 连的是HCLC_DSYS 为166MHz

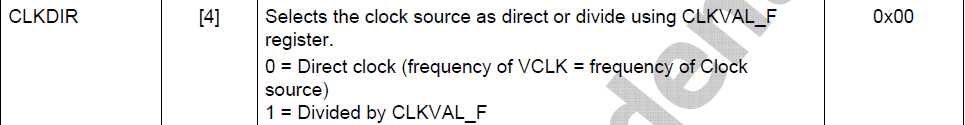

bit4:开启分频;

bit13-6设置时钟大小,时钟频率要小于控制器的最大时钟,也要小于LCD驱动器的最大时钟。

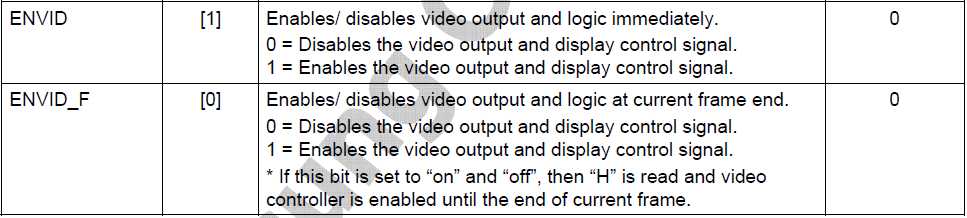

bit0 bit1为使能控制信号都使能

VIDCON1寄存器 Video Main Control 1 Register

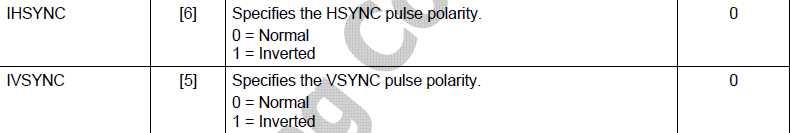

bit5 bit6设置HSYNC和VSYNC的极性,如果LCD的高低电平脉冲是相同的话,则Normal,如果极性相反则Invert。

VIDTCON0:设置时序,根据LCD数据手册中的时序来设置,结合“LCD控制器的输出时序”

VIDTCON1

VIDTCON2

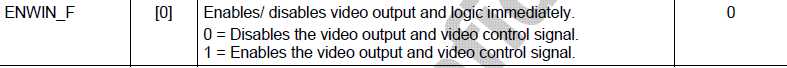

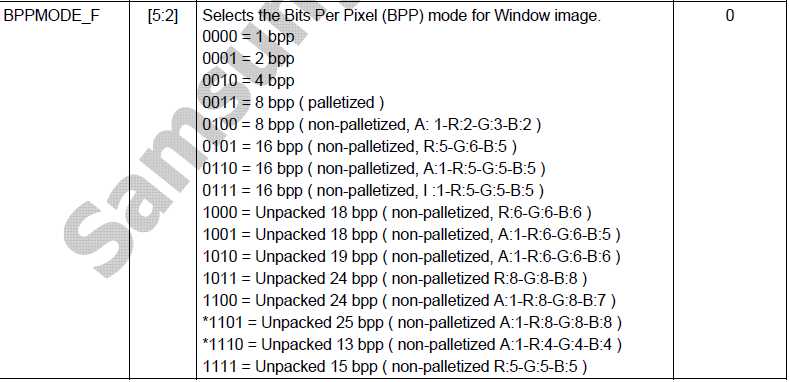

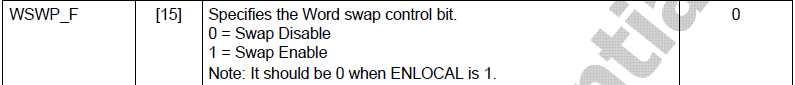

WINCON0寄存器

bit1:使能window0

bit5-2选择RGB888模式 1011

bit15:设置输出顺序为 red green blue还是 blue green red 设置为1:BGR 设置为0:RGB

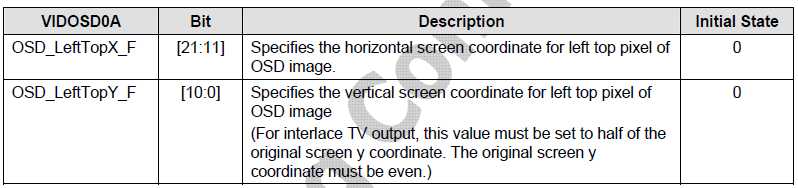

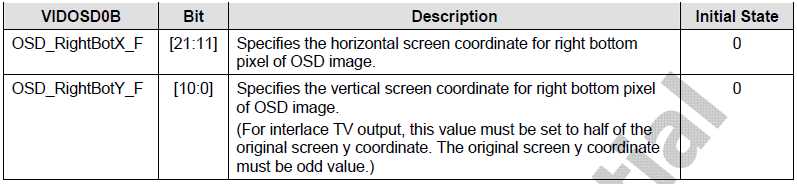

VIDOSD0A VIDOSD0B这两个寄存器是用来设置内存中window0大小;

比如设置为LCD屏幕的尺寸(即左上坐标为(0, 0) 右下坐标为(799, 479))

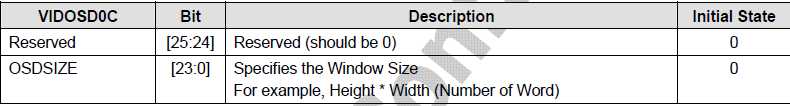

VIDOSD0C也是设置内存中window0的大小

比如设置为LCD屏幕的尺寸=800*480

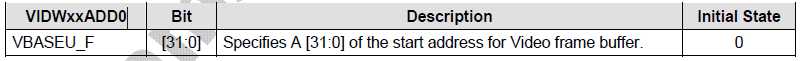

VIDW0xADD0Bx设置内存中window0的起始地址的

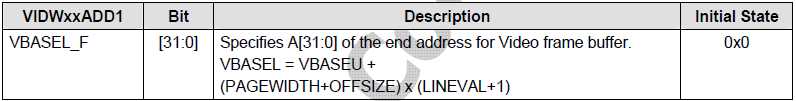

VIDW0xADD1Bx设置内存中window0的结束地址的

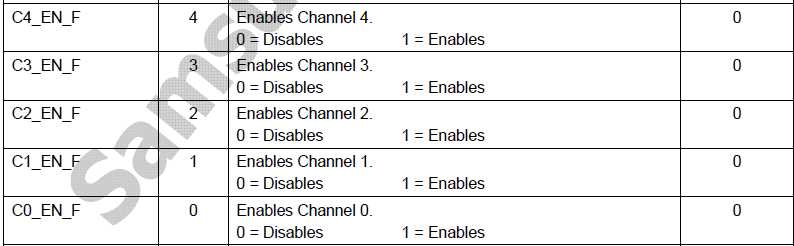

SHODOWCON寄存器来设置虚拟windows显示的;

以下位可以分别设置哪个windows显示;

补充:看核心板、地板原理图相应引脚要设置为LCD的引脚模式,LCD背光要打开;

标签:部分 block 结束 ima 相关 gravity 时钟频率 执行 就会

原文地址:https://www.cnblogs.com/linhaostudy/p/10467249.html