标签:总线 基础 直接 http 两种 lock div mis --

SPI(Serial Peripheral Interface--串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。SPI总线可直接与各个厂家生产的多种标准外围器件相连,包括FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI接口是在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,低位在后,为全双工通信,数据传输速度总体来说比I2C总线要快,速度可达到几Mbps。

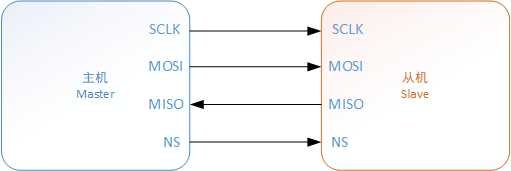

1.接口信号

该接口一般使用4条线:串行时钟线(SCLK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线NS。

图1:主从机结构

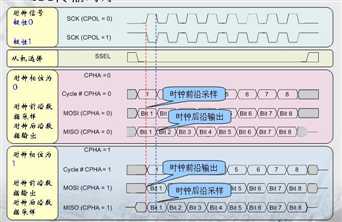

2.工作模式

SPI在SCLK控制下通过移位寄存器,每个sclk时钟周期传输1bit的数据,其具体数据传输模式可查看SPI总线协议及SPI时序图详解这篇文章。

有四种工作模式,各个工作模式的不同在于SCLK不同, 具体工作由时钟极性CPOL(Clock Polarity),时钟相位CPHA(Clock Phase)决定

CPOL:决定时钟空闲时的电平为高或低;

1 = 时钟低电平时有效,空闲时为高

0 = 时钟高电平时有效,空闲时为低

CPHA:定义SPI数据传输的两种基本模式

0=时钟周期的上升沿采集数据,时钟周期的下降沿输出数据;

标签:总线 基础 直接 http 两种 lock div mis --

原文地址:https://www.cnblogs.com/yongleili717/p/10528908.html