标签:sig 选择器 配置 验证 模式 load style strong dram

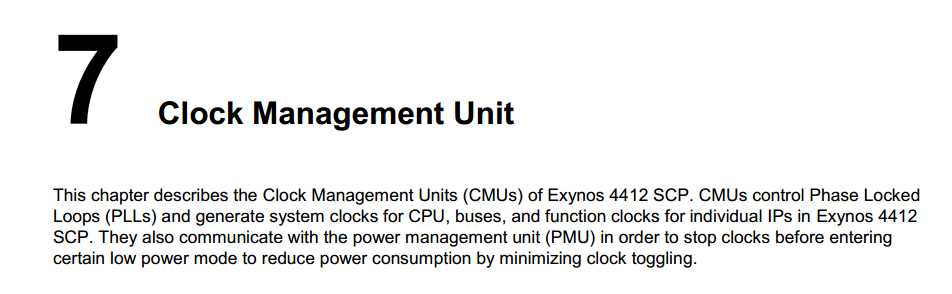

本章描述了Exynos 4412 SCP的时钟管理单元(CMUs)。在Exynos 4412 SCP中,CMUs控制相位锁相环(PLLs),并为CPU、总线和单个ip的功能时钟生成系统时钟。它们还与电源管理单元(PMU)通信,以便在进入某些低功耗模式之前停止时钟,从而通过最小化时钟切换来降低功耗。

7.1时钟域

在Exynos 4412 SCP中,它将函数块彼此异步计时,以提供更广泛的操作频率选择。它还简化了物理实现。

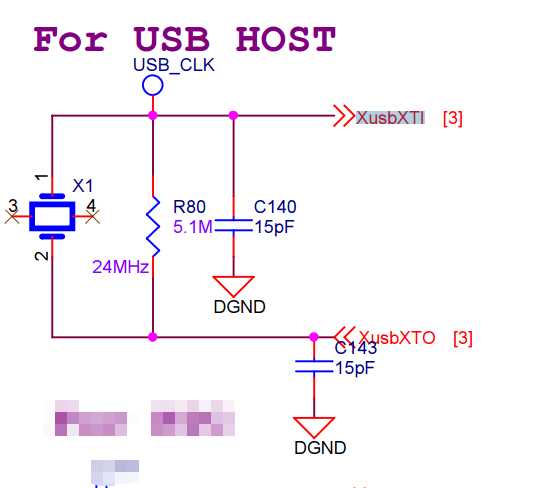

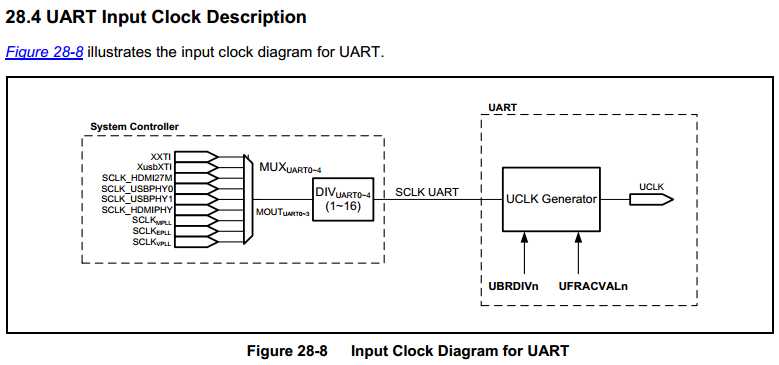

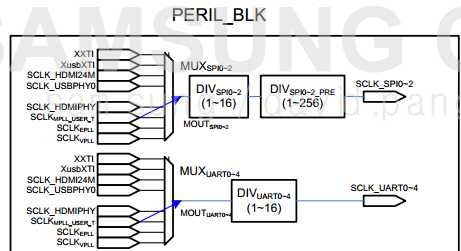

做串口的时候所用时钟 ,时钟源还为外围总线提供时钟源

,时钟源还为外围总线提供时钟源

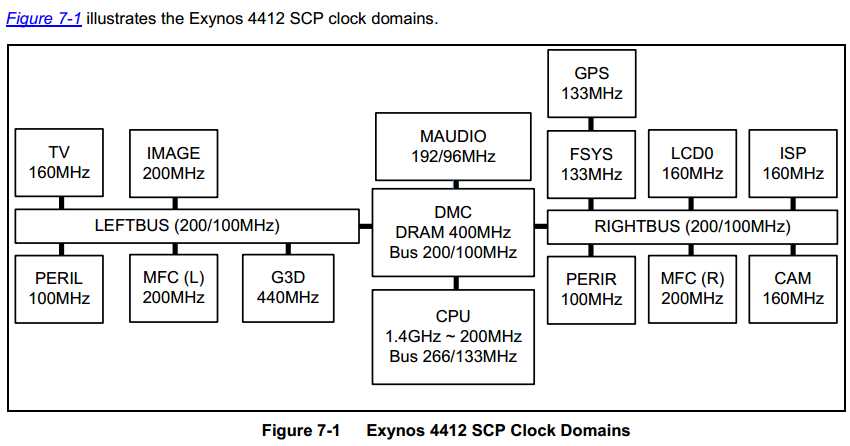

硬件来说,一共有三种:锁相环、选择器、分频器。

PLL结尾的:锁相 环,用于倍频

DIV:分频器

例如:

核心板中可以找到相应引脚:

APLL_CON0中:

| MDIV | [25:16] | RWX | PLL M Divide Value | 0xC8 |

| PDIV | [13:8] | RWX | PLL P Divide Value | 0x6 |

| SDIV | [2:0] | RWX | PLL S Divide Value | 0x1 |

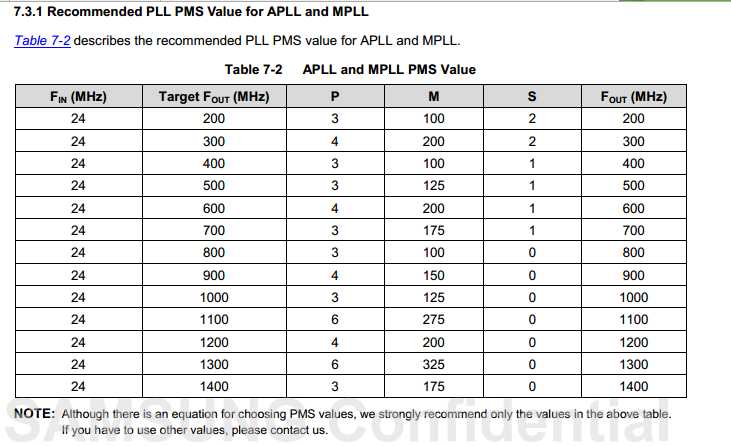

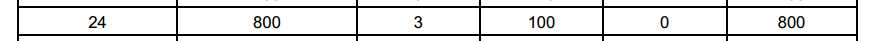

锁相环与时钟管理相关配置表:

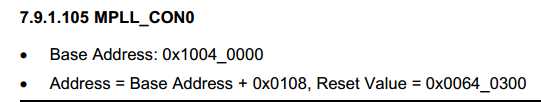

以串口时钟为例分析:

回到第七章去找

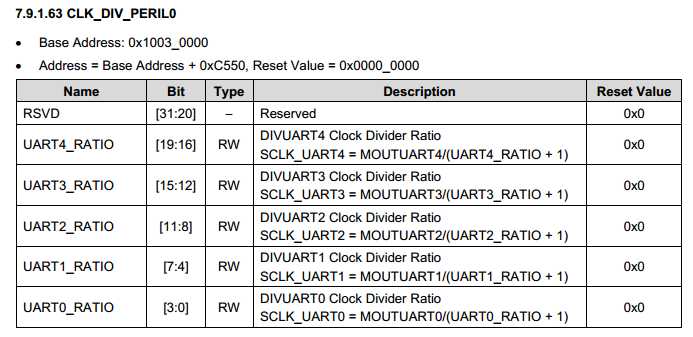

我想从后往前找,看它的分频因子是多少,

试着搜索 divuart0后:

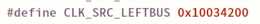

开始验证:

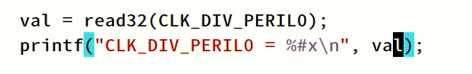

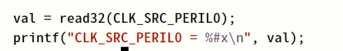

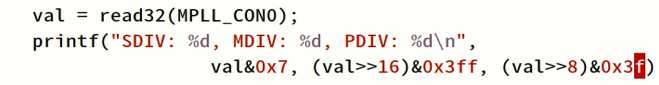

打印:

结果:

低四位 = 7

MOUTUART0 / (UART0_RATIO + 1) = MOUTUART0 / (7 + 1)

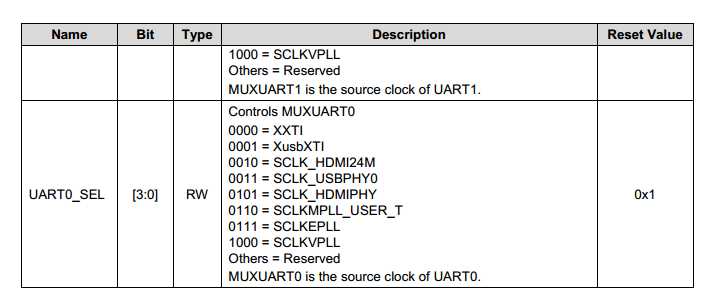

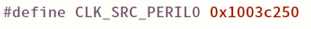

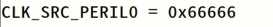

MOUTUART0取决于 八位选择器的输出 ,存在于与这个寄存器相关的某一个区域:搜索MUXUART0

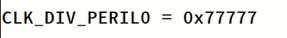

结果:

我们打印这个寄存器的值:

结果:

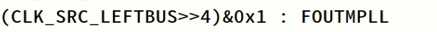

选择的时钟源即为:SCLKMPULL_USER_T

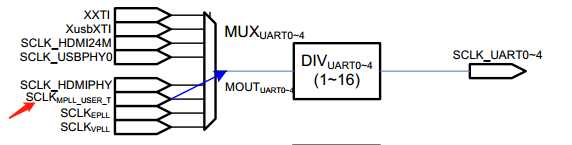

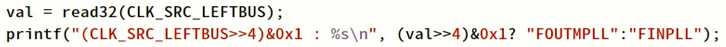

打印第四位,查看结果:

结果:

下面打印一下

结果:

找完一圈,找到了

即,800 / 8 = 100 MHz

至此,分析出了UART的时钟源为100MHz

注意:以上是在bootloader层面去验证,如果从事bootloader的设计的话,要自己设置这些寄存器得到想要的时钟频率。

标签:sig 选择器 配置 验证 模式 load style strong dram

原文地址:https://www.cnblogs.com/jason-linux/p/10530266.html