Mif 文件的数据是通过 mif_maker2010 这个软件生成的,它的使用教程通过这个链接可以找到:https://www.cnblogs.com/qidaiymm/p/6007704.html

module sw_control(

clk,

rst_n,

data_out,

sw

);

input clk;

input rst_n;

input[1:0] sw;

output[7:0] data_out; //数据输出

reg[7:0] address;

wire[7:0] q1,q2,q3; //地址寄存器

reg[7:0] data_out;

always@(posedge clk or negedge rst_n)

if(!rst_n)

address <= 8‘d0;

else if(address==255)

address <=8‘d0;

else

address <= address +1‘b1;

san_jiao_xing san_jiao_xing(

.address(address),

.clock(clk),

.q(q1)

);

sin sin(

.address(address),

.clock(clk),

.q(q2)

);

fang_bo fang_bo(

.address(address),

.clock(clk),

.q(q3)

);

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

data_out<=8‘d0;

else

begin

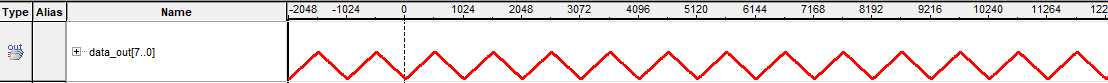

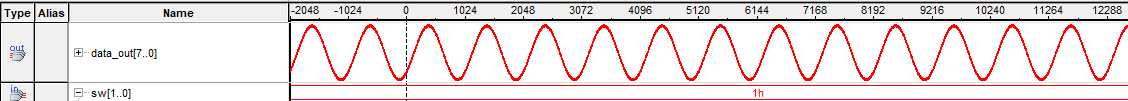

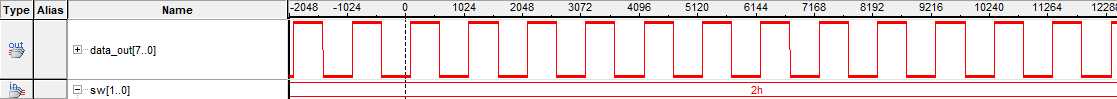

case(sw)

0:data_out<=q1;

1:data_out<=q2;

2:data_out<=q3;

default:data_out<=8‘d0;

endcase

end

end

endmodule

//顶层模块

module AD_pulse_signal_generator(

clk,

rst_n,

key_in,

sw,

data_out

);

input clk;

input rst_n;

input[1:0] key_in;

input[1:0] sw;

output[7:0] data_out;

control_freq u1(

.clk(clk),

.rst_n(rst_n),

.key_in(key_in),

.fout(fout)

);

sw_control u2(

.clk(fout),

.rst_n(rst_n),

.data_out(data_out),

.sw(sw)

);

endmodule

欢迎各位朋友批评指正~