标签:put ports mes NPU module gen 核心 play 计数

5-10 用Verilog设计一个功能类似74ls160的计数器。

(1)解题思路

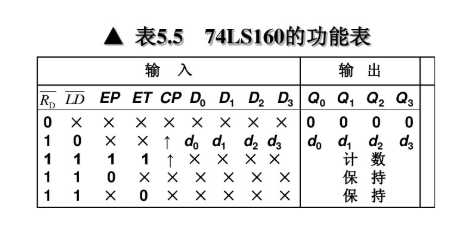

设计一个74ls160,需要知道它的功能表,以及原理图

(2)核心模块代码

module fidv1 (rd,clk,et,load,datain,dataout,cout,ep);

input rd,et,load,clk,ep;

input [3:0] datain;

output [3:0] dataout ;

output cout;

reg cout;

reg [3:0] q1;

wire rd;

always @ (posedge clk or negedge rd)

if (rd==0) begin q1<=4‘d0; end//rd=0时清零

else begin

if(clk==1&load==0) q1=datain;

else if(clk==1&load==1)

begin

if(ep==1&et==1&q1<4‘d10) //开始计数

begin q1=q1+1;cout=0;

end

else if((ep&et)==0) begin q1=q1;cout=0;end//保持不变

else if(q1==4‘d10) cout=1;//进位输出

end

end

assign dataout =q1;

endmodule

(3)测试模块代码

`timescale 1 ps/ 1 ps

module fidv1_ll();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg [3:0] datain;

reg ep;

reg et;

reg load;

reg rd;

// wires

wire cout;

wire [3:0] dataout;

// assign statements (if any)

fidv1 i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.cout(cout),

.datain(datain),

.dataout(dataout),

.ep(ep),

.et(et),

.load(load),

.rd(rd)

);

always #2 clk=~clk;

initial

begin

#0 clk=0;

#0 rd=1;

#0 datain=4‘d2;

#2 load=0;

#2 ep=1;

#0 et=1;

#12 load=1;

#16 ep=0;

#0 et=0;

#8 rd=0;

#2 rd=1;

#6 datain=4‘d3;

#5 load=0;

$display("dataout=%d,datain=%d",dataout,datain);

#2 $stop;

end

endmodule

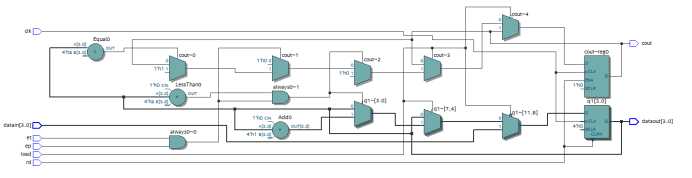

(4)RTL View的网表图

标签:put ports mes NPU module gen 核心 play 计数

原文地址:https://www.cnblogs.com/0001lizhubo/p/10846885.html