标签:情况 img reg 启用 模式 设置 9.png 梳理 参考

最近在在设计一块板子的时候发现在设计STM32电路这部分时,有些东西模棱两可。本着科学严谨的态度,本着对工作负责的态度(板子设计坏了都是money!),这里对STM32最小系统的设计进行一个梳理。如果其他人愿意将就,而我不愿意将就。

下面以STM32F407IGT6的最小系统设计为例。

124:SWDIO;

137:SWCLK。

选择SW下载模式,只需要3根线就好,DIO,GND,CLK。

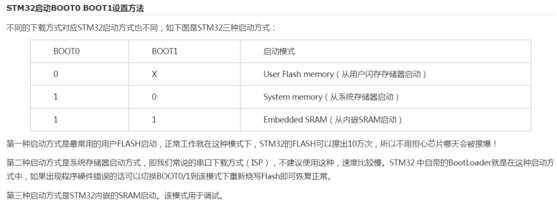

58:BOOT1;

166:BOOT0;

通常情况下是BOOT0接地,BOOT1悬空。

29:OSC_IN;

30:OSC_OUT。

当接有源晶振时,直接接OSC_IN管脚就行了,OSC_OUT管脚悬空就行。

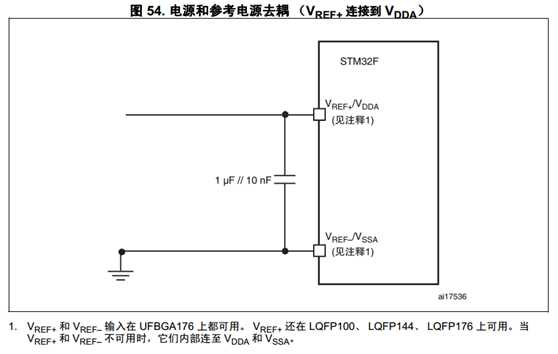

1, V_ref+与V_dda相连接

在VDDA/VREF+与VSSA/VFRE-之间并联1uF和10nF的电容。

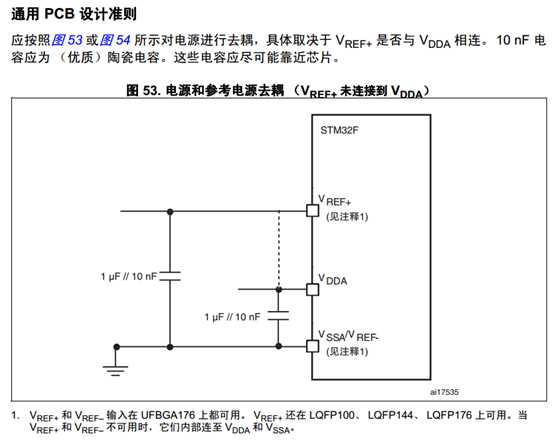

2, 2,V_ref+与V_dda不连接

需要在VREF+和VREF-之间并联1uF和10nF的电容。

需要在VDDA和VSSA之间并联1uF和10nF的电容。

见STM32F4xx中文数据手册3.18调压器

BYPASS_REG一直设置为低,启用调压器,然后VCAP_1和VCAP_2通过2.2uF的电容接地。

参考设计:BYPASS_REG接地(若有),VCAP_1和VCAP_2通过2.2uF的电容接地。

VDD和VSS之间用100nF的去耦电容相连接。

保持 PDR_ON(171)为高电平,启用电源监控器。

参考设计:PDR_ON(若有)接3V3

VSSA和VDDA之间通过100nF和10uF电容相连接。

VBAT直接接3.3V。

后续会放出我设计的最小系统电路图。

未完,待续

标签:情况 img reg 启用 模式 设置 9.png 梳理 参考

原文地址:https://www.cnblogs.com/xutopia/p/10874820.html