标签:模型 swap 字符 png 编译器 并且 http 添加 系统

SUBS PC,LR,#4 MOV R0,#0x00 LDR R0,[R1]

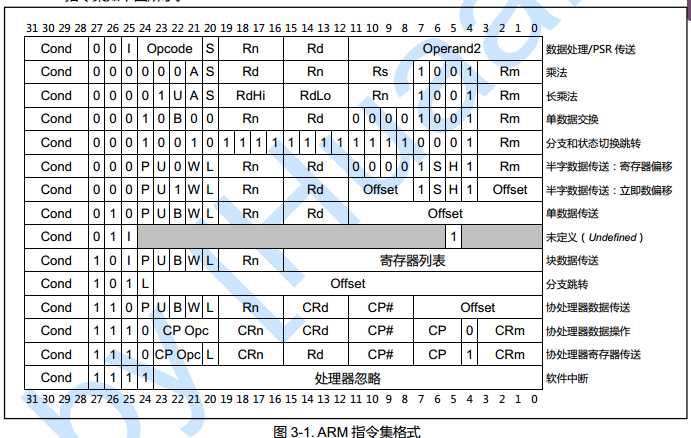

所有指令都是 32bit,load/store 体系结构(对存储器的访问只能使用加载和存储指令实现)

在 ARM 状态,所有的指令都可以按照 CPSR 状态码和指令条件字段的状态来有条件地执行。

此字段(位[31:28])确定了在什么情况下哪一个指令被执行。如果 C,N,Z 和 V 标志位的状态符合字段的条件码,将执行指令,否则忽略不执行。

有 16 种可能的条件,每种表示为在指令助记符后附加两个字符后缀。例如,一个分支(汇编语言中的 B)跳转指令变成 BEQ 为“如果相等则分支跳转”,这意味着只有 Z 标志位被置位了才会执行分支跳转。

在实际应用当中,将会使用到 15 种不同的条件:如下表所列,保留第 16 种(1111),并且一定不要使用。

使用指令条件码可实现高效的逻辑操作, 提高代码执行效率。 例如:

if(a > b) a++; CMP R0,R1 else b++; ADDHI R0,R0,#1 ADDLS R1,R1,#1

MOV R0,#0x00 <--> MOVAL R0,#0x00

机器码: MOV R0,#0x00 <------> 1110 001 1101 0 0000....000 -->0xE3A00000

数据存储指令的机器码是 1110 001,1110 是条件码,

MOV 指令的机器码是 1101

0 为 S 的机器码,0 为禁用,1 为启动

0000...000 为R0,#0x00

标签:模型 swap 字符 png 编译器 并且 http 添加 系统

原文地址:https://www.cnblogs.com/kele-dad/p/10920693.html