标签:output 允许 程序 NPU ril 功能 fpga src style

Verilog语言和软件语言不一样,有些时候理所当然的编写,也没有报语法错误,可是功能就是不对。唉,把遇到的坑都记在本篇博客吧。

1. initial begin...end里面不能有always,如果非要在里面达到always的效果,那用forever就行了。

2. reg [3:0] a=4‘d7; 这样写是对的,

wire [3:0] a=4‘d7; 这样写是错的。

3. 时序电路建议赋初始值,组合电路则不需要。

4. Verilog中不建议使用 * 和 / ,%可以偶尔使用。

5. &&、||、!是逻辑符,结果为1(真)或0(假)。

&、|、~ 是按位符,结果是化为2进制后,再按位进行比较后的结果。

6. 三目运算符是允许嵌套的,例如:assign a = (b>6) ? 1 : (b<5) ? 1 : 0 ;

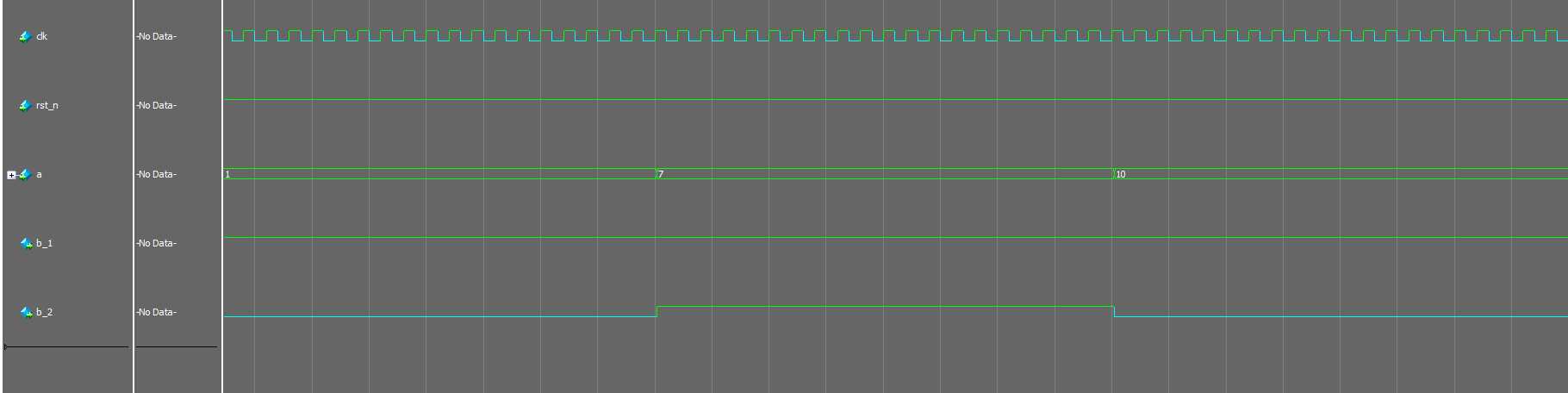

7.如果你想表达 5 < a < 9,那么你直接这样写是错的,应该写成 5 < a && a < 9 ,不信?我们看看代码和波形!

1 //====================================================================== 2 // --- 名称 : test 3 // --- 作者 : xianyu_FPGA 4 // --- 日期 : 5 // --- 描述 : 5<a<9 5<a && a<9 的区别 6 /* ----------------------------- 7 | a | 1 | 7 | 10 | 8 ----------------------------- 9 | 希望的 | 0 | 1 | 0 | 10 ----------------------------- 11 | b_1 | 1 | 1 | 1 | 12 ----------------------------- 13 | b_2 | 0 | 1 | 0 | 14 ----------------------------- 15 结论:b_2的表达方式才是对的! 16 */ 17 //====================================================================== 18 19 module test 20 //---------------------<端口声明>--------------------------------------- 21 ( 22 input clk , //时钟,50Mhz 23 input rst_n , //复位,低电平有效 24 input [3:0] a , 25 output reg b_1 , 26 output reg b_2 27 ); 28 29 //---------------------------------------------------------------------- 30 //-- 程序开始 31 //---------------------------------------------------------------------- 32 always @(*)begin 33 if(5<a<9) 34 b_1 = 1; 35 else 36 b_1 = 0; 37 end 38 39 always @(*)begin 40 if(5<a && a<9) 41 b_2 = 1; 42 else 43 b_2 = 0; 44 end 45 46 endmodule

标签:output 允许 程序 NPU ril 功能 fpga src style

原文地址:https://www.cnblogs.com/xianyufpga/p/11022625.html