标签:状态 位长 请求 校验 操作 mini2440 个数 strong bsp

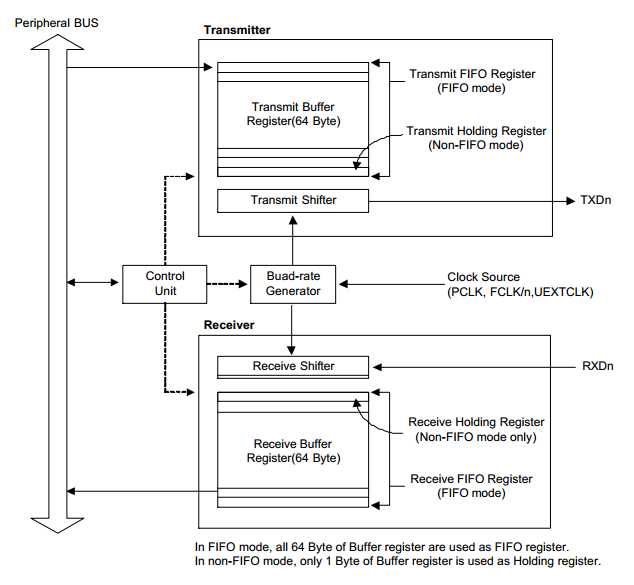

S3C2440A 的通用异步收发器(UART)配有 3 个独立异步串行 I/O(SIO)端口,每个都可以是基于中断或基

于 DMA 模式的操作。换句话说,UART 可以通过产生中断或 DMA 请求来进行 CPU 和 UART 之间的数据传输。

UART 通过使用系统时钟可以支持最高 115.2Kbps 的比特率。

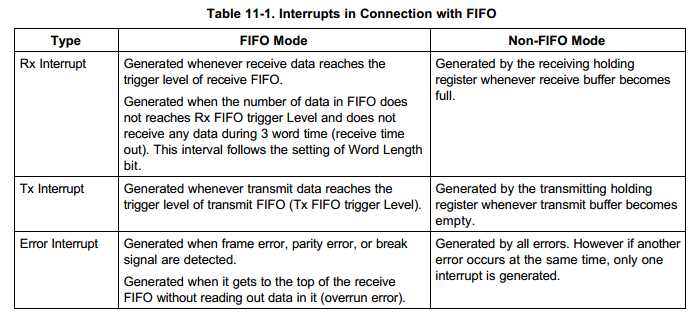

uart中断触发的时机

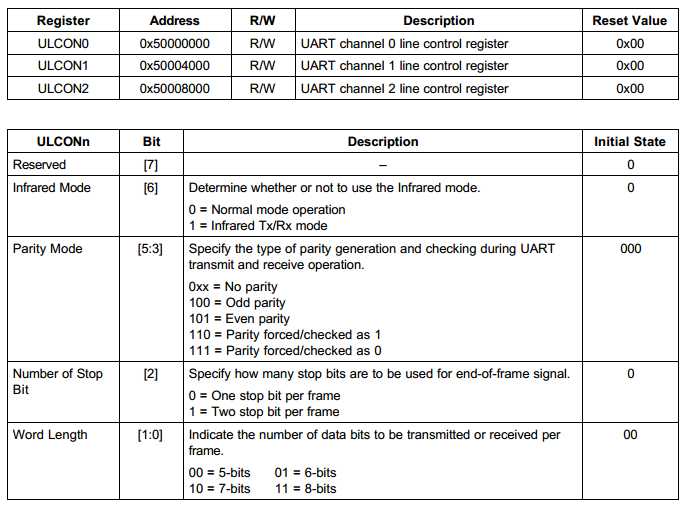

UART LINE控制寄存器ULCON,用于控制uart的奇偶校验模式选择,停止位长度,以及一次发送的数据个数设定。

UART 控制寄存器UCON,用于设定是否启用环回模式,设定中断类型的等。

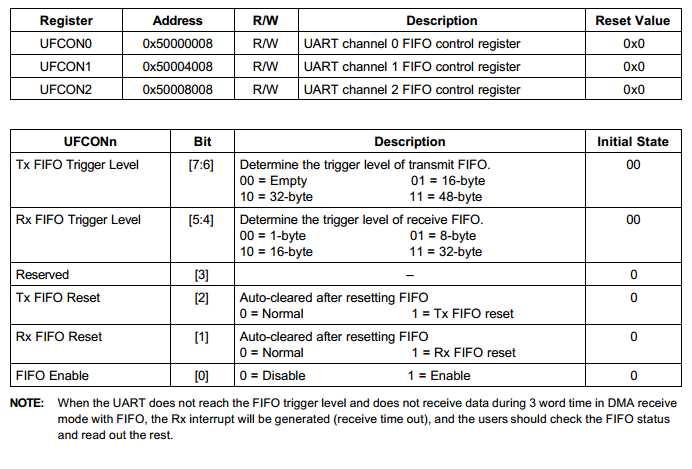

UART FIFO 控制寄存器UFCON

当 UART 未达到 FIFO 触发深度或在带 FIFO 的 DMA 接收模式中 3 字周期期间没有收到数据时,将发生 Rx

中断(接收超时),用户应该检查 FIFO 状态并读出剩余部分。

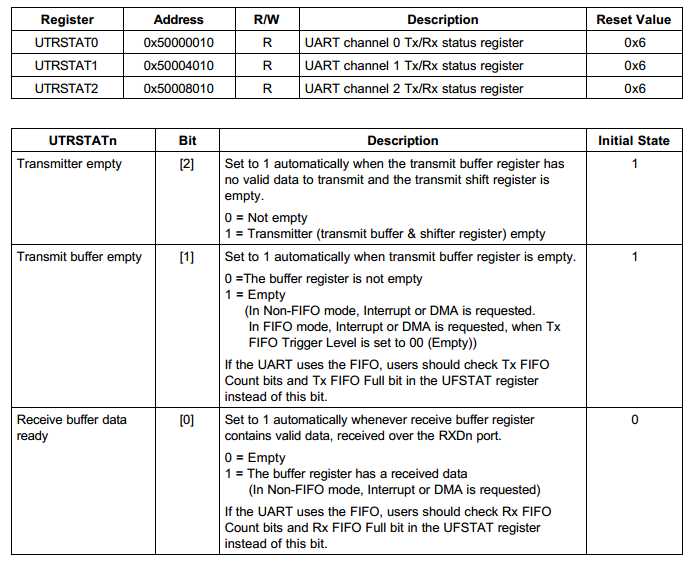

UART TX/RX 状态寄存器UTRSTAT

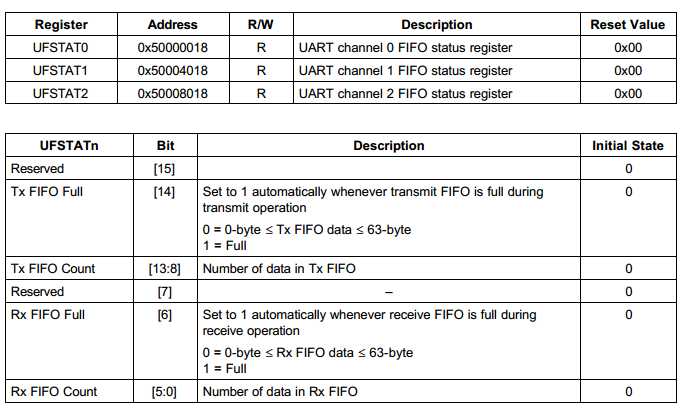

UART FIFO 状态寄存器UFSTAT

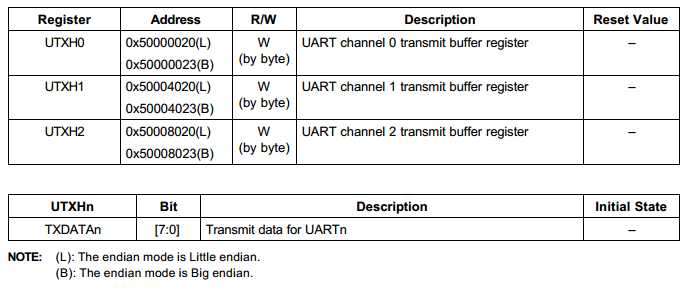

UART 发送缓冲寄存器UTXH

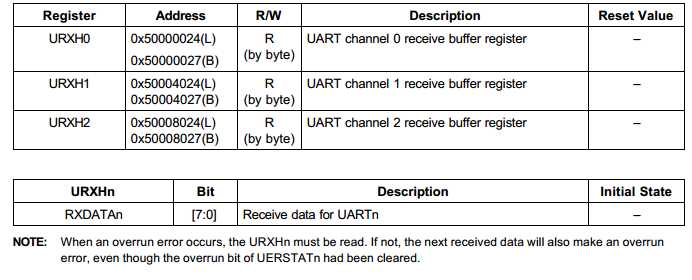

UART 接收缓冲寄存器URXH

标签:状态 位长 请求 校验 操作 mini2440 个数 strong bsp

原文地址:https://www.cnblogs.com/souroot/p/11144998.html